一种芯片供电网络电迁移分析方法、系统及存储介质

本发明涉及集成电路辅助设计领域,特别是涉及一种芯片供电网络电迁移分析方法、系统及存储介质。

背景技术:

1、随着新材料领域的发展和纳米制造工艺的改进,晶体管越来越小,按照摩尔定律的描述,集成电路的集成度以平均每隔十八个月翻一番的惊人速度发展着。超大规模集成电路(very large scale integration,vlsi)面临着越来越多的问题,其中,芯片供电网络设计遇到的难题尤为突出:芯片功率密度越来越大,供电电压降阈值越来越低,噪声容限越来越低。工业界和学术界一直在寻求更加高效准确的芯片供电网络设计方法。其中,互连线上的电迁移现象是决定供电网络可靠性的重要因素之一。

2、电迁移(electromigration,em)是指金属导线中,在电流作用下发生金属原子迁移的现象。运动中的电子和金属原子之间碰撞,发生动量交换,金属原子沿电子流方向迁移时,从阴极向阳极方向移动。这种定向原子流最终导致金属互连导线上产生空洞和晶须,最终导致供电网络发生开路或短路。电迁移空洞成核时间(tnuc)是描述电迁移现象的一项重要指标,它代表芯片供电网络由于电迁移现象首次产生空洞的时间,即当互连导线上的电迁移瞬态应力首次突破应力极限时,供电网络产生空洞的时间。

3、芯片供电网络电迁移分析的传统方法是基于统计规律的电迁移失效经验模型,如blench极限和black方程,它们广泛应用于当前eda工具的供电网络电迁移分析与评估中。但是随着新材料与纳米工艺的发展,芯片制造工艺进入7纳米以下节点后,芯片集成度越来越高,基于统计规律的片上供电网络电迁移求解算法的准确度已经无法满足高集成度芯片的设计要求,电迁移物理模型应运而生。在电迁移物理模型korhonen方程提出后,通过在真实芯片上进行测试和检验,其电迁移分析精度满足新一代eda工具的需求。使用物理模型进行电迁移分析求解已经是学术界和工业界的发展趋势。然而,korhonen方程是一个电迁移应力关于时域和空域的非齐次方程,基于物理模型korhonen方程的电迁移分析算法需要求解大量偏微分方程,寻找高效而精确的物理模型求解算法是学术界和工业界一直以来的研究热点。korhonen物理模型的求解方法主要分为数值解法和解析解法,其中数值解法主要原理是将时域、空域离散化,通过对时间迭代进行求解;解析解法采取积分变换等形式将非齐次korhonen方程转化为齐次方程,对瞬态电迁移应力进行非迭代求解。非迭代应力求解方式更具有高效性。

4、对于具有百亿级供电网络节点的超大规模集成电路来说,基于物理模型的电迁移仿真计算量非常大,这给供电网络设计的电迁移分析带来了巨大难题。同时,在铜互连线微观结构上,由于纳米制造工艺下的退火过程,金属导线会形成晶粒微观结构。晶粒微观结构具有随机性,它导致金属原子电迁移活化能具有随机性,最终使得电迁移速率具有随机性,这造成了随机的应力增长情况和空洞成核时间,给电迁移分析带来了难题。这种随机工艺要求在对供电网络的电迁移现象进行分析时,使用统计的模型和方法进行研究。面对工艺参数变化且具有随机性的片上供电网络,如何将高效的物理模型求解方法应用于随机工艺情况、如何加速物理模型求解、如何提高其电迁移分析效率是一个具有实际价值的研究课题。

技术实现思路

1、本发明的目的是提供一种芯片供电网络电迁移分析方法、系统及存储介质,能够提高芯片供电网络电迁移分析的准确性和速度。

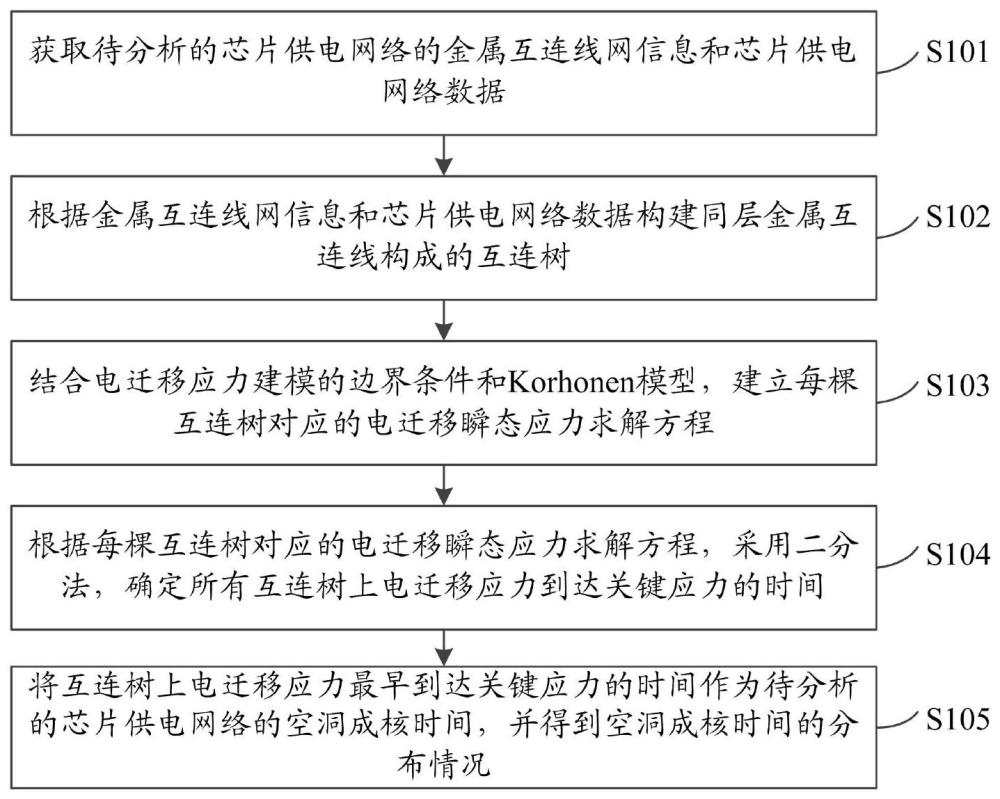

2、为实现上述目的,本发明提供了如下方案:一种芯片供电网络电迁移分析方法,包括:获取待分析的芯片供电网络的金属互连线网信息和芯片供电网络数据;所述芯片供电网络数据包括:电阻、负载电流源以及供电电压。

3、根据金属互连线网信息和芯片供电网络数据构建同层金属互连线构成的互连树。

4、结合电迁移应力建模的边界条件和korhonen模型,建立每棵互连树对应的电迁移瞬态应力求解方程。

5、根据每棵互连树对应的电迁移瞬态应力求解方程,采用二分法,确定所有互连树上电迁移应力到达关键应力的时间。

6、将互连树上电迁移应力最早到达关键应力的时间作为待分析的芯片供电网络的空洞成核时间,并得到空洞成核时间的分布情况。

7、所述结合电迁移应力建模的边界条件和korhonen模型,建立每棵互连树对应的电迁移瞬态应力求解方程,具体包括:将电迁移活化能均值下对应的扩散率作为典型扩散率取值。

8、利用典型扩散率取值对所有互连树的稳态应力分别进行计算。

9、当互连树对应的稳态应力小于应力极限时,将对应的互连树滤除。

10、在电迁移活化能均值下,计算待分析的芯片供电网络中滤除后的互连树对应的空洞成核时间。

11、根据空洞成核时间对滤除后的互连树进行排序,进而确定关键互连树。

12、对关键互连树随机工艺下的原子电迁移活化能进行蒙特卡洛按概率分布函数直接采样。

13、基于korhonen模型建立方程,对关键互连树,使用各分支随机扩散率代替各分支内部扩散率以及使用连接点的扩散率表达形式来代替连接点扩散率的方式,构建所有关键互连树的电迁移瞬态应力求解方程。

14、可选地,所述根据每棵互连树对应的电迁移瞬态应力求解方程,采用二分法,确定所有互连树上电迁移应力到达关键应力的时间,具体包括:采用openmp对多个互连树对应的电迁移瞬态应力求解方程进行并行计算。

15、可选地,所述将互连树上电迁移应力最早到达关键应力的时间作为待分析的芯片供电网络的空洞成核时间,并得到空洞成核时间的分布情况,具体包括:将互连树上电迁移应力最早到达关键应力的时间作为待分析的芯片供电网络的空洞成核时间,并将当前的空洞成核时间值进行记录。

16、直到空洞成核时间采样次数达到预设抽样次数。

17、对采样结果进行分析,绘制频率直方图。

18、根据频率直方图,确定待分析的芯片供电网络的空洞成核时间分布的均值以及方差情况。

19、一种芯片供电网络电迁移分析系统,包括:数据获取模块,用于获取待分析的芯片供电网络的金属互连线网信息和芯片供电网络数据;所述芯片供电网络数据包括:电阻、负载电流源以及供电电压。

20、互连树构建模块,用于根据金属互连线网信息和芯片供电网络数据构建同层金属互连线构成的互连树。

21、电迁移瞬态应力求解方程建立模块,用于结合电迁移应力建模的边界条件和korhonen模型,建立每棵互连树对应的电迁移瞬态应力求解方程。

22、求解模块,用于根据每棵互连树对应的电迁移瞬态应力求解方程,采用二分法,确定所有互连树上电迁移应力到达关键应力的时间。

23、空洞成核时间确定模块,用于将互连树上电迁移应力最早到达关键应力的时间作为待分析的芯片供电网络的空洞成核时间,并得到空洞成核时间的分布情况。

24、一种存储介质,其上存储有计算机程序指令,当所述计算机程序指令被处理器执行时实现所述的一种芯片供电网络电迁移分析方法。

25、根据本发明提供的具体实施例,本发明公开了以下技术效果:本发明所提供的一种芯片供电网络电迁移分析方法、系统及存储介质,结合电迁移应力建模的边界条件和korhonen模型,建立每棵互连树对应的电迁移瞬态应力求解方程;本发明基于电迁移korhonen物理模型的特征函数解析解法,考虑随机工艺参数的影响并使用统计模型进行分析,相比于普通的解析方法,本发明能够根据随机工艺情况对电迁移现象进行更符合实际生产的仿真,以便在芯片设计阶段预测供电网络使用寿命;根据每棵互连树对应的电迁移瞬态应力求解方程,采用二分法,确定所有互连树上电迁移应力到达关键应力的时间,进而能够提高芯片供电网络电迁移分析的准确性和速度。

- 还没有人留言评论。精彩留言会获得点赞!