对FPGA进行配置、回读和刷新的电路及控制方法

本发明涉及集成电路,具体涉及一种对fpga进行配置、回读和刷新的电路及控制方法。

背景技术:

1、fpga(field-programmable gate array)即现场可编程门阵列,它是和cpu、dsp并列的一种通用集成电路。fpga片内包括时序逻辑、组合逻辑、布线资源、存储器阵列、运算逻辑阵列、时钟网络、io逻辑等资源,用户通过图形化设计方式、或者硬件描述语言(hdl)的设计输入方式,可以对fpga片内的资源进行调用、进而搭建出各种数字电路。

2、用户完成fpga功能开发设计之后,需要将电路设计转换为二进制码流,码流中只包含0、1数字组合,其不同的数字组合方式,决定了fpga片内的电路结构。由于fpga的功能是由码流所决定的,所以,如果希望fpga行使预期的功能,就要先将码流传输进fpga,这一过程称作“配置”(configuration)。

3、对fpga进行配置的电路,是领域内的公知技术:其一种典型方法是jtag下载回读:从上位机,经过usb和jtag接口的下载线,通过jtag接口,将码流传输至fpga,并可进行回读比对。此方法能够实现对fpga的配置、回读,但缺点是:配置信息掉电即丢,只适用于调试,无法用于产品和设备的现场部署。另一种方法是:使用prom对fpga进行上电配置时的配置加载,其优点是prom可以对配置数据作非易失存储,并且由于工作状态下不需要上位机,所以可以部署于实际的产品中,但是其缺点是:只能对fpga进行上电配置的配置加载,无法对fpga配置进行回读、比对、刷新。

4、相关技术中,公布号为cn112433777a的专利申请文献提出了一种sram型fpga的配置数据动态刷新方法,所存在的缺陷是:仅支持spi nor flash,功能固定单一且无法实时对芯片的工作模式进行调整设置;需要生成配置文件和屏蔽文件,生成屏蔽文件需要更加复杂的设计流程且设计开发时间更长,需要的存储器空间更大,进而需要更多存储器芯片、更高的成本;另外该方案只实现了回读刷新,未记载上电初始化配置过程。公布号为cn112527350a的专利申请文献提出了一种星载sram型fpga配置与刷新控制的ip核,所存在的缺陷是:仅支持并口nor flash,功能固定单一、无法实时对芯片的工作模式进行调整设置;再者其作为一个ip而出现,对外包括apb总线、axi总线、dma接口,只能由更大的电路的子模块使用,无法作为独立工作的模块。另外,sram型fpga的配置方案中,sram阵列易受空间粒子、宇宙射线、带电粒子的影响,进而发生误翻转。

技术实现思路

1、本发明所要解决的技术问题在于如何提供一种对fpga芯片进行配置、回读和刷新的电路。

2、本发明通过以下技术手段解决上述技术问题的:

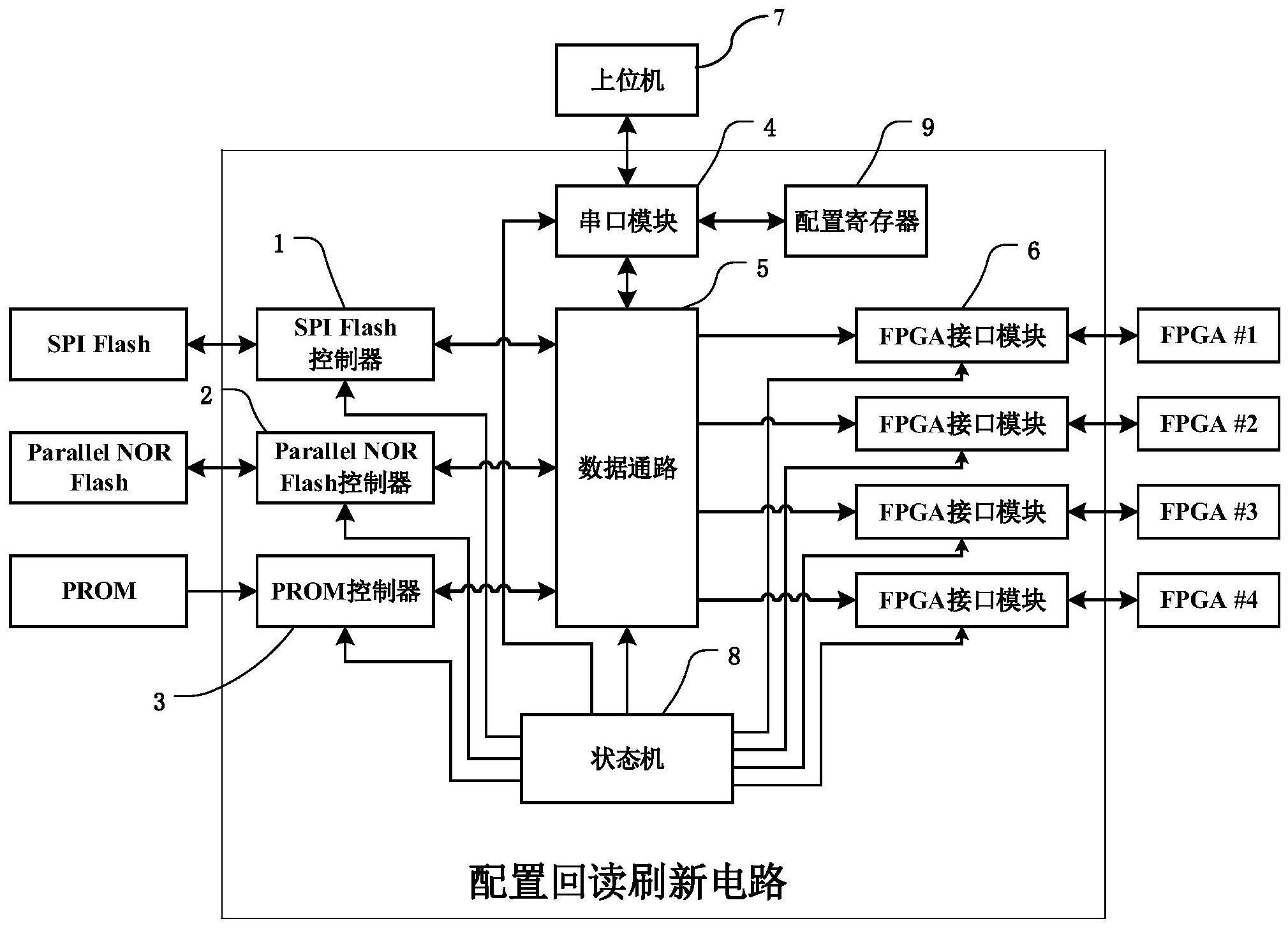

3、第一方面,本发明提出了一种对fpga进行配置、回读和刷新的电路,所述电路包括存储控制器、串口模块、数据通路、fpga接口模块以及状态机,所述存储控制器与所述fpga接口模块之间、所述存储控制器与所述串口模块之间以及所述fpga接口模块与所述串口模块之间均通过所述数据通路连接,所述状态机分别与所述存储控制器、所述串口模块、所述数据通路以及所述fpga接口模块相连接,所述存储控制器连接有存储器,所述串口模块与上位机相连接;

4、所述状态机包括:

5、信息接收模块,用于通过所述串口模块接收所述上位机发送的信息,所述信息的内容包括指令、数据以及控制信息;

6、读写控制模块,用于基于所述控制信息控制所述存储控制器对其连接的存储器进行所述数据的读写操作;

7、配置模块,用于基于所述控制信息和所述指令控制所述fpga接口模块通过所述数据通路获取所述存储器中的数据或所述串口模块发送的数据,以对所述fpga接口模块连接的fpga芯片进行配置;

8、回读模块,用于基于所述控制信息和所述指令控制所述fpga接口模块对所连接的fpga芯片进行回读,并将获取的回读数据经所述数据通路发送至所述串口模块;

9、刷新模块,用于在所述fpga接口模块将回读数据与存储器中的数据或串口模块所发送的数据进行比对进行比对出错时,所述状态机用于基于所述控制信息控制所述fpga接口模块,以使所述fpga接口模块利用所述存储器中的数据或所述串口模块发送的数据对fpga芯片的配置数据进行刷新。

10、进一步地,所述信息的内容还包括地址,所述串口模块接收所述上位机发送的信息,并将所述数据发送至与所述地址对应的所述存储器或所述fpga接口模块。

11、进一步地,所述串口模块还连接有配置寄存器,所述信息的内容还包括用于表示所述存储器的工作状态的状态信息;

12、所述串口模块用于将所述数据、所述状态信息和所述控制信息写入所述配置寄存器。

13、进一步地,所述状态机用于基于所述控制信息控制所述存储控制器,使得所述存储控制器通过所述数据通路接收所述串口模块发送的数据并写入所述存储器,或使得所述存储控制器读取存储器中的数据并通过所述数据通路发送给所述串口模块或所述fpga接口模块。

14、进一步地,所述存储控制器包括spi flash控制器、并口nor flash控制器以及prom控制器中的至少一种,所述存储器包括spi flash、nor flash以及prom中的至少一种,所述spi flash控制器与所述spi flash相连接,所述并口nor flash控制器与所述norflash相连接,所述prom控制器与所述prom相连接。

15、进一步地,所述电路还包括ecc译码模块,所述数据通路与所述fpga接口模块之间经所述ecc译码模块连接,所述ecc译码模块用于采用bch编码或汉明码或ldpc码对存储器中编码后的数据进行检错和纠错。

16、进一步地,所述fpga接口模块设置的数量为至少一个。

17、进一步地,所述电路为采用硬件描述语言实现的数字逻辑电路。

18、第二方面,本发明提出了一种如上所述的对fpga进行配置、回读和刷新的电路的控制方法,应用于上位机,所述方法包括:

19、通过所述串口模块接收所述上位机发送的信息,所述信息的内容包括指令、数据以及控制信息;

20、基于所述控制信息控制所述存储控制器对其连接的存储器进行所述数据的读写操作;

21、基于所述控制信息和所述指令控制所述fpga接口模块通过所述数据通路获取所述存储器中的数据或所述串口模块发送的数据,以对所述fpga接口模块连接的fpga芯片进行配置;

22、基于所述控制信息和所述指令控制所述fpga接口模块对所连接的fpga芯片进行回读,并将获取的回读数据经所述数据通路发送至所述串口模块;

23、在所述fpga接口模块将回读数据与存储器中的数据或串口模块所发送的数据进行比对进行比对出错时,基于所述控制信息控制所述fpga接口模块,以使所述fpga接口模块利用所述存储器中的数据或所述串口模块发送的数据对fpga芯片的配置数据进行刷新。

24、进一步地,所述串口模块还连接有配置寄存器,所述信息的内容还包括用于表示所述存储器的工作状态的状态信息;

25、所述串口模块用于将所述数据、所述状态信息和所述控制信息写入所述配置寄存器。

26、本发明的优点在于:

27、(1)本发明通过设置状态机对存储控制器、串口模块、数据通路、fpga接口模块进行控制,控制存储控制器对存储器的操作及控制fpga接口模块对fpga的配置/回读/刷新操作等,通过配置、回读、刷新操作,可以对fpga芯片内的配码错误进行检测和更新,增强了fpga芯片对恶劣环境的适应性;与jtag配置模式相比,可以在无上位机的情况下工作,能够实现现场部署,与prom配置模式相比,能够实现fpga配码的回读、比对、刷新。

28、(2)能够支持并口nor flash、spi flash、prom等多种存储器芯片类型。

29、(3)既可以上电后按照默认的预定流程工作,也可以通过串口对芯片的工作模式进行实时的调整设置,克服了传统的配置电路功能固定单一的缺点。

30、(4)配置回读刷新的电路是纯数字逻辑电路,既可以通过1颗asic单芯片实现,也可以使用cpld或另一颗fpga来实现,是一个可以独立工作的电路。

31、本发明附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

- 还没有人留言评论。精彩留言会获得点赞!