一种芯片验证方法、装置、设备及存储介质与流程

本技术涉及电子,尤其涉及一种芯片验证方法、装置、设备及存储介质。

背景技术:

1、随着集成电路理论的不断完善和系统级芯片(system on chip,soc)的出现,技术人员对芯片的功能以及设计效率有了更高的要求。随着芯片的规模越来越大,芯片验证在整个芯片研制过程的地位越来越重要。芯片验证确定为芯片研制过程中必不可少的一环,可以有效检测芯片的功能是否满足需求。其中,通用验证方法学(universal verificationmethodology,uvm)是一个验证平台开发框架,技术人员可以利用其构建具有标准化层次结构和接口的功能验证环境,uvm的出现为芯片验证提供了便利。

2、目前,在基于uvm对芯片进行验证的过程中,由于配置类型和配置参数的不确定性,仍需要技术人员反复手动配置参数,才能获得正确的指令,以对芯片进行验证。由于获取正确的指令的过程需要依靠技术人员手动配置,难以快速获得正确的命令,使得芯片验证仿真的时间较长,验证效率降低。

技术实现思路

1、本技术提供的一种芯片验证方法、装置、设备及存储介质,目的在于解决芯片验证效率低的问题。

2、为达到上述目的,本技术采用如下技术方案:

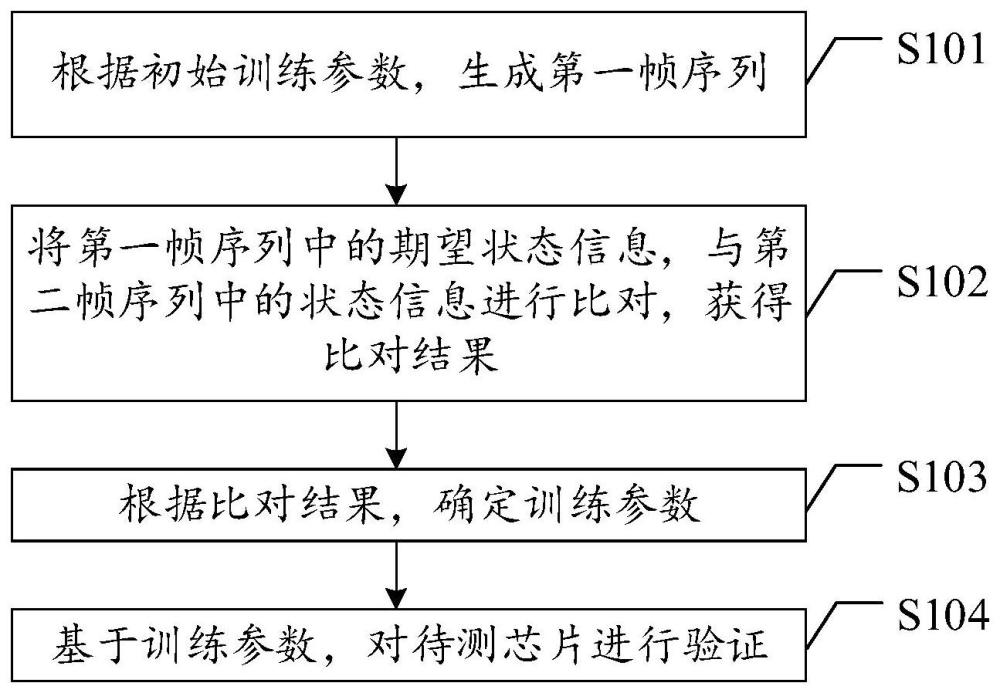

3、第一方面:本技术提供一种芯片验证方法,包括:

4、根据初始训练参数,生成第一帧序列,所述第一帧序列中包含状态配置信息与期望状态信息,所述状态配置信息,用于指示待测芯片生成第二帧序列;

5、将所述第一帧序列中的期望状态信息,与所述第二帧序列中的状态信息进行比对,获得比对结果;

6、根据所述比对结果,确定训练参数;

7、基于所述训练参数,对所述待测芯片进行验证。

8、在一种可能的实现方式中,所述比对结果为所述第一帧序列中的期望状态信息,与所述第二帧序列中的状态信息不一致,所述根据所述比对结果,确定的训练参数,包括:

9、根据所述比对结果,将所述第二帧序列中的状态信息中,与所述期望状态信息不同的状态信息确定为错误信息;

10、基于所述错误信息,对所述初始训练参数进行调节,获得调节后的参数;

11、基于所述调节后的参数,生成第三帧序列,所述第三帧序列中包含调节后的状态配置信息与调节后的期望状态信息,所述调节后的状态配置信息,用于指示待测芯片生成第四帧序列;

12、将所述第三帧序列中的调节后的期望状态信息,与所述第四帧序列中的状态信息进行比对,获得调节后的比对结果;

13、当所述调节后的比对结果为所述第三帧序列中的调节后的期望状态信息,与所述第四帧序列中的状态信息一致时,将所述调节后的参数确定为所述训练参数。

14、在一种可能的实现方式中,所述比对结果为所述第一帧序列中的期望状态信息,与所述第二帧序列中的状态信息一致,所述根据所述比对结果,确定训练参数,包括:

15、将所述初始训练参数,确定为所述训练参数。

16、在一种可能的实现方式中,所述第一帧序列中的期望状态信息包括所述第一帧序列中命令位域的信息和所述第一帧序列中状态位域的信息,所述第二帧序列中的状态信息包括所述第二帧序列中命令位域的信息和所述第二帧序列中状态位域的信息,所述将所述第一帧序列中的期望状态信息,与所述第二帧序列中的状态信息进行比对,获得比对结果,包括:

17、将所述第一帧序列中命令位域的信息,与所述第二帧序列中命令位域的信息进行比对;

18、当所述第一帧序列中命令位域的信息,与所述第二帧序列中命令位域的信息一致时,将所述第一帧序列中状态位域的信息,与所述第二帧序列中状态位域的信息进行比对,获得比对结果。

19、在一种可能的实现方式中,所述将所述第一帧序列中命令位域的信息,与所述第二帧序列中命令位域的信息进行比对之后,还包括:

20、当所述第一帧序列中命令位域的信息,与所述第二帧序列中命令位域的信息不一致时,调节所述初始训练参数。

21、在一种可能的实现方式中,所述根据初始训练参数,生成第一训练帧序列之前,还包括:

22、响应于配置指令,生成所述初始训练参数,所述配置指令中包含帧序列的类型。

23、在一种可能的实现方式中,所述帧序列的类型,包括第二空闲序列idle2,第三空闲序列idle3,分布式管理环境序列dme中的至少一种。

24、第二方面:本技术提供一种芯片验证装置,包括:

25、生成单元、比对单元、确定单元、和验证单元;

26、所述生成单元,用于根据初始训练参数,生成第一帧序列,所述第一帧序列中包含状态配置信息与期望状态信息,所述状态配置信息,用于指示待测芯片生成第二帧序列;

27、所述比对单元,用于将所述第一帧序列中的期望状态信息,与所述第二帧序列中的状态信息进行比对,获得比对结果;

28、所述确定单元,用于根据所述比对结果,确定训练参数;

29、所述验证单元,用于基于所述训练参数,对所述待测芯片进行验证。

30、在一种可能的实现方式中,所述比对结果为所述第一帧序列中的期望状态信息,与所述第二帧序列中的状态信息不一致,所述确定单元,包括:

31、第一确定子单元、第一获得单元、第一生成子单元、第一比对子单元和第二确定子单元;

32、所述第一确定子单元,用于根据所述比对结果,将所述第二帧序列中的状态信息中,与所述期望状态信息不同的状态信息确定为错误信息;

33、所述第一获得单元,用于基于所述错误信息,对所述初始训练参数进行调节,获得调节后的参数;

34、所述第一生成子单元,用于基于所述调节后的参数,生成第三帧序列,所述第三帧序列中包含调节后的状态配置信息与调节后的期望状态信息,所述调节后的状态配置信息,用于指示待测芯片生成第四帧序列;

35、所述第一比对子单元,用于将所述第三帧序列中的调节后的期望状态信息,与所述第四帧序列中的状态信息进行比对,获得调节后的比对结果;

36、所述第二确定子单元,用于当所述调节后的比对结果为所述第三帧序列中的调节后的期望状态信息,与所述第四帧序列中的状态信息一致时,将所述调节后的参数确定为所述训练参数。

37、在一种可能的实现方式中,所述比对结果为所述第一帧序列中的期望状态信息,与所述第二帧序列中的状态信息一致,所述确定单元,包括:第三确定子单元;

38、所述第三确定子单元,用于将所述初始训练参数,确定为所述训练参数。

39、在一种可能的实现方式中,所述第一帧序列中的期望状态信息包括所述第一帧序列中命令位域的信息和所述第一帧序列中状态位域的信息,所述第二帧序列中的状态信息包括所述第二帧序列中命令位域的信息和所述第二帧序列中状态位域的信息,所述获得单元,包括:第二比对子单元、第二获得单元;

40、所述第二比对子单元,用于将所述第一帧序列中命令位域的信息,与所述第二帧序列中命令位域的信息进行比对;

41、所述第二获得单元,用于当所述第一帧序列中命令位域的信息,与所述第二帧序列中命令位域的信息一致时,将所述第一帧序列中状态位域的信息,与所述第二帧序列中状态位域的信息进行比对,获得比对结果。

42、在一种可能的实现方式中,所述装置,还包括:发送单元;

43、所述发送单元,用于当所述第一帧序列中命令位域的信息,与所述第二帧序列中命令位域的信息不一致时,调节所述初始训练参数。

44、在一种可能的实现方式中,所述装置,还包括:第二生成子单元;

45、所述第二生成子单元,用于响应于配置指令,生成所述初始训练参数,所述配置指令中包含帧序列的类型。

46、在一种可能的实现方式中,所述帧序列的类型,包括第二空闲序列idle2,第三空闲序列idle3,分布式管理环境序列dme中的至少一种。

47、第三方面:本技术提供一种计算机设备,所述计算机设备包括:处理器以及存储器;

48、所述存储器用于存储程序代码,并将所述程序代码传输给所述处理器;

49、所述处理器用于根据所述程序代码中的指令执行如上所述的一种芯片验证方法的步骤。

50、第四方面:本技术提供一种计算机可读存储介质,所述计算机可读存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现如上所述的一种芯片验证方法的步骤。

51、相较于现有技术,本技术具有以下有益效果:

52、本技术提供一种芯片验证方法、装置、设备及存储介质,通过根据初始训练参数,生成第一帧序列,所述第一帧序列中包含状态配置信息与期望状态信息,所述状态配置信息,用于指示待测芯片生成第二帧序列;将所述第一帧序列中的期望状态信息,与所述第二帧序列中的状态信息进行比对,获得比对结果;根据所述比对结果,确定训练参数;基于所述训练参数,对所述待测芯片进行验证。本技术中训练参数可以通过比对结果来确定,无需人为手动进行配置,可以快速确定训练参数,缩短验证仿真时间,有效提高芯片验证的效率。

- 还没有人留言评论。精彩留言会获得点赞!