基于TMSC6678平台的实时信号处理架构设计方法与流程

本发明属于雷达信号处理,具体为基于tmsc6678平台的实时信号处理架构设计方法。

背景技术:

1、雷达信号处理系统具有高浮点计算密度、高并行和算法集中的特点,现有主流的并行处理方案硬件一般采用dsp+fpga等嵌入式平台;一般而言,fpga平台完成脉冲压缩、距离走动校正和相参积累等信号处理流程,dsp完成目标检测、数量估计、目标航迹跟踪等数据处理流程。

2、还有一部分主流处理方案采用gpu做信号采集和信号处理的相关工作,该方案应用gpu的cuda库,在gpu中完成并行信号处理和数据处理等工作;同时,也存在一部分方案采用基于fpga+arm架构的嵌入式平台,完成信号处理流程,其fpga完成ad信号采集和数字下变频等工作,arm完成脉冲压缩、相参积累、检测和聚类跟踪等工作。

3、对于上述采用gpu平台进行并行处理的方案,虽然其运行效率高,但也存在着依赖cuda库和价格昂贵的缺点。而对于采用fpga+arm的信号处理方案,arm是通用型cpu,其没有针对雷达信号处理流程相关运算模块的优化,因此在实时运算上存在考验。总的来说,采用dsp+fpga等嵌入式平台完成雷达信号处理过程,相对于gpu平台而言,虽然运算效率相对较低,但同时也具有成本相对较低、软件平台成熟且方便移植的优势;相对于fpga+arm方案,dsp可专门针对雷达信号处理流程相关运算模块进行优化,因此在成本相差不大的情况下,运算效率可得到极大提高。

4、不过,即使在确定现有主流dsp+fpga的嵌入式平台架构下,雷达信号处理的可靠性,算法修改周期长、效率低的难题仍然未能得到很好解决,并且对于外场测试环境,难以更新程序,导致调试过程困难;这些问题亟需得到解决,本领域技术人员对此开始研究新的架构设计及应用方法,以发挥出dsp+fpga嵌入式平台最大优势,改善雷达信号实时处理的效果。

技术实现思路

1、针对背景技术中的现状,本发明提供一种新的设计方法,采用主流的dsp+fpga并行处理平台,完成雷达实时信号处理的流程;本发明尤其考虑了外场测试环境,支持网络传输rd域数据,还能通过上位机的控制实现dsp和fpga重新建链。因此,本发明保证了雷达信号处理模块的可靠性,解决了外场调试困难、算法修改周期长、效率低的难题。

2、本发明采用了以下技术方案来实现目的:

3、一种基于tmsc6678平台的实时信号处理架构设计方法,tmsc6678平台作为雷达系统的信号处理模块,在雷达系统中26ms算法运行时间和50hz数据刷新率的要求下,完成rd域数据幅值求取、目标cfar检测、目标角度求取、目标聚类、目标跟踪和滤波操作;

4、在tmsc6678平台中,dsp通过srio接口获取fpga经过相参积累后的rd域数据,并对rd域数据进行区域划分;随后应用tmsc6678平台的多核处理器,以多核并行方式求取rd域数据的幅值,再以多核协作方式并行完成目标cfar检测,最后通过多核处理器的核0进行目标聚类与目标跟踪操作,将得到的结果数据上传至上位机;

5、上位机在连接tmsc6678平台的情况下,完成对平台算法的编辑修改与控制执行,并接受rd域数据、结果数据的关键帧回传,完成雷达信号实时处理过程;同时,上位机实时判断与dsp及fpga的建链情况,并在建链异常时执行重新建链操作。

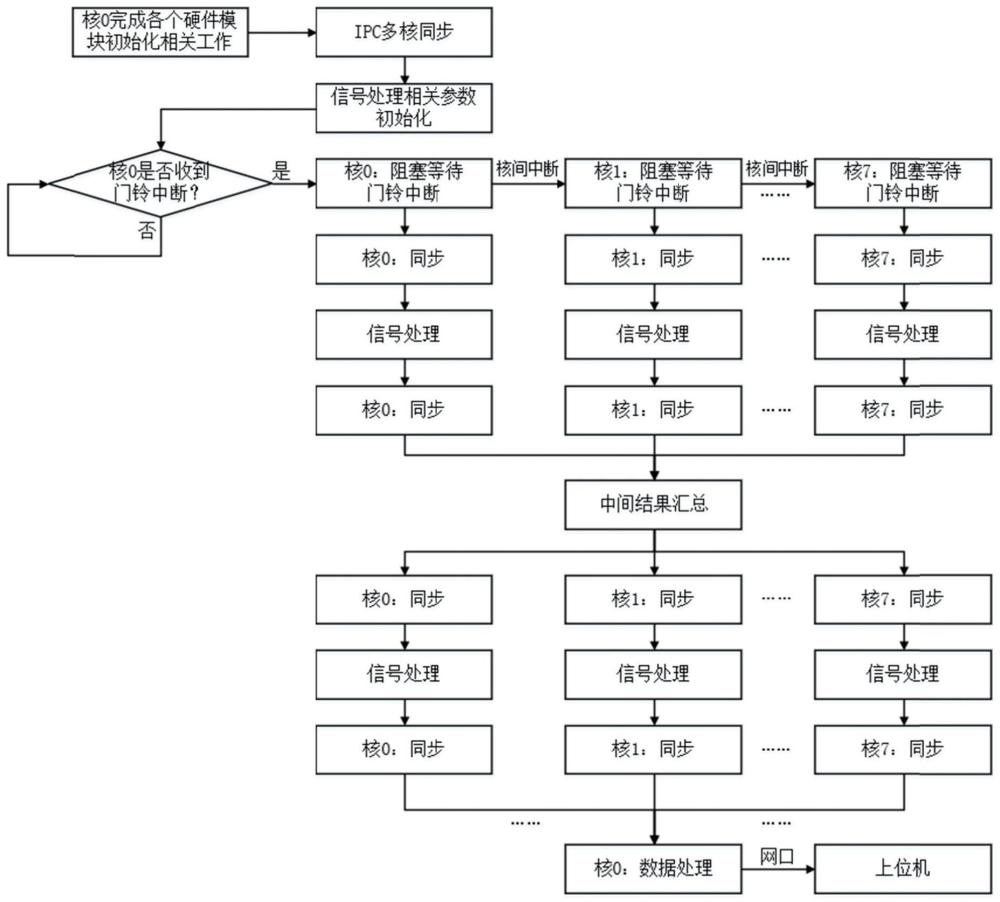

6、进一步的,在tmsc6678平台的多核处理器中,核0对dsp中串口、spi接口、网口和srio接口的驱动模块进行初始化操作;在初始化操作时,多核处理器中核0以外的其余核心进入ipc多核同步模块,等待核0完成初始化操作;

7、当所有核心完成多核同步后,核0对雷达信号处理算法的相关参数进行初始化赋值操作,并申请中间变量及结果数据对应的静态内存空间;随后,所有核心进入阻塞状态,等待雷达系统中其余模块的中断信息。

8、进一步的,fpga先完成ad中频信号采集、数字下变频、脉冲压缩和相参积累操作后,得到rd域数据,并同时从dsp各接口获取雷达系统伺服转速和方位角信息;fpga通过srio接口将完整数据包传输给dsp,传输完成后向核0发出门铃中断;

9、核0收到门铃中断后,释放信号量并向核1发送ipc中断信号,随后进入ipc多核同步模块;核1在收到ipc中断信号后,同样释放信号量,并向下个核心发送ipc中断信号,随后进入ipc多核同步模块,以此类推执行至多核处理器中最后1个核心;进入ipc多核同步模块的核心均持续等待,直至所有核心均进入后,才开始执行雷达信号实时处理操作;每个核心在完成自身负责的信号处理内容后,均持续等待其余核心完成各自的信号处理内容。

10、进一步的,所有核心在ipc多核同步模块中均完成自身当前步负责的信号处理内容后,同步汇总当前步信号处理结果,并将其中的中间结果分解为多个独立的输入,留给对应核心进行下一步的信号处理;

11、当信号处理的所有步均完成后,得到的最终信号处理结果通过共享空间留至核0,核0完成聚类、跟踪和滤波操作,随后通过dsp网口将最终信号处理结果及相关数据传输至上位机中;

12、在以tmsc6678平台为信号处理模块的架构设计中,信号处理模块上同时提供具有3种模式的上位机算法修改接口,3种模式分别为:

13、正常工作模式:执行信号处理模块的正常数据交互过程;

14、rd域传输模式:仅传输fpga上传的rd域数据;

15、关键帧模式:仅提供目标以及目标中心单元处的rd域信息。

16、进一步的,在以tmsc6678平台作为信号处理模块的信号处理过程中,fpga向dsp的pingpongbuffer轮询发送数据;当fpga向pingbuffer发送数据时,pongbuffer的数据进行并行信号处理;同理当fpga向pongbuffer发送数据时,pingbuffer的数据进行并行信号处理;并行信号处理流程包括rd域数据幅值求取、目标cfar检测和目标角度求取。

17、进一步的,上位机通过设定数据格式与算法修改内容表的方式,对平台算法进行编辑修改与控制执行;上位机向tmsc6678平台的dsp下发算法参数后,dsp修改对应参数,并将修改参数回传至上位机,上位机显示回传结果;当dsp和fpga的srio接口掉链时,上位机下发重新建链指令,使dsp和fpga的srio重新建链,具体过程如下:

18、判断dsp的srio接口初始化是否成功,同时检测其链接状态是否为x4,以及fpga是否返回建链成功标志;如果判断中的任1项未能满足,则控制dsp重新复位srio,初始化srio接口,向fpga发送建链请求;持续进行判断,若3项均满足,则表明重新建链成功,销毁dsp中断资源,重新申请srio中断的相关资源。

19、综上所述,由于采用了本技术方案,本发明的有益效果如下:

20、1、本发明方法中对多核区域进行划分,并行cfar检测,通过将rd域划分给多个检测区域,每个核心负责其中一个区域的检测,最后将结果汇总;这一分治思想顺利提高了算法运行效率;

21、2、本发明方法的信号处理流程中,多核并行edma搬运,以及多核pingpongbuffer设计,在多核同时进行dma的搬运过程中,释放了cpu资源,节省了搬运时间,相应的也提高了算法运行效率;

22、3、本发明的多核同步流程设计中,通过核间中断机制,触发核间中断释放其同步相关信号量,从而达到信号处理流程同步的目的;

23、4、本发明方法在上位机和dsp之间,通过相关协议内容,使系统能够支持rd域数据以及关键帧数据的上传;系统也支持上位机对dsp信号处理算法相关参数修改,以及fpga和dsp的重新建链。

- 还没有人留言评论。精彩留言会获得点赞!