FPGA的电路设计方法、ASIC原型验证方法及设计装置与流程

本技术涉及asic原型验证领域,尤其涉及一种fpga的电路设计方法、asic原型验证方法及设计装置。

背景技术:

1、在asic实现中,通常需要通过fpga进行原型验证。asic设计比fpga设计要大得多,通常在多个fpga上划分为多个分区。被划分到不同fpga的功能模块,可能需要共同的寄存器列表进行控制,从而需要对控制寄存器进行划分。

2、现有技术对fpga的gpio资源要求过高,同时控制寄存器的拆分复杂度高。

技术实现思路

1、鉴于此,本技术实施例提供了一种fpga的电路设计方法、asic原型验证方法及设计装置,以消除或改善现有技术中存在的一个或更多个缺陷。

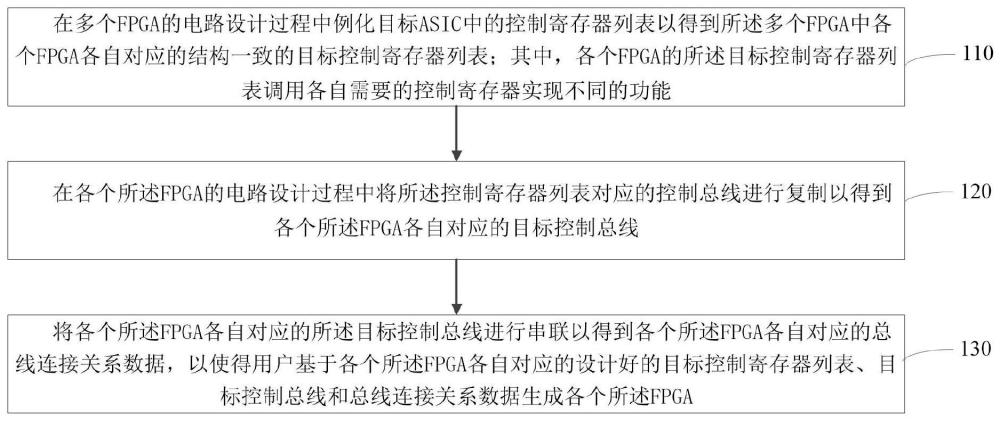

2、本技术的第一个方面提供了一种fpga的电路设计方法,该方法包括:

3、在多个fpga的电路设计过程中例化目标asic中的控制寄存器列表以得到所述多个fpga中各个fpga各自对应的结构一致的目标控制寄存器列表;其中,各个fpga的所述目标控制寄存器列表调用各自需要的控制寄存器实现不同的功能;

4、在各个所述fpga的电路设计过程中将所述控制寄存器列表对应的控制总线进行复制以得到各个所述fpga各自对应的目标控制总线;

5、将各个所述fpga各自对应的所述目标控制总线进行串联以得到各个所述fpga各自对应的总线连接关系数据,以使得用户基于各个所述fpga各自对应的设计好的目标控制寄存器列表、目标控制总线和总线连接关系数据生成各个所述fpga。

6、在本技术的一些实施例中,在所述在多个fpga的电路设计过程中例化目标asic中的控制寄存器列表以得到所述多个fpga中各个fpga各自对应的结构一致的目标控制寄存器列表之后,还包括:

7、将各个所述目标控制寄存器列表中除对应只读功能模块的目标控制寄存器列表外的其他目标控制寄存器列表中的只读寄存器都置零。

8、在本技术的一些实施例中,所述在各个所述fpga的电路设计过程中将所述控制寄存器列表对应的控制总线进行复制以得到各个所述fpga各自对应的目标控制总线,包括:

9、在各个所述fpga的电路设计过程中采用各个所述fpga各自对应的总线同步模块将所述控制总线进行复制以得到各自对应的目标控制总线;

10、所述目标控制总线包括第一控制总线和第二控制总线;

11、其中,各个所述fpga中的终点fpga的目标控制总线不包括所述第二控制总线;各个所述fpga中的起点fpga中的目标控制总线还包括对所述控制总线进行复制得到的第三控制总线。

12、在本技术的一些实施例中,所述将各个所述fpga各自对应的所述目标控制总线进行串联以得到各个所述fpga各自对应的总线连接关系数据,包括:

13、将各个所述第一控制总线与各自对应的总线同步模块和本地的目标控制寄存器列表进行连接,以及将各个所述第二控制总线与各自对应的总线同步模块和下一级fpga的总线同步模块进行连接;将所述第三控制总线与对应的总线同步模块和所述目标asic的各个功能模块进行连接,以得到各个所述fpga各自对应的总线连接关系数据。

14、本技术的第二个方面提供了一种fpga的电路设计装置,该装置包括:

15、控制寄存器列表例化模块,用于在多个fpga的电路设计过程中例化目标asic中的控制寄存器列表以得到所述多个fpga中各个fpga各自对应的结构一致的目标控制寄存器列表;其中,各个fpga的所述目标控制寄存器列表调用各自需要的控制寄存器实现不同的功能;

16、控制总线复制模块,用于在各个所述fpga的电路设计过程中将所述控制寄存器列表对应的控制总线进行复制以得到各个所述fpga各自对应的目标控制总线;

17、控制总线串联模块,用于将各个所述fpga各自对应的所述目标控制总线进行串联以得到各个所述fpga各自对应的总线连接关系数据,以使得用户基于各个所述fpga各自对应的设计好的目标控制寄存器列表、目标控制总线和总线连接关系数据生成各个所述fpga。

18、本技术的第三个方面还提供了一种基于fpga的asic原型验证方法,该方法包括:

19、生成目标控制指令;

20、将所述目标控制指令发送至各个由权利要求1-4任一项所述的fpga的电路设计方法生成的fpga各自对应的总线同步模块,以使各个所述总线同步模块在各自对应的本地目标控制寄存器列表中进行相应的读取或更新。

21、在本技术的一些实施例中,在所述目标控制指令为只读指令时,所述以使各个所述总线同步模块在各自对应的本地目标控制寄存器列表中进行相应的读取或更新,包括:

22、各个所述总线同步模块依次基于接收到的只读指令,将各自接收到的目标读取数据,与从本地的目标控制寄存器列表中的只写寄存器基于所述只读指令读取的读取数据进行或运算,以更新所述目标读取数据,并将更新后的目标读取数据和所述只读指令传入各自对应的下一级fpga中的总线同步模块。

23、在本技术的一些实施例中,在所述目标控制指令为只写指令时,所述以使各个所述总线同步模块在各自对应的本地目标控制寄存器列表中进行相应的读取或更新,包括:

24、各个所述总线同步模块依次基于接收到的只写指令,将各自接收到的目标写入数据写入本地的目标控制寄存器列表中的只写寄存器,并将所述目标写入数据和只写指令传入各自对应的下一级fpga中的总线同步模块。

25、本技术的第四个方面提供了一种电子设备,包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,所述处理器执行所述计算机程序时实现前述的第一方面所述的fpga的电路设计方法,或者实现前述的第三方面所述的基于fpga的asic原型验证方法。

26、本技术的第五个方面提供了一种计算机可读存储介质,其上存储有计算机程序,该计算机程序被处理器执行时实现前述的第一方面所述的fpga的电路设计方法,或者实现前述的第三方面所述的基于fpga的asic原型验证方法。

27、本技术提供一种fpga的电路设计方法、asic原型验证方法及设计装置,所述方法包括:在多个fpga的电路设计过程中例化目标asic中的控制寄存器列表以得到所述多个fpga中各个fpga各自对应的结构一致的目标控制寄存器列表;在各个所述fpga的电路设计过程中将所述控制寄存器列表对应的控制总线进行复制以得到各个所述fpga各自对应的目标控制总线;将各个所述fpga各自对应的所述目标控制总线进行串联以得到各个所述fpga各自对应的总线连接关系数据,以使得用户基于各个所述fpga各自对应的设计好的目标控制寄存器列表、目标控制总线和总线连接关系数据生成各个所述fpga。本技术能够有效降低控制寄存器列表划分的复杂度,进而有效地对asic进行原型验证。

28、本技术的附加优点、目的,以及特征将在下面的描述中将部分地加以阐述,且将对于本领域普通技术人员在研究下文后部分地变得明显,或者可以根据本技术的实践而获知。本技术的目的和其它优点可以通过在说明书以及附图中具体指出的结构实现到并获得。

29、本领域技术人员将会理解的是,能够用本技术实现的目的和优点不限于以上具体所述,并且根据以下详细说明将更清楚地理解本技术能够实现的上述和其他目的。

- 还没有人留言评论。精彩留言会获得点赞!