向量处理器、神经网络加速器、芯片及电子设备的制作方法

本发明涉及神经网络,尤其涉及一种向量处理器、加速器、芯片及电子设备。

背景技术:

1、深度神经网络(deep neural network,dnn)是一种基于人工神经网络架构的机器学习方法,人工神经网络(artificial neural networks,ann)使用相互连接的节点(称为神经元)的层来处理和学习输入数据。深度神经网络是具有多个层的人工神经网络,这些层位于输入层和输出层之间。神经网络总是由相同的组件组成:神经元、突触、权重、偏差和函数,在实际应用中,这些组件通常被称作算子。常见的算子有:卷积、池化、上/下采样、激活函数、元素操作(元素加、元素减、元素乘、元素除)等。深度学习使用多个层来表示数据的不同层次的抽象,从而提高模型的准确性和泛化能力,已经广泛应用于运算机视觉、语音识别、自然语言处理、机器翻译、生物信息学、药物设计、医学图像分析等领域,产生了与人类专家水平相当甚至超越的结果。

2、随着数据量不断地累积,以神经网络为主题的人工智能技术得到越来越广泛的应用。尽管神经网络已经被证明能够成功解决自动驾驶、人脸识别等实际问题,但由于传统硬件平台运算性能的局限性,使得神经网络在传统硬件难以高效部署。因此,需要专门为神经网络算法设计定制的硬件平台,这中硬件平台被称为神经网络加速器,其核心通常是一组专用的集成电路芯片,这种芯片被称为神经网络加速器芯片。

3、在神经网络中,图像的缩小和放大是必不可少的功能,一般图像放大通过上采样实现,可以使用双线性插值、最近邻插值等算法;图像缩小通过下采样、池化实现,可以使用最近邻插值、双线性插值、最大池化、平均池化等算法。现有神经网络加速器中,受限于面积成本、性能和功耗的考虑,神经网络加速器芯片通常需要在维持性能的情况下降低面积。

技术实现思路

1、本发明的目的在于提供一种向量处理器、神经网络加速器、芯片及电子设备,以至少解决上述技术问题。本发明提供的诸多技术方案中的优选技术方案所能产生的诸多技术效果详见下文阐述。

2、为实现上述目的,本发明提供了以下技术方案:

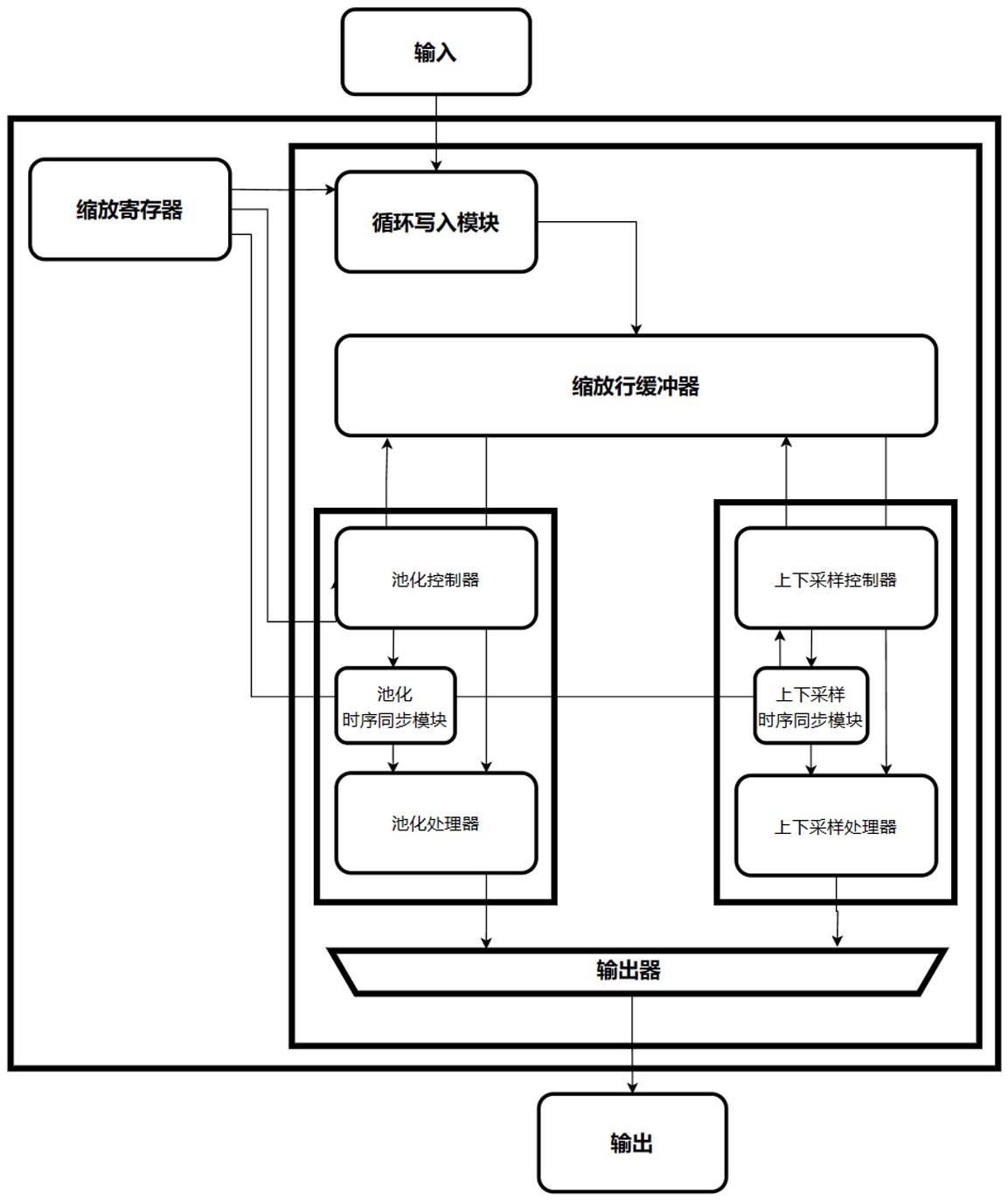

3、本发明提供的一种向量处理器,包括:池化处理模块、上下采样模块和缩放行缓冲器,所述池化处理模块及上下采样模块均与所述缩放行缓冲器连接且共用所述缩放行缓冲器;所述池化处理模块通过池化算法对图像进行缩小,所述上下采样模块通过上采样算法对图像进行放大,下采样算法对图像进行缩小;根据输入特征图的地址信号、控制信号,所述缩放行缓冲器将所述输入特征图的特征图数据送入对应的行存储器,并发送所述缩放行缓冲器的状态信息至所述池化处理模块或上下采样模块。

4、可选地,所述向量处理器还包括与所述缩放行缓冲器连接的循环写入模块;所述循环写入模块接收所述特征图数据,产生所述特征图数据的地址信号和控制信号,并将所述特征图数据、地址信号、控制信号输入所述缩放行缓冲器。

5、可选地,所述池化处理模块包括相互连接的池化控制器、池化处理器;所述池化控制器根据不同的池化内核大小输出至少一个有效地址到所述缩放行缓冲器,并在每个所述池化内核开始和结束时分别输出开始脉冲信号、结束脉冲信号;基于所述开始脉冲信号、结束脉冲信号,所述池化处理器进行所述特征图数据的池化运算。

6、可选地,所述池化处理模块还包括池化时序同步模块,所述池化时序同步模块与所述池化控制器、池化处理器连接,基于所述开始脉冲信号、结束脉冲信号进行时序同步。

7、可选地,所述池化控制器还用于判断所述缩放行缓冲器是否满足池化算法的执行条件,所述池化算法的执行条件为:所述缩放行缓冲器中累积的行数大于或等于所述池化内核的高度。

8、可选地,所述上下采样模块包括相互连接的上下采样控制器、上下采样处理器;所述上下采样控制器用于从所述缩放行缓冲器中读出所述特征图数据的地址、及上下采样运算所需要的参数;所述上下采样处理器用于进行所述特征图数据的上采样运算、下采样运算。

9、可选地,所述上下采样控制器采用最近邻工作模式或双线性工作模式;在所述最近邻工作模式中,所述上下采样控制器每次输出一路特征图数据的有效地址到所述缩放行缓冲器,所述缩放行缓冲器每次输出一路特征图数据到所述上下采样处理器,所述上下采样处理器计算后进行结果输出;在所述双线性工作模式中,所述上下采样控制器每次输出特征图数据的四路有效地址到缩放行缓冲器,所述四路有效地址与四个缩放参数经过上下采样时序同步模块同步后传输至所述上下采样处理器,所述上下采样处理器对所述特征图数据、缩放参数依次乘加运算进行结果输出。

10、可选地,所述上下采样控制器还用于判断所述缩放行缓冲器是否满足上采样算法或下采样算法的执行条件,所述上采样算法、下采样算法的执行条件为:所述缩放行缓冲器中累积的行数大于或等于两行。

11、可选地,所述向量处理器还包括缩放寄存器,所述缩放寄存器与所述循环写入模块、池化处理模块、上下采样模块均进行连接;所述缩放寄存器用于选择池化处理模块、上下采样模块,或配置图像放大或缩小的比例。

12、可选地,所述向量处理器还包括顶层控制模块,所述顶层控制模块对所述池化处理模块、上下采样模块的计算过程进行控制。

13、可选地,所述顶层控制模块通过状态机对所述池化处理模块、上下采样处理模块的工作过程进行控制;所述状态机对所述池化处理模块的控制过程为:所述向量处理器上电,所述状态机处于空闲状态;所述顶层控制模块发送启动信号,所述状态机进入数据等待状态;当缩放行缓冲器累积预定量的数据,所述状态机进入到计算状态;在所述状态机处于所述计算状态时;当一行计算结束且未完成所有行的计算时,状态机进入所述数据等待状态;当一行计算结束且需要等待最后一个像素完成计算时,所述状态机进入计算等待状态,并在池化计算完成后进入所述数据等待状态;当所有计算完成时,状态机进入到结束状态;所述状态机对所述上下采样处理模块的控制过程为: 所述向量处理器上电,所述状态机处于空闲状态;所述顶层控制模块发送启动信号,所述状态机进入数据等待状态;当所述缩放行缓冲器累积预定量的数据,所述状态机跳转到计算状态;当一行计算结束后,状态机跳转到换行状态;在所述状态机处于所述换行状态时;当输入数据不够多算一行时,状态机进入所述数据等待状态;当输入数据量足够多算一行时,所述状态机进入述计算状态;当输出所有行计算结束时,所述状态机进入结束状态。

14、一种神经网络加速器,包括以上任一项所述的一种向量处理器。

15、一种芯片,包括以上所述的一种神经网络加速器。

16、一种电子设备,包括以上所述的一种芯片。

17、实施本发明上述技术方案中的一个技术方案,具有如下优点或有益效果:

18、本发明的池化处理模块对图像进行缩小,上下采样模块对图像进行放大或缩小,且池化处理模块及上下采样模块共用缩放行缓冲器,在维持向量处理器及包含有向量处理器的芯片的原有处理性能前提下,相较于传统向量处理器,在保持电路性能不变时,通过缩放行缓冲器节省了一定的行缓冲器的面积,从而减少向量处理器对应的面积,进而可以减少包含有向量处理器的芯片的面积,且可以降低向量处理器和包含有向量处理器的芯片的成本和功耗。

- 还没有人留言评论。精彩留言会获得点赞!