I2C接口规避错误起始和停止条件的电路结构及方法与流程

本发明涉及i2c(inter-integrated circuit,集成电路总线)总线,尤其涉及一种i2c接口规避错误起始条件和停止条件的电路结构及方法。

背景技术:

1、近年来,随着集成电路行业高速发展,芯片的集成度越来越高。几乎所有的消费电子、通信电子系统都集成有:智能控制电路(比如mcu)、通用电路(比如lcd驱动器、i/o口、ram、eeprom或数据转换器)、面向应用电路(比如数字调谐或信号处理电路、音频拨号电话的dtmf发生器)。为了使硬件效益最大、电路最简单化,philips公司开发了一个简单、开放的双向两线i2c总线,包括数据线sda和时钟线scl,来实现有效的器件控制。所有符合i2c总线的器件组合了一个片上接口,使器件之间直接通过i2c总线通信,这使得ic(integratedcircuit,集成电路)可以很容易形成模块化和标准化,便于重复利用。

2、i2c总线解决了很多在设计数字控制电路时遇到的接口问题,极大地简化了硬件电路和pcb布线,降低了系统成本,提高了系统的可靠性。i2c总线是一个真正的多主机总线,多个主机初始化数据传输的时候,可以通过冲突检测和仲裁防止数据破坏,任何设备都可以作为主机或者从机,但同一时刻只有一个主机,这使得i2c总线非常灵活,总线上的电路增加和删除不会影响别的单元工作。i2c总线可以通过外部连线进行在线监测,便于系统调试和故障诊断,有利于模块化和标准化软件,极大地缩短了研发周期;总线上挂载的i2c设备数目由总线的最大电容决定且具有极低的电流消耗。

3、i2c总线的sda数据线和scl时钟线都是双向线路,通过一个电流源或上拉电阻连接到正的电源电压,当总线空闲时这两条线路都是高电平,当scl线为高电平时sda线由高电平向低电平切换表示起始条件。当scl线为高电平时sda线由低电平向高电平切换表示停止条件。总线在起始条件后被认为处于忙的状态,然后就可以开始传输数据位、响应位、停止位。在停止条件的某段时间后总线被认为再次处于空闲状态,如果产生重复起始条件而不产生停止条件总线会一直处于忙的状态。如图1所示为i2c总线起始条件和停止条件检测时序图。其中,左侧虚线框为停止条件检测时序图,右侧为起始条件检测时序图,scl上升沿到sda边沿为setup时间,即协议规定的建立时间,sda边沿到scl下降沿为hold时间,即协议规定的保持时间,主机需要保证总线时序是满足协议规定的建立时间和保持时间要求的。起始条件和停止条件检测严重影响数据传输正确性,因此在设计中涉及到i2c总线时,起始条件和停止条件检测一直是着重要考虑的部分。

4、实际应用中,受工作环境和电路本身延迟的影响,i2c的时钟信号和数据信号会发生抖动,产生毛刺,时钟信号和数据信号的时序发生错位、起始条件或停止条件的建立时间、保持时间不符合i2c协议规定,这些情况都可能会导致设备检测到错误的起始条件或停止条件。而现有技术中,还没有针对各种导致设备检测到错误的起始条件或停止条件的通用解决方案,比如中国专利cn112540943b中,通过过滤毛刺的方法解决了起始条件检错错误的问题,但是没有给出其它情况下检测到错误的起始条件和停止条件的解决办法。

技术实现思路

1、本发明要解决的技术问题在于,针对现有技术中i2c接口可能出现的各种起始条件和错误条件检测错误的问题,提供一种i2c接口规避错误起始条件和停止条件的电路结构及方法。

2、本发明解决其技术问题所采用的技术方案是:

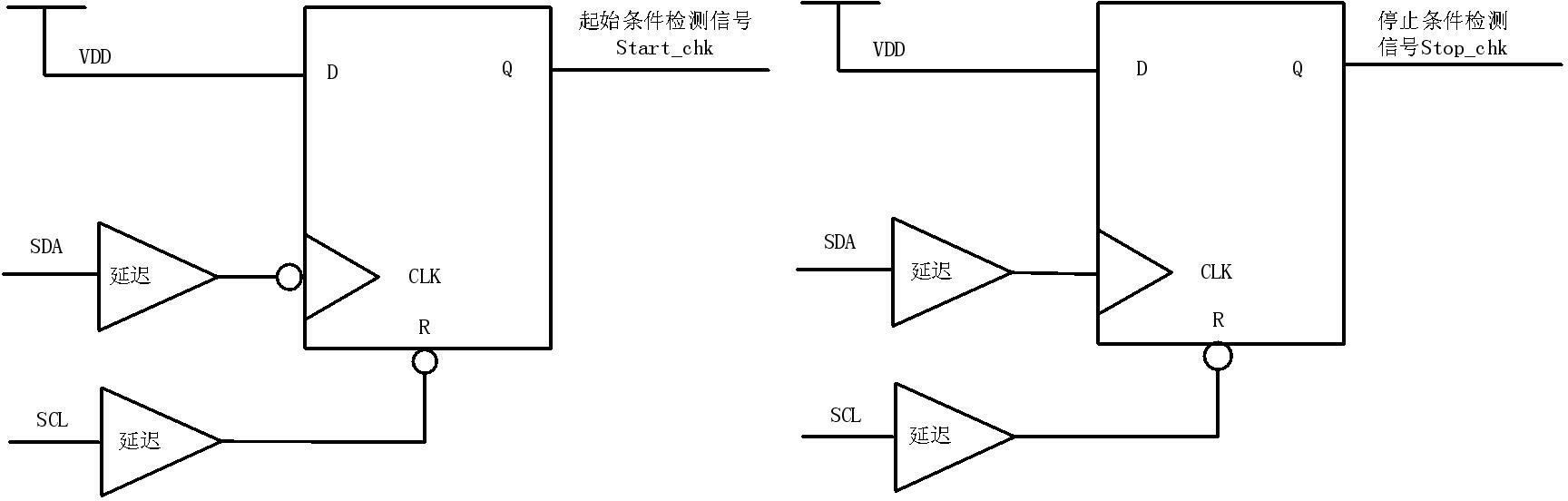

3、本发明提供了一种i2c接口规避错误起始条件的电路结构,包括:第一d触发器、第一scl高电平延迟单元、第一sda延迟单元,其中:

4、所述第一scl高电平延迟单元的输入端与i2c时钟总线scl连接,输出端经过一个反相器后连接所述第一d触发器的复位端,用于对i2c时钟总线scl上的时钟信号上升沿进行延迟;

5、所述第一sda延迟单元的输入端与i2c数据总线sda连接,输出端经过一个反相器后连接所述第一d触发器的时钟端,用于对i2c数据总线sda上的数据信号进行延迟;

6、所述第一d触发器的数据输入端接高电平,输出端输出起始条件检测信号,用于根据延迟后的scl信号和sda信号输出起始条件检测结果;

7、所述第一sda延迟单元的延迟时间设置为预计的起始条件保持时间;

8、所述第一scl高电平延迟单元的延迟时间设置为预计的起始条件保持时间和预计的起始条件建立时间之和。

9、本发明还提供了一种i2c接口规避错误起始条件的方法,基于所述的i2c接口规避错误起始条件的电路结构实现,包括以下步骤:

10、s1a,确定起始条件保持时间,将第一sda延迟单元的延迟时间设置为预计的起始条件保持时间;

11、s1b,确定起始条件建立时间,将第一scl高电平延迟单元的延迟时间设置为预计的起始条件保持时间和预计的起始条件建立时间之和;

12、s1c,由所述的i2c接口规避错误起始条件的电路结构进行起始条件检测。

13、本发明还提供了一种i2c接口规避错误停止条件的电路结构,包括:第二d触发器、第二scl高电平延迟单元、第二sda延迟单元,其中:

14、所述第二scl高电平延迟单元的输入端与i2c时钟总线scl连接,输出端经过一个反相器后连接所述第二d触发器的复位端,用于对i2c时钟总线scl上的时钟信号上升沿进行延迟;

15、所述第二sda延迟单元的输入端与i2c数据总线sda连接,输出端连接所述第二d触发器的时钟端,用于对i2c数据总线sda上的数据信号进行延迟;

16、所述第二d触发器的数据输入端接高电平,输出端输出停止条件检测信号,用于根据延迟后的scl信号和sda信号输出停止条件检测结果;

17、所述第二sda延迟单元的延迟时间设置为预计的停止条件保持时间;

18、所述第二scl高电平延迟单元的延迟时间设置为预计的停止条件保持时间和预计的停止条件建立时间之和。

19、本发明还提供了一种i2c接口规避错误停止条件的方法,基于i2c接口规避错误停止条件的电路结构实现,包括以下步骤:

20、s2a,确定停止条件保持时间,将第二sda延迟单元的延迟时间设置为预计的停止条件保持时间;

21、s2b,确定停止条件建立时间,将第二scl高电平延迟单元的延迟时间设置为预计的停止条件保持时间和预计的停止条件建立时间之和;

22、s2c,由i2c接口规避错误停止条件的电路结构进行停止条件检测。

23、本发明还提供了一种i2c接口规避错误起始条件和停止条件的电路结构,包括:第三d触发器、第四触发器、第三scl高电平延迟单元、第三sda延迟单元:

24、所述第三scl高电平延迟单元的输入端与i2c时钟总线scl连接,输出端经过一个反相器后分别连接所述第三d触发器和第四触发器的复位端,用于对i2c时钟总线scl上的时钟信号上升沿进行延迟;

25、所述第三sda延迟单元的输入端与i2c数据总线sda连接,输出端经过一个反相器后连接所述第三d触发器的时钟端,所述第三sda延迟单元的输出端还与所述第四d触发器的时钟端连接,用于对i2c数据总线sda上的数据信号进行延迟;

26、所述第三d触发器的数据输入端接高电平,输出端输出起始条件检测信号,用于根据延迟后的scl信号和sda信号输出起始条件检测结果;

27、所述第四d触发器的数据输入端接高电平,输出端输出停止条件检测信号,用于根据延迟后的scl信号和sda信号输出停止条件检测结果;

28、所述第三sda延迟单元的延迟时间设置为预计的起始条件保持时间,所述预计的起始条件保持时间和预计的停止条件保持时间相等;

29、所述第三scl高电平延迟单元的延迟时间设置为预计的起始条件保持时间和预计的起始条件建立时间之和,所述预计的起始条件建立时间和预计的停止条件建立时间相等。

30、本发明还提供了一种i2c接口规避错误起始条件的方法,基于所述的i2c接口规避错误起始条件和停止条件的电路结构实现,包括以下步骤:

31、s3a,确定起始条件保持时间,停止条件保持时间和起始条件保持时间相等,将第三sda延迟单元的延迟时间设置为预计的起始条件保持时间;

32、s3b,确定起始条件建立时间,停止条件建立时间和起始条件建立时间相等,将第三scl高电平延迟单元的延迟时间设置为预计的起始条件保持时间和预计的起始条件建立时间之和;

33、s3c,由所述电路结构进行起始条件和停止条件检测。

34、本发明基于i2c协议,提出了一种规避错误识别起始条件和停止条件的电路结构,该电路结构主要由d触发器和延迟单元组成,通过分别延迟i2c总线的时钟线和数据线,增加了起始条件和停止条件的建立时间和保持时间检测窗口,确保了起始条件和停止条件正常产生,避免了外部因素导致的检测到错误的起始条件和停止条件的情况。因为加入了延迟单元,检测电路也具备了一定的毛刺过滤功能,减少了由毛刺而产生的检测错误。对于i2c时钟线和数据线错位的情况,也能通过调节延迟单元的延迟时间来避免检测错误。本发明所述方法,结构简单,易于集成,所用资源较少,且检测准确性高,容错性强,非常适用于各种集成了i2c总线协议的电子产品控制器。

- 还没有人留言评论。精彩留言会获得点赞!