具有可配置空间加速器的处理器、方法和系统与流程

本公开总体上关于电子学,更具体地,本公开的实施例关于可配置空间加速器。

背景技术:

1、处理器或处理器集合执行来自指令集(例如,指令集架构(isa))的指令。指令集是涉及编程的计算机架构的一部分,并且一般包括原生数据类型、指令、寄存器架构、寻址模式、存储器架构、中断和异常处理以及外部输入和输出(i/o)。应当注意,术语“指令”在本文中一般是指宏指令(例如,提供给处理器供执行的指令),或者指微指令(例如,由处理器的解码器解码宏指令所产生的指令)。

技术实现思路

技术特征:

1.一种处理器,包括:

2.如权利要求1所述的处理器,进一步包括多个配置控制器,每一个配置控制器耦合到所述多个处理元件的相应子集,并且每一个配置控制器用于从存储加载配置信息并且引起所述多个处理元件的相应子集根据所述配置信息耦合。

3.如权利要求2所述的处理器,进一步包括多个配置高速缓存,每一个配置控制器耦合至相应的配置高速缓存以取出用于所述多个处理元件的相应子集的配置信息。

4.如权利要求3所述的处理器,其中,由所述执行单元执行的所述第一操作用于将配置信息预取到所述多个配置高速缓存中的每一个中。

5.一种方法,包括:

6.如权利要求5所述的方法,进一步包括:

7.如权利要求6所述的方法,进一步包括:从多个配置高速缓存中的相应配置高速缓存取出用于所述多个处理元件的相应子集的配置信息。

8.如权利要求7所述的方法,其中,由所述执行单元执行的所述第一操作为:将配置信息预取到所述多个配置高速缓存中的每一个中。

9.一种机器可读介质,包括代码,所述代码当被执行时使机器执行如权利要求5-8中的任一项所述的方法。

10.一种处理器,包括:

技术总结

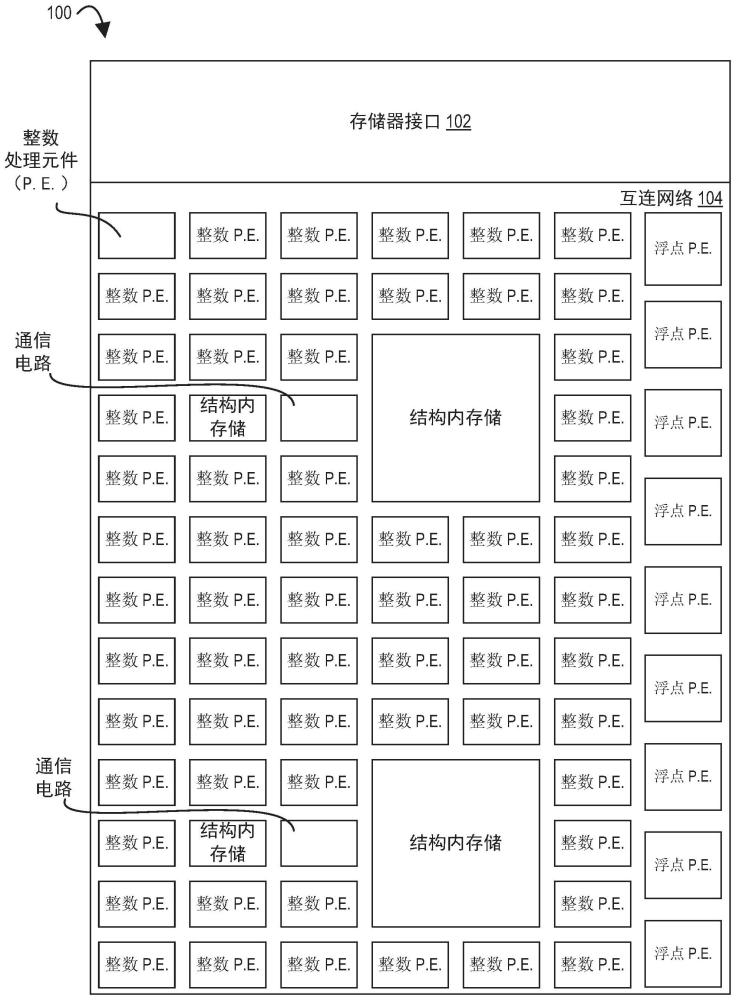

本申请公开了具有可配置空间加速器的处理器、方法和系统。在一个实施例中,处理器包括:核,所述核具有解码器和执行单元,所述解码器用于将指令解码为经解码指令,所述执行单元用于执行所述经解码指令以执行第一操作;多个处理元件;以及互连网络,在所述多个处理元件之间,所述互连网络用于接收包括多个节点的数据流图的输入,其中,所述数据流图用于被覆盖到所述互连网络和所述多个处理元件中,并且每一个节点被表示为所述多个处理元件中的数据流操作器,并且所述多个处理元件用于当传入操作数集到达所述多个处理元件时执行第二操作。

技术研发人员:K·弗莱明,K·D·格洛索普,小西蒙·C·史迪力,J·唐,A·G·加拉

受保护的技术使用者:英特尔公司

技术研发日:

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!