基于忆阻器的存内逻辑电路及全阵列并行计算方法

本技术涉及集成电路,特别是涉及一种基于忆阻器的存内逻辑电路及全阵列并行计算方法。

背景技术:

1、存内计算作为一种面向目标识别、自动驾驶、人工智能、大数据以及5g等新型边缘端应用的计算处理架构,以其具有克服传统冯·诺依曼系统中存储墙和功耗墙瓶颈问题的潜力而受到了广泛关注。

2、基于忆阻器的非易失性逻辑计算是实现这种架构的最有前途的技术路线之一。其中,忆阻器利用电阻值作为物理状态变量,在脉冲电压的操作条件下,可以实现在两个稳定阻值状态,即高阻值态(rhrs)与低阻值态(rlrs)之间的切换,忆阻器的高阻态对应逻辑“0”,低阻态对应逻辑“1”。

3、现阶段基于忆阻器的逻辑计算方法主要分为两类:状态逻辑电路和cmos混合逻辑电路。状态逻辑电路的逻辑输入与输出利用忆阻器的高低阻值态表示,通过外加偏置电压改变忆阻器的阻值态以实现逻辑运算,主要包括实质蕴含逻辑(imply)电路与忆阻器辅助逻辑(magic)电路。基于忆阻器的cmos混合逻辑电路的逻辑输入与输出利用cmos辅助电路或辅助mos管的高低电平、和忆阻器的高低阻值态表示,通过配置混合逻辑电路中忆阻器的初始阻值态和辅助电路分压比改变忆阻器的阻值态以实现逻辑计算。

4、然而现有技术中,基于忆阻器的存内逻辑在高层次的软件算法应用上受限于底层的基础电路结构,尚难以做到行列均可灵活选通,进而难以做到全阵列的并行计算。且现有技术中,基于忆阻器的存内逻辑计算方法尚无法做到行、列信息进行交互并具有并行执行的能力,面对矩阵式计算任务,现有技术需要成倍数增长的时间,影响计算效率。

技术实现思路

1、基于此,有必要针对上述技术问题,提供一种能够进行高效计算的基于忆阻器的存内逻辑电路及全阵列并行计算方法。

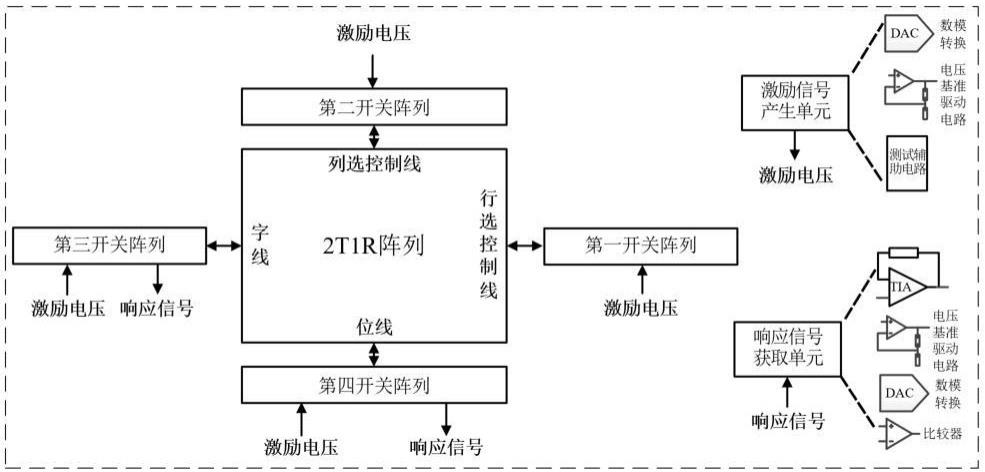

2、一种基于忆阻器的存内逻辑电路,包括:基于忆阻器的存内计算阵列、开关单元、激励信号产生单元以及响应信号获取单元;

3、所述基于忆阻器的存内计算阵列包括多个以阵列形式排布的存内计算单元,各所述存内计算单元均具有四个端口,包括两个输入端口和两个输入输出端口,所述两个输入端口包括行选控制端口和列选控制端口,两个输入输出端口包括忆阻器顶电极连接端口以及忆阻器底电极连接端口;

4、所述开关单元包括四组开关阵列,各组所述开关阵列分别对应连接至所述存内计算单元其中一输入端口,以对该输入端口的状态进行控制;

5、所述激励信号产生单元与所述开关单元连接,并通过所述开关阵列的控制向所述存内计算单元的输入端口提供不同的激励电压;

6、所述响应信号获取单元与所述开关单元连接,并通过开关阵列的控制获取所述存内计算单元输出的不同激励响应信号。

7、在其中一实施例中,在所述存内计算阵列中:

8、位于同一行的存内计算单元的行选控制端口通过行选控制线连接;

9、位于同一列的存内计算单元的列选控制端口通过列选控制线连接;

10、位于同一行的存内计算单元的忆阻器顶电极连接端口通过字线连接;

11、位于同一列的存内计算单元的忆阻器底电极连接端口通过位线连接。

12、在其中一实施例中,所述基于忆阻器的存内计算阵列的连线拓扑结构为:

13、所述行选控制线与字线并行排布,所述列选控制线与位线并行排布;

14、所述行选控制线以及字线,与所述列选控制线以及位线交叉垂直排布。

15、在其中一实施例中,所述开关单元的四组开关阵列分别为第一开关阵列、第二开关阵列、第三开关阵列以及第四开关阵列;

16、所述第一开关阵列中的各开关分别对应的与所述存内计算阵列中某一行的行选控制线连接;

17、所述第二开关阵列中的各开关分别对应的与所述存内计算阵列中某一列的列选控制线连接;

18、所述第三开关阵列中的各开关分别对应的与所述存内计算阵列中某一行的字线连接;

19、所述第四开关阵列中的各开关分别对应的与所述存内计算阵列中某一列的位线连接。

20、在其中一实施例中,所述激励信号产生单元通过开关单元向各所述存内计算单元的输入端口提供包括列选通电压、行选通电压、置位电压、复位电压、读电压以及逻辑操作电压;

21、所述响应信号获取单元获取存内计算阵列输出不同激励响应信号,用于包括阻值读取、模数转换以及信号测试。

22、在其中一实施例中,各所述存内计算单元均包括忆阻器、第一晶体管以及第二晶体管。

23、一种全阵列并行计算方法,所述全阵列并行计算方法应用于上述的基于忆阻器的存内逻辑电路中,包括:

24、对所述基于忆阻器的存内计算阵列中某一选定行中各存内计算单元中的忆阻器的阻值进行同时读取;

25、对所述基于忆阻器的存内计算阵列中某一选定列中各存内计算单元中的忆阻器的阻值进行同时读取;

26、采用所述基于忆阻器的存内计算阵列中某几行和某几列构成的选定区域中存内计算单元进行并行逻辑计算。

27、在其中一实施例中,所述对所述基于忆阻器的存内计算阵列中某一选定行中各存内计算单元中的忆阻器的阻值进行同时读取包括:

28、控制所述存内计算阵列中选定行的字线连接读电压,其它行的字线悬空;

29、控制所述存内计算阵列中所有列的位线全部接地,列选控制线全部接列选通电压;

30、控制所述存内计算阵列中选定行的行选控制线接行选通电压,其它行的行选控制线接地。

31、在其中一实施例中,对所述基于忆阻器的存内计算阵列中某一选定列中各存内计算单元中的忆阻器的阻值进行同时读取包括:

32、控制所述存内计算阵列中所有行的字线全部接地,行选控制线全部接行选通电压;

33、控制所述存内计算阵列中选定列的位线连接读电压,其它列的位线悬空;

34、控制所述存内计算阵列中选定列的列选控制线接列选通电压,其它行列的列选控制线接地。

35、在其中一实施例中,所述采用所述基于忆阻器的存内计算阵列中某几行和某几列构成的选定区域中存内计算单元进行并行逻辑计算包括:

36、在所述存内计算阵列中,将所述选定区域内所有行的字线接地或者接逻辑操作电压,在所述选定区域外的其他行的字线悬空;

37、在所述存内计算阵列中,将所述选定区域内所有列的位线接地或者接逻辑操作电压,在所述选定区域外的其他列的位线悬空;

38、在所述存内计算阵列中,将所述选定区域内所有行的行选控制线接地或行选通电压,在所述选定区域外的其他行的行选控制线全部接地;

39、在所述存内计算阵列中,将所述选定区域内所有列的列选控制线全部接列选通电压,在所述选定区域外的其他列的列选控制线全部接地。

40、上述基于忆阻器的存内逻辑电路及全阵列并行计算方法,该存内逻辑电路包括基于忆阻器的存内计算阵列、开关单元、激励信号产生单元以及响应信号获取单元,其中,基于忆阻器的存内计算阵列包括多个以阵列形式排布的存内计算单元,且各存内计算单元均具有四个输入端口,包括行选控制端口、列选控制端口、忆阻器顶电极连接端口以及忆阻器底电极连接端口,通过利用开关单元中的四组开关阵列分别对存内计算单元的四个输入端口状态进行控制,从而实现对阵列中某一行、某一列或者某一区域进行灵活选择,并基于选择区域进行读或者写或者是逻辑操作,以提高计算效率。

- 还没有人留言评论。精彩留言会获得点赞!