一种基于描述符的通用实时仿真系统数据传输系统

本发明属于实时仿真,具体涉及一种基于描述符的通用实时仿真系统数据传输系统。

背景技术:

1、当前国内外采用cpu+fpga架构实时仿真系统的两种常用数据传输方法为blockdma和scatter gather dma。

2、block dma数据传输方法要求源地址和目标地址必须连续,一次只能传输一块物理地址上连续的数据,完成传输后发起中断;实时仿真系统中采用这种方式,需要在fpga端对接收和发送的数据进行缓存,同时dma写内存数据完成后需要向cpu端发送中断。

3、scatter gather dma数据传输方法通过链表描述物理地址上不连续的存储空间,dma控制器在传输完一块物理地址上连续的数据后,不用发起中断,而是根据链表进行传输下一块物理地址上连续的数据,直至传输完毕后再发起一次中断,如此可以大大减少中断的次数,提高数据传输的效率;这种传输方式一方面适用于传输数据量大的应用场景,对于实时仿真系统而言无法体现其优势,另一方面同样需要fpga端对接收和发送数据进行缓存,根据链表dma写内存数据完成同样需向cpu端发送中断。

4、对于实时仿真技术领域而言,cpu+fpga架构实时仿真系统仿真步长通常只有微秒级,理论上仿真步长越小仿真精度越高,但是实时仿真的前提条件是仿真步长内数据解算不能超时,而降低传输延时实质上是增加数据解算时间,以尽可能满足更小的仿真步长内数据解算需求。上述两种数据传输方法在fpga端均需要对接收和发送的数据进行缓存,同时dma数据写完成后均需向cpu端发送中断,而缓存和中断均是影响传输延时的关键因素。

技术实现思路

1、本发明的目的就是为了解决上述背景技术存在的不足,提供一种基于描述符的通用实时仿真系统数据传输系统,以优化数据传输机制,达到降低传输缓存和中断引入时延的目的。

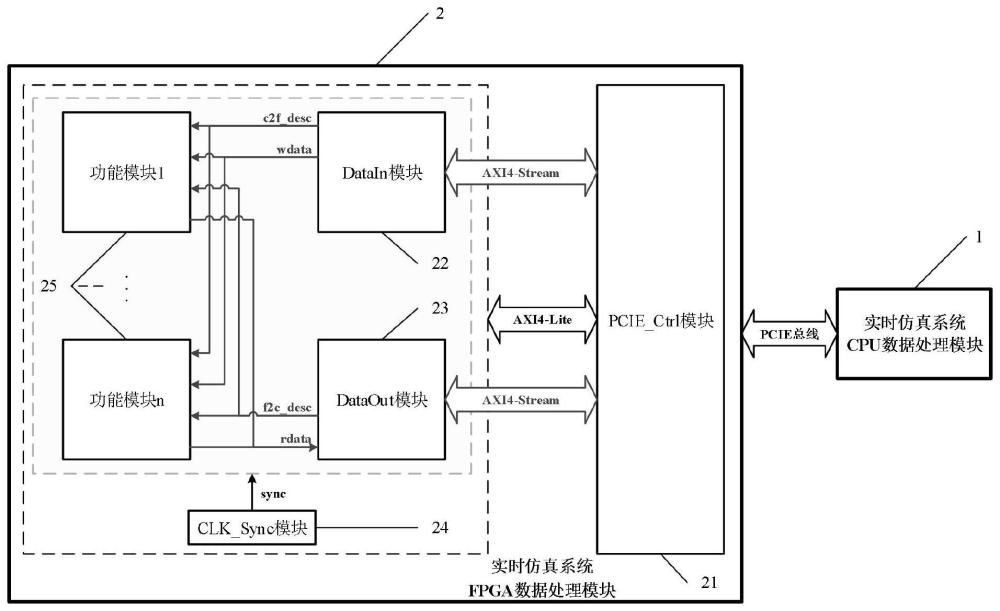

2、本发明采用的技术方案是:一种基于描述符的通用实时仿真系统数据传输系统,包括通过pcie总线进行数据交互的实时仿真系统cpu数据处理模块和实时仿真系统fpga数据处理模块;所述实时仿真系统cpu数据处理模块支持pio读写操作,实现对所述fpga数据处理模块内部子模块的寄存器读写,包括c2f和f2c描述符信息;还支持dma数据的读写操作,实现实时仿真系统cpu数据处理模块和实时仿真系统fpga数据处理模块之间dma数据的接收和发送处理;还用于获取dma写内存数据的最后一个时间戳计数值,用于判断一次dma写内存数据是否完成。

3、上述技术方案中,所述实时仿真系统fpga处理模块包括pcie_ctrl模块、datain模块、dataout模块、clk_sync模块和若干个功能模块;

4、pcie_ctrl模块实现实时仿真系统fpga数据处理模块和实时仿真系统cpu数据处理模块的数据交互;

5、所述pcie_ctrl模块执行对datain模块、dataout模块、clk_sync模块和功能模块的寄存器读写操作,并将dma读内存数据发送给datain模块,同时接收来自dataout模块发送的dma写内存数据;

6、datain模块接收所述pcie_ctrl模块发送的dma读内存数据,并根据c2f描述符寻址功能模块,并将dma读内存数据按照固定格式写入对应寻址寄存器中;

7、dataout模块根据f2c描述符寻址功能模块,将寻址寄存器数据按照固定格式发送给所述pcie_ctrl模块,作为dma写内存数据;

8、clk_sync模块产生脉宽和周期可配置的同步信号,实现所述datain模块、dataout模块、功能模块的数据传输控制。

9、上述技术方案中,所述pcie_ctrl模块内部包括xilinx pcie ip核、发送引擎模块、接收引擎模块和axi4-lite总线互联模块;发送引擎模块、接收引擎模块实现pcie事务层tlp的组包发送和接收解析功能,通过axi4-lite总线互联模块对datain模块、dataout模块、clk_sync模块和功能模块的寄存器读写操作;发送引擎模块将dma读内存数据发送给datain模块,接收引擎模块接收来自dataout模块发送的dma写内存数据;发送引擎模块和接收引擎模块通过xilinx pcie ip核自动完成所实时仿真系统fpga数据处理模块和实时仿真系统cpu数据处理模块之间的数据交互。

10、上述技术方案中,所述datain模块包括第一同步控制模块、第一数据控制模块和第一描述符存储模块;

11、第一同步控制模块进行输入同步信号sync的延时控制;

12、第一描述符存储模块接收pcie_ctrl模块发送的c2f描述符信息并进行存储;

13、第一数据控制模块接收所述pcie_ctrl模块发送的dma读内存数据,并根据c2f描述符寻址功能模块,将dma读内存数据按照固定格式写入对应寻址寄存器中。

14、上述技术方案中,所述dataout模块包括数据组合模块、第二同步控制模块、第二数据控制模块和第二描述符存储模块;

15、数据组合模块用于实现功能模块寻址数据的组合;

16、第二同步控制模块进行输入同步信号sync的延时控制和时间戳计数;

17、第二描述符存储模块接收pcie_ctrl模块发送的c2f描述符信息并进行存储;

18、第二数据控制模块根据f2c描述符寻址功能模块,将寻址寄存器数据按照固定格式发送给pcie_ctrl模块,作为dma写内存数据;时间戳计数值作为dma写内存数据的最后一个数据上传,所述时间戳计数值作为实时仿真cpu数据处理模块判断一次dma写内存数据完成的判断标志,避免采用中断方式。

19、上述技术方案中,所述clk_sync模块包括同步生成模块和第三同步控制模块;同步生成模块用于生成脉宽和周期可配置的同步信号,第三同步控制模块基于同步信号对datain模块、dataout模块、功能模块进行使能控制。

20、上述技术方案中,所述功能模块包括第四同步控制模块和用户自定义功能模块;第四同步控制模块进行输入同步信号sync的延时控制;用户自定义模块根据用户需求添加所需的功能逻辑以实现不同的应用需求。

21、上述技术方案中,所述pcie_ctrl模块与所述datain模块、dataout模块、clk_sync模块、功能模块之间通过axi4-lite总线连接,实现对所连接模块的寄存器读写操作。

22、上述技术方案中,所述pcie_ctrl模块通过与接收引擎rx_engine模块和发送引擎tx_engine模块引出的axi4-stream总线连接,将dma读内存数据发送给datain模块,同时接收来自dataout模块发送的dma写内存数据。

23、本发明的有益效果是:本发明通过过描述符设计和实时数据传输时序设计,规定实时数据传输格式,达到减少实时数据传输路径中的缓存环节,降低传输延时的目的;并通过通用化接口设计,有助于用户自定义fpga功能模块的快速集成。

24、进一步地,本发明每个时钟周期根据128bit f2c描述符寻址获取功能模块1~n对应寄存器组合而成的128bit数据,并以axi4-stream接口形式输出,保证数据无缓存,同时在发送数据的最后一拍将时间戳计数值亦通过数据流形式输出,用于cpu作为数据传输完成判断标志,有效避免了常规dma数据传输方式采用中断机制引入的延时。

25、进一步地,本发明每个时钟周期将axi4-stream接口接收的128bit数据,通过128bit c2f描述符寻址写入功能模块1~n对应寄存器中,保证数据无缓存。

- 还没有人留言评论。精彩留言会获得点赞!