芯片测试的方法、装置、电子设备及存储介质与流程

本技术涉及芯片测试,尤其涉及一种芯片测试的方法、装置、电子设备及存储介质。

背景技术:

1、芯片回片后,对其测试主要包括板级测试和ate机台(automatictest equipment,集成电路自动测试机)。机台测试主要是针对芯片量产测试,需要对每一颗芯片进行一系列科目的测试。

2、然而,在现有机台测试方法中,通常是设置机台的时钟频率与芯片的通信时钟频率一致,机台会在该时钟频率下生成激励信号。但是,在不同协议模式下进行芯片测试,就需要根据模式重新设定机台的上升沿采样,还是下降沿采样,空闲时,时钟是高电平还是低电平,这种设置对于机台的操作费时又费力,降低了测试效率。

技术实现思路

1、有鉴于此,本技术提供了一种芯片测试的方法、装置、电子设备及存储介质,以解决现有技术中在对不同协议模式的芯片进行测试时,需要频繁更改测试机台的设置,费时又费力,降低了测试效率的问题。

2、为实现上述目的,本技术提供如下技术方案:

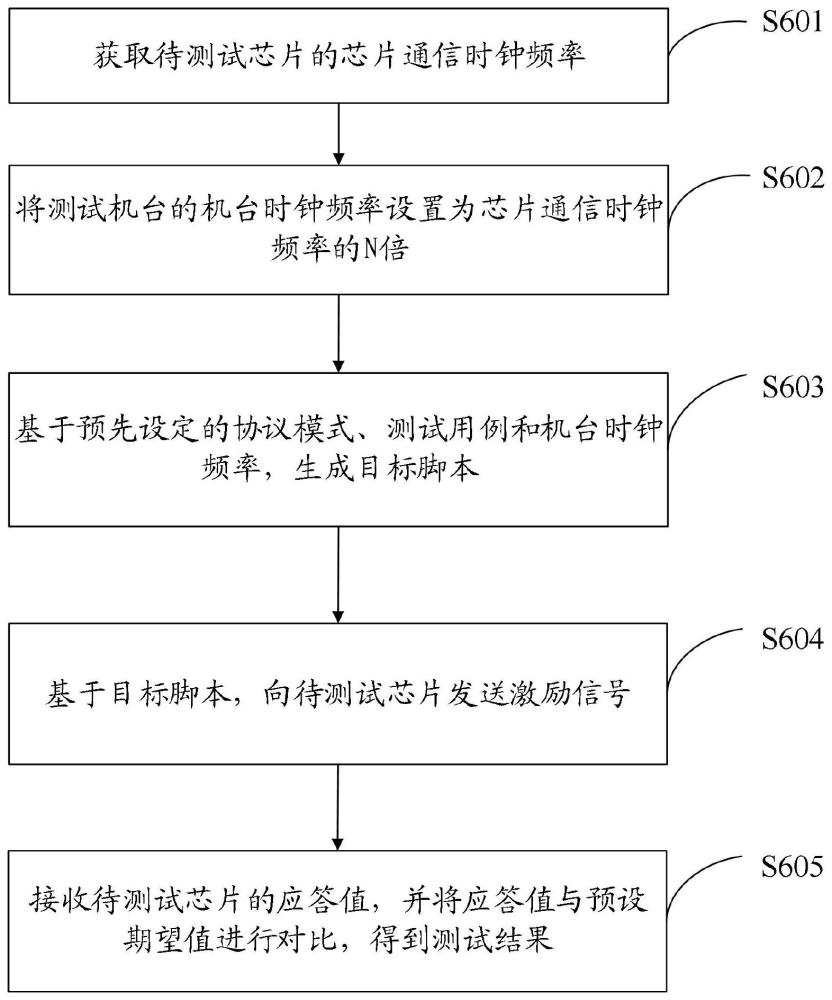

3、本技术第一方面公开了一种芯片测试的方法,包括:

4、获取待测试芯片的芯片通信时钟频率;

5、将测试机台的机台时钟频率设置为所述芯片通信时钟频率的n倍;其中,n为偶数;

6、基于预先设定的协议模式、测试用例和所述机台时钟频率,生成目标脚本;其中,所述目标脚本用于定义所述机台时钟频率、数字输入和数字输出信息;所述数字输入为测试机台向所述待测试芯片发送的激励信号;所述数字输出为待测试芯片向测试机台发出的响应信号;所述激励信号用于提供所述待测试芯片的芯片通信时钟信号、片选信号和输入信号;

7、基于所述目标脚本,向所述待测试芯片发送激励信号;

8、接收所述待测试芯片的应答值,并将所述应答值与预设期望值进行对比,得到测试结果。

9、可选的,上述的方法,所述基于预先设定的协议模式、测试用例和所述机台时钟频率,生成目标脚本,包括:

10、基于预先设定的协议模式、测试用例和所述机台时钟频率,确定当前协议模式下的每一个指令和所述每一个指令对应的波形;

11、基于所述每一个指令和所述每一个指令对应的波形,生成目标脚本。

12、可选的,上述的方法,所述向所述待测试芯片发送激励信号,包括:

13、将所述芯片通信时钟信号通过所述待测试芯片的时钟管脚进行发送;

14、将所述芯片片选信号通过所述待测试芯片的片选信号管脚进行发送;

15、将所述芯片输入信号通过所述待测试芯片的输入管脚进行发送。

16、可选的,上述的方法,所述将测试机台的机台时钟频率设置为所述芯片通信时钟频率的n倍之后,还包括:

17、基于预设的参数表,确定所述测试机台的时钟采样沿参数和空闲状态参数。

18、可选的,上述的方法,所述将所述应答值与预设期望值进行对比,得到测试结果,包括:

19、将所述待测试芯片的应答值与所述预设期望值进行对比;

20、若所述待测试芯片的应答值与所述预设期望值一致,则生成芯片测试合格的测试结果;

21、若所述待测试芯片的应答值与所述预设期望值一致,则生成芯片测试不合格的测试结果。

22、可选的,上述的方法,所述预先设定的协议模式至少包括:模式0、模式1、模式2和模式3;

23、所述模式0对应的参数为:时钟极性为0,时钟相位为0,时钟的第一个跳变沿是上升沿,第二个跳变沿是下降沿;采样触发条件为:所述待测试芯片在收到激励信号的第一个跳变沿时采样;

24、所述模式1对应的参数为:时钟极性为0,时钟相位为1,时钟的第一个跳变沿是上升沿,第二个跳变沿是下降沿;采样触发条件为:所述待测试芯片在收到激励信号的第二个跳变沿时采样;

25、所述模式2对应的参数为:时钟极性为1,时钟相位为0,时钟的第一个跳变沿是下降沿,第二个跳变沿是上升沿;采样触发条件为:所述待测试芯片在收到激励信号的第一个跳变沿时采样;

26、所述模式3对应的参数为:时钟极性为1,时钟相位为1,时钟的第一个跳变沿是下降沿,第二个跳变沿是上升沿;采样触发条件为:所述待测试芯片在收到激励信号的第二个跳变沿时采样。

27、本技术第二方面公开了一种芯片测试的装置,包括:

28、获取单元,用于获取待测试芯片的芯片通信时钟频率;

29、设置单元,用于将测试机台的机台时钟频率设置为所述芯片通信时钟频率的n倍;其中,n为偶数;

30、生成单元,用于基于预先设定的协议模式、测试用例和所述机台时钟频率,生成目标脚本;其中,所述目标脚本用于定义所述机台时钟频率、数字输入和数字输出信息;所述数字输入为测试机台向所述待测试芯片发送的激励信号;所述数字输出为待测试芯片向测试机台发出的响应信号;所述激励信号用于提供所述待测试芯片的芯片通信时钟信号、片选信号和输入信号;

31、发送单元,用于基于所述目标脚本,向所述待测试芯片发送激励信号;

32、对比单元,用于接收所述待测试芯片的应答值,并将所述应答值与预设期望值进行对比,得到测试结果。

33、可选的,上述的装置,所述生成单元,包括:

34、确定子单元,用于基于预先设定的协议模式、测试用例和所述机台时钟频率,确定当前协议模式下的每一个指令和所述每一个指令对应的波形;

35、生成子单元,用于基于所述每一个指令和所述每一个指令对应的波形,生成目标脚本。

36、可选的,上述的装置,所述发送单元,包括:

37、第一发送单元,用于将所述芯片通信时钟信号通过所述待测试芯片的时钟管脚进行发送;

38、第二发送单元,用于将所述芯片片选信号通过所述待测试芯片的片选信号管脚进行发送;

39、第三发送单元,用于将所述芯片输入信号通过所述待测试芯片的输入管脚进行发送。

40、可选的,上述的装置,还包括:

41、确定单元,用于基于预设的参数表,确定所述测试机台的时钟采样沿参数和空闲状态参数。

42、可选的,上述的装置,所述对比单元,包括:

43、对比子单元,用于将所述待测试芯片的应答值与所述预设期望值进行对比;

44、第一生成单元,用于若所述待测试芯片的应答值与所述预设期望值一致,则生成芯片测试合格的测试结果;

45、第二生成单元,用于若所述待测试芯片的应答值与所述预设期望值一致,则生成芯片测试不合格的测试结果。

46、可选的,上述的装置,所述预先设定的协议模式至少包括:模式0、模式1、模式2和模式3;

47、所述模式0对应的参数为:时钟极性为0,时钟相位为0,时钟的第一个跳变沿是上升沿,第二个跳变沿是下降沿;采样触发条件为:所述待测试芯片在收到激励信号的第一个跳变沿时采样;

48、所述模式1对应的参数为:时钟极性为0,时钟相位为1,时钟的第一个跳变沿是上升沿,第二个跳变沿是下降沿;采样触发条件为:所述待测试芯片在收到激励信号的第二个跳变沿时采样;

49、所述模式2对应的参数为:时钟极性为1,时钟相位为0,时钟的第一个跳变沿是下降沿,第二个跳变沿是上升沿;采样触发条件为:所述待测试芯片在收到激励信号的第一个跳变沿时采样;

50、所述模式3对应的参数为:时钟极性为1,时钟相位为1,时钟的第一个跳变沿是下降沿,第二个跳变沿是上升沿;采样触发条件为:所述待测试芯片在收到激励信号的第二个跳变沿时采样。

51、本技术第三方面公开了一种电子设备,包括:

52、一个或多个处理器;

53、存储装置,其上存储有一个或多个程序;

54、当所述一个或多个程序被所述一个或多个处理器执行时,使得所述一个或多个处理器实现如本技术第一方面中任意一项所述的方法。

55、本技术第四方面公开了一种计算机存储介质,其上存储有计算机程序,其中,所述计算机程序被处理器执行时实现如本技术第一方面中任意一项所述的方法。

56、从上述技术方案可以看出,本技术提供的芯片测试的方法中,首先获取待测试芯片的芯片通信时钟频率。然后将测试机台的机台时钟频率设置为芯片通信时钟频率的n倍。接着基于预先设定的协议模式、测试用例和机台时钟频率,生成目标脚本。基于目标脚本,向待测试芯片发送激励信号。最后接收待测试芯片的应答值,并将应答值与预设期望值进行对比,得到测试结果。由此可知,利用本技术的方法,通过将测试机台的机台时钟频率设置为芯片通信时钟频率的n倍,作为测试机台的实际采样时钟,然后编写目标脚本,基于目标脚本生成激励信号并发送到待测试芯片,待测试芯片所需的芯片通信时钟信号、片选信号和输入信号全部由激励信号提供,实现了芯片时钟的可控性,最后接收芯片应答值得到测试结果。实现了在机台不更改设置的情况下,只更改目标脚本中时钟激励的方式,就可满足不同通信模式的测试需求,极大的提高了测试效率。解决了现有技术中对不同协议模式的芯片进行测试时,需要频繁更改测试机台的设置,费时又费力,降低了测试效率的问题。

- 还没有人留言评论。精彩留言会获得点赞!