一种敏感数据传输总线架构、控制逻辑电路及传输系统的制作方法

本技术涉及半导体芯片设计,具体涉及一种用于芯片内部的敏感数据传输总线架构、控制逻辑电路及传输系统。

背景技术:

1、出于保护知识产权及防止黑客攻击等原因,现代半导体芯片的设计实现中通常集成一些较为敏感的数据(简称敏数),譬如:严禁篡改但可公开的且用于标识芯片制造商身份信息的cuid(chipset unique identification,芯片唯一标识)数据;严禁篡改又需保密的且用于片内密码处理引擎开展工作的root-key(根密钥)数据;按需更新且需保密的且用于片内某些加密/解密处理引擎所需的输入激励类数据(包括但不限于:密钥、算法参数、输入分组)等等。

2、现有方案对这些具有敏感属性的片内数据的传输,即从相应的片内提供源(生成端,也可称为敏数源)传输到已知的片内接收地(即接收端,也可称为敏数端)的传输过程,往往没有进行特别的处理考量,容易在传输过程中造成这些数据的泄露、篡改等。

技术实现思路

1、有鉴于此,本说明书实施例提供适合于在半导体芯片内部、以较小的实施成本(譬如芯片的资源/功耗代价、性能消耗等)完成来自于众多敏数源的芯片敏感数据被安全地分发到片内指定敏收端的一种简单总线及控制器的电路架构。

2、本说明书实施例提供以下技术方案:

3、本说明书实施例提供一种敏感数据传输总线架构,应用于芯片内的敏数源和敏数端之间的敏感数据传输,所述敏感数据传输总线架构包括:

4、传输写使能信号接口,其中所述传输写使能信号接口用于传输一组敏感数据的一趟分发操作的使能信号,所述传输写使能信号的位宽为r且为独热式有效,r表示敏数端的数量,敏数端为敏感数据的接收端;

5、地址数据信号接口,其中所述地址数据信号接口用于传输所述分发操作对应的操作数据,所述操作数据包括所述敏感数据对应的敏数源的索引编号、敏数端存储空间的寻址信号、以及所述索引编号的第一基准校验值和所述寻址信号的第二基准校验值,所述地址数据信号接口的位宽为n+i+v,其中n为所述寻址信号的位宽;i为所述索引编号的位宽;v为所述第一基准校验值和所述第二基准校验值的位宽;

6、敏感数据信号接口,其中所述敏感数据信号接口用于传输所述分发操作对应预设位宽的敏感数据;

7、反馈等待信号接口,其中所述反馈等待信号接口用于敏数端在未准备好接收所述分发操作对应传输敏感数据时设置忙反馈信号,当所述忙反馈信号有效时,当前粒度的单次传输不被执行,待等到所述忙反馈信号无效时所述单次传输再被执行。

8、优选地,所述地址数据信号接口的位宽为可编程位宽;和/或,所述敏感数据信号接口的位宽为可编程位宽。

9、优选地,所述敏感数据信号接口的位宽不大于所有敏数源的单组敏感数据量的最小值,以便于对单组敏感数据量各不相同的多个敏数源统一地开展分发传输。

10、优选地,所述地址数据信号接口传输的所述操作数据用于:所述目标敏数端在接收到所述传输写使能信号接口中自身对应的使能信号位有效时,根据接收到的所述操作数据中部分或全部数据进行检测后存储处理。

11、优选地,根据接收到的所述操作数据中部分或全部数据进行检测后存储处理,包括:

12、对所述操作数据中n位长的所述寻址信号与对应自身存储区的地址位段进行检测,当发现所述寻址信号不属于本敏数端对应的寻址空间,则屏蔽接收所述敏感数据,并将自身的敏感数据存储区清空;

13、和/或,对所述操作数据中i位长的索引编号与片内敏数源的索引值位段进行检测,当发现所述索引编号的敏数源不属于本敏数端合法对应的敏数源,则屏蔽接收所述敏感数据,并将自身的敏感数据存储区清空;

14、和/或,对所述操作数据中v位长的第一基准校验值和第二基准校验值,与自身计算生成的实时校验值进行比对校验,当发现校验结果不一致时,则屏蔽接收所传敏感数据,并将自身的敏感数据存储区清空,其中所述实时校验值为敏数端根据实际接收到的所述寻址信号和所述索引编号而实时计算生成的校验值。

15、优选地,所述地址数据信号接口传输的所述寻址信号还用于:在所述分发操作的敏数源中,单个敏数源在一趟分发的整个传输过程中伴随提供位宽全长的且每次传输中依序变化的敏数端存储空间的寻址信号,以使目标敏数端基于所述传输写使能信号接口的有效位和所述依序变化的敏数端存储空间的寻址信号中的2位数据进行敏感数据的存储。

16、优选地,所述第一基准校验值和/或所述第二基准校验值为基于以下任意一种校验方式得到的校验值:奇偶校验、循环冗余码校验。

17、优选地,所述第一基准校验值和/或所述第二基准校验值在敏数源向所述敏感数据信号接口输入数据时生成。

18、优选地,所述敏感数据传输总线架构还包括监测接口,其中所述监测接口用于传输异常配置信号,以使目标敏数端基于所述异常配置信号进行置起和/或预定义的响应机制,并自行判断是接收还是屏蔽当前分发传输。

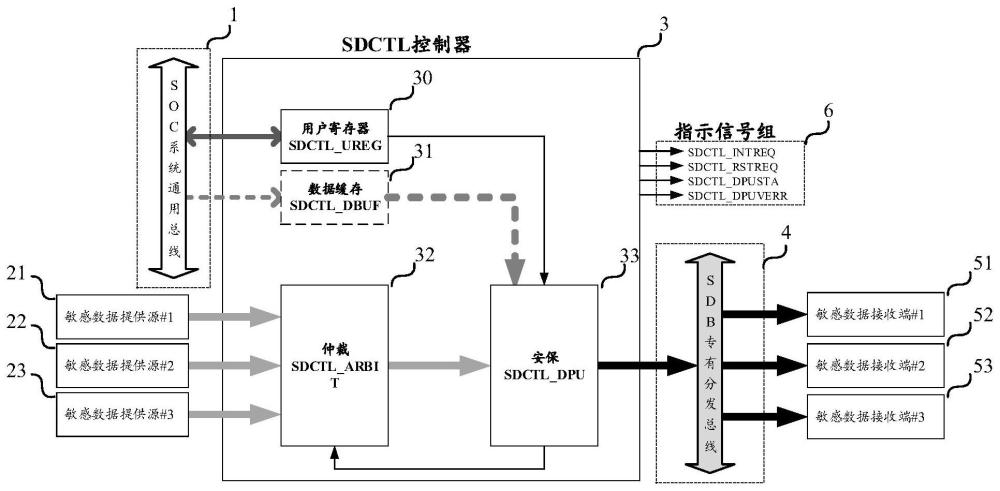

19、本说明书实施例还提供一种敏感数据传输控制逻辑电路,设置于芯片内,且位于芯片内的敏数源与如本技术中任意一项所述的敏感数据传输总线架构之间,所述敏感数据传输控制逻辑电路包括:用户寄存器子模块、安保子模块、仲裁子模块和与所述敏数源对应的输入端口;

20、所述输入端口用于连接敏数源;

21、所述仲裁子模块用于对多个所述输入端口的敏数源进行仲裁;

22、所述配置寄存器包括至少一对寄存器组,每对寄存器组包括安保分发屏蔽使能寄存器和安保控制寄存器,所述安保分发屏蔽使能寄存器用于配置该安保单元安保单元对应的合法敏数源,所述安保控制寄存器用于配置安保单元对应的合法敏数端;以及,所述用户寄存器子模块与芯片内的通用总线连接,以便芯片对所述寄存器组进行配置;

23、所述安保子模块的各安保单元用于根据对应所述寄存器组的配置数据,对所述仲裁子模块仲裁后的敏数源向敏数端传输敏感数据的传输过程进行分发保护。

24、优选地,分发保护包括:

25、当根据对应所述寄存器组的配置数据确定出目标敏数源被分发屏蔽时,所述安保子模块控制所述仲裁子模块,使所述仲裁子模块的缓存不被写入当前正在输入的敏感数据;

26、和/或,当根据对应所述寄存器组的配置数据确定出目标敏数源不需要分发屏蔽时,则所述安保子模块控制所述仲裁子模块,使所述仲裁子模块的缓存从敏数源输入敏感数据,并将所述仲裁子模块缓存的敏感数据通过所述敏感数据传输总线架构向敏数端广播式分发传输。

27、优选地,一趟分发操作的分发保护的触发满足以下条件:目标安保单元对应所述寄存器组中,安保控制寄存器中的安保使能比特位设置为1,安保分发屏蔽使能寄存器对应指定敏数源的比特位设置为1,以及指定敏数源在分发传输期间给出的敏数端存储空间地址落在目标安保单元的保护范围内。

28、优选地,所述安保控制寄存器还用于配置安保单元对应的合法敏数端包括:配置合法敏数端对应的保护使能、保护配置的更新锁护及保护存储空间范围,其中所述安保控制寄存器包括1比特位的保护使能,1比特位的保护配置更新锁护和多比特位的存储空间保护范围设置位域。

29、优选地,多比特位的存储空间保护范围设置位域包括:1比特位地址方式配置位、多比特位基础地址和多比特位额外地址;其中,当地址方式配置位设置为0时,则存储空间保护范围为自基础地址到额外地址的地址范围;当地址方式配置位设置为1时,则存储空间保护范围为让存储空间保护地址与额外地址的逻辑与结果和基础地址与额外地址的逻辑与结果相等的空间地址构成的地址范围。

30、优选地,所述安保子模块的各安保单元还用于根据对应所述寄存器组的配置数据,在一趟分发操作的整个传输过程期间进行实时校验的合法性监测,并输出故障信息。

31、优选地,实时校验的合法性监测包括以下任意一项或多项:

32、根据各安保单元的配置寄存器确定敏数源是否合法;

33、根据各安保单元的配置寄存器确定敏数端是否合法;

34、根据各安保单元的配置寄存器确定保护的使能是否被修改;

35、根据各安保单元的配置寄存器确定保护地址范围是否合法。

36、优选地,所述敏感数据传输控制逻辑电路还包括数据缓存子模块,其中所述数据缓存子模块用于提供敏感数据的缓存空间,以基于缓存空间实现预设粒度转换处理和/或优先级传输控制。

37、本说明书实施例还提供一种敏感数据传输系统,包括:敏数源、如本技术中任意一项所述的敏感数据传输总线架构、如本技术中任意一项所述的敏感数据传输控制逻辑电路、芯片内的通用总线和敏数端;

38、其中,所述敏数源与所述敏感数据传输控制逻辑电路的输入端口连接,所述通用总线与所述敏感数据传输控制逻辑电路的用户寄存器子模块连接,所述敏感数据传输控制逻辑电路的安保子模块通过所述敏感数据传输总线架构与所述敏数端连接。

39、与现有技术相比,本说明书实施例采用的上述至少一个技术方案能够达到的有益效果至少包括:

40、通过提供适合于在半导体芯片内部的一种简单总线架构,能够以较小的实施成本(譬如芯片的资源/功耗代价、性能消耗等)完成来自于众多片内敏数源的芯片敏感数据被安全地分发到片内指定敏收端,使得敏感数据片内传输具有良好的统一性、可扩展性、安全性等性能。

- 还没有人留言评论。精彩留言会获得点赞!