PCB设计中快速给多个铜皮赋网络的方法、系统及介质与流程

本发明涉及pcb设计领域,具体涉及pcb设计中快速给多个铜皮赋网络的方法、系统及介质。

背景技术:

1、在设计多波束多单元的相控阵pcb时经常会遇到给多个单元的天线单元馈电网络的铜皮赋予不同的网络,对于少量的或者只有几十个天线单元馈电网络的铜皮我们可以使用软件自带的赋网络方法,通过人工手动的一个一个的给不同的铜皮赋不同网络,但是在对于几百个或者上千个天线单元时,如果一个一个给不同的铜皮赋予不同的网络可能会花上几个小时的时间,工作量大,人工成本高,而且还容易出错,效率低。

2、目前市面针对提升pcb设计效率的有很多方法和现有技术,例如cn 108920245 a“一种pcb设计中dangling line的处理方法”、cn 107885950 a“一种pcb设计中删除重叠过孔的方法”和cn 110377975 b“一种pcb设计中差分线过孔附近gnd过孔检查的方法和系统”等现有方法,这些现有方法都是利用cadence软件供了开放式的二次开发接口语言编写skill来提升设计效率,但是目前还没有针对解决快速给多个铜皮赋予网络的方法。

3、有鉴于此,特提出本申请。

技术实现思路

1、本发明所要解决的技术问题是现有方法都是依靠软件自身所携带的功能手动的一个一个地给铜皮赋予网络,当设计相控阵或者射频阵列之类的pcb板时,就会对大量的铜皮赋予不同的网络,如果依靠人工一个一个赋网络时效率非常低,工作量大,人工成本高,而且还容易出错。

2、本发明目的在于提供pcb设计中快速给多个铜皮赋网络的方法、系统及介质,本发明通过编程形式形成一种自动化工具,能快速的给多个铜皮赋于正确网络的方法,替代了现有技术方案中人工手动的一个一个给铜皮赋网络的方式,采用本发明可快速给多个铜皮赋于正确的网络,极大的提高了设计效率,节约了人力成本,保证了设计质量。

3、本发明通过下述技术方案实现:

4、第一方面,本发明提供了pcb设计中快速给多个铜皮赋网络的方法,该方法通过编程形式形成一种自动化工具;该方法包括:

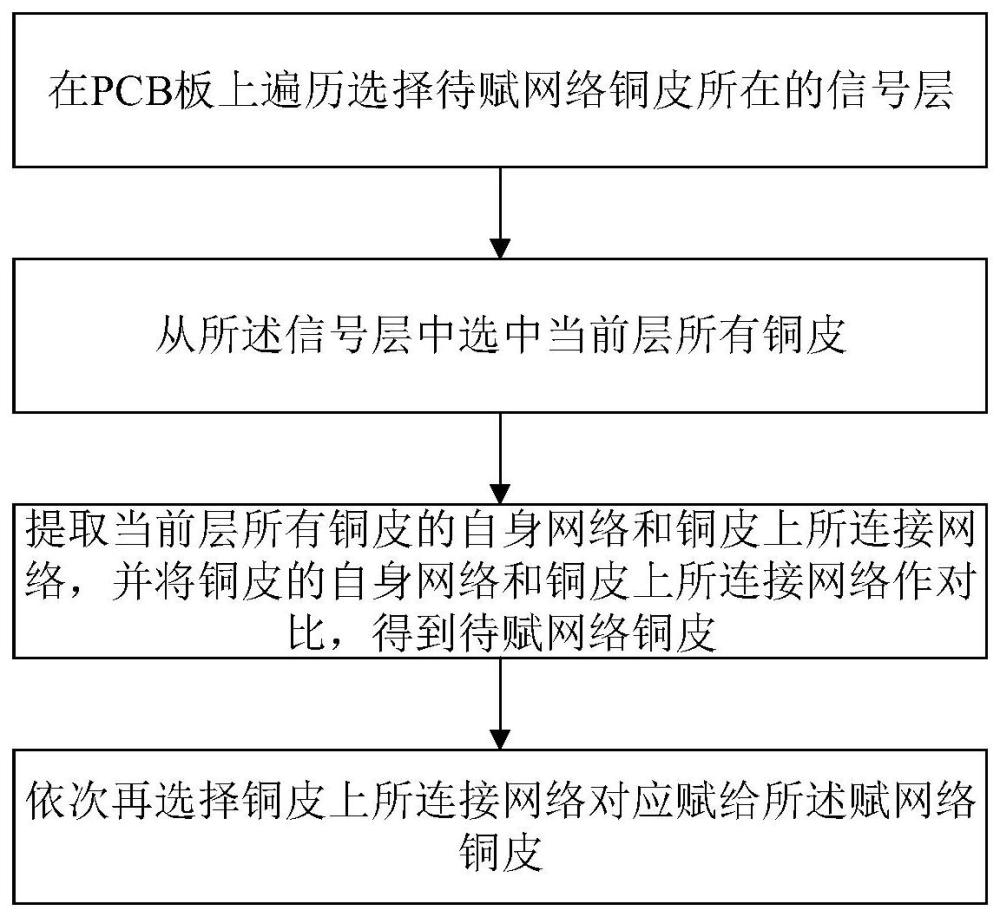

5、在pcb板上遍历选择待赋网络铜皮所在的信号层,从信号层中选中当前层所有铜皮;

6、提取当前层所有铜皮的自身网络和铜皮上所连接网络,并将铜皮的自身网络和铜皮上所连接网络作对比,得到待赋网络铜皮;

7、依次再选择铜皮上所连接网络对应赋给赋网络铜皮。

8、本发明使用cadence软件作为pcb设计时对某一信号层多个铜皮赋予不同网络时,通过使用本发明的自动化工具能够快速的通过简单操作实现对多个铜皮赋上正确的网络,能大大提高设计效率和节约人工成本。

9、作为进一步地优选,从信号层中选中当前层所有铜皮,具体为:

10、通过识别铜皮的中心坐标依次对当前层中所有的铜皮进行选中。

11、作为进一步地优选,铜皮上所连接网络指的是铜皮上所连接的引脚(pin)网络或过孔(via)网络。

12、作为进一步地优选,铜皮的自身网络包括铜皮上所连接的引脚(pin)网络、铜皮上所连接的过孔(via)网络或悬空网络。

13、作为进一步地优选,将铜皮的自身网络和铜皮上所连接网络作对比,得到待赋网络铜皮,包括:

14、将铜皮的自身网络和铜皮上所连接网络作对比:

15、若铜皮的自身网络和铜皮上所连接网络不一致,则把网络异常的铜皮列为待赋网络铜皮;

16、若铜皮的自身网络和铜皮上所连接网络一致,则不存在待赋网络铜皮。

17、作为进一步地优选,网络异常的铜皮,判断步骤为:

18、基于cadence软件中的drc规则比对,若铜皮的自身网络和铜皮上所连接网络属性不一致并提示错误代码vs,则该铜皮为网络异常的铜皮;

19、其中,错误代码vs标识过孔v的网络和铜皮s的网络冲突。

20、第二方面,本发明提供了pcb设计中快速给多个铜皮赋网络的系统,该系统使用上述的pcb设计中快速给多个铜皮赋网络的方法;该系统包括:

21、遍历选择单元,用于在pcb板上遍历选择待赋网络铜皮所在的信号层;

22、选中层铜皮单元,用于从信号层中选中当前层所有铜皮;

23、提取单元,用于提取当前层所有铜皮的自身网络和铜皮上所连接网络;

24、对比单元,用于将铜皮的自身网络和铜皮上所连接网络作对比,得到待赋网络铜皮;

25、赋值单元,用于依次再选择铜皮上所连接网络对应赋给赋网络铜皮。

26、作为进一步地优选,铜皮上所连接网络指的是铜皮上所连接的引脚(pin)网络或过孔(via)网络;

27、铜皮的自身网络包括铜皮上所连接的引脚(pin)网络、铜皮上所连接的过孔(via)网络或悬空网络。

28、第三方面,本发明又提供了一种电子设备,包括存储器、处理器以及存储在所述存储器中并可在所述处理器上运行的计算机程序,所述处理器执行所述计算机程序时实现上述的pcb设计中快速给多个铜皮赋网络的方法。

29、第四方面,本发明又提供了一种计算机可读存储介质,所述计算机可读存储介质存储有计算机程序,所述计算机程序被处理器执行时实现上述的pcb设计中快速给多个铜皮赋网络的方法。

30、本发明与现有技术相比,具有如下的优点和有益效果:

31、本发明pcb设计中快速给多个铜皮赋网络的方法、系统及介质,本发明通过编程形式形成一种自动化工具,能快速的给多个铜皮赋于正确网络的方法,替代了现有技术方案中人工手动的一个一个给铜皮赋网络的方式。采用本发明可快速给多个铜皮赋于正确的网络,极大的提高了设计效率,节约了人力成本,保证了设计质量。本发明使用时,直接调用该方法生成的自动化工具,能够实现pcb设计中快速给多个铜皮赋正确的网络。

技术特征:

1.pcb设计中快速给多个铜皮赋网络的方法,其特征在于,该方法通过编程形式形成一种自动化工具;该方法包括:

2.根据权利要求1所述的pcb设计中快速给多个铜皮赋网络的方法,其特征在于,从所述信号层中选中当前层所有铜皮,具体为:

3.根据权利要求1所述的pcb设计中快速给多个铜皮赋网络的方法,其特征在于,所述铜皮上所连接网络指的是铜皮上所连接的引脚网络或过孔网络。

4.根据权利要求1所述的pcb设计中快速给多个铜皮赋网络的方法,其特征在于,所述铜皮的自身网络包括铜皮上所连接的引脚网络、铜皮上所连接的过孔网络或悬空网络。

5.根据权利要求1所述的pcb设计中快速给多个铜皮赋网络的方法,其特征在于,将铜皮的自身网络和铜皮上所连接网络作对比,得到待赋网络铜皮,包括:

6.根据权利要求5所述的pcb设计中快速给多个铜皮赋网络的方法,其特征在于,所述网络异常的铜皮,判断步骤为:

7.pcb设计中快速给多个铜皮赋网络的系统,其特征在于,该系统包括:

8.根据权利要求7所述的pcb设计中快速给多个铜皮赋网络的系统,其特征在于,所述铜皮上所连接网络指的是铜皮上所连接的引脚网络或过孔网络;

9.一种电子设备,包括存储器、处理器以及存储在所述存储器中并可在所述处理器上运行的计算机程序,其特征在于,所述处理器执行所述计算机程序时实现如权利要求1至6任一项所述的pcb设计中快速给多个铜皮赋网络的方法。

10.一种计算机可读存储介质,所述计算机可读存储介质存储有计算机程序,其特征在于,所述计算机程序被处理器执行时实现如权利要求1至6任一项所述的pcb设计中快速给多个铜皮赋网络的方法。

技术总结

本发明公开了PCB设计中快速给多个铜皮赋网络的方法、系统及介质,该方法通过编程形式形成一种自动化工具;该方法包括:在PCB板上遍历选择待赋网络铜皮所在的信号层,从信号层中选中当前层所有铜皮;提取当前层所有铜皮的自身网络和铜皮上所连接网络,并将铜皮的自身网络和铜皮上所连接网络作对比,得到待赋网络铜皮;依次再选择铜皮上所连接网络对应赋给赋网络铜皮。本发明通过编程形式形成一种自动化工具,能快速的给多个铜皮赋于正确网络的方法,替代了现有技术方案中人工手动的一个一个给铜皮赋网络的方式,采用本发明可快速给多个铜皮赋于正确的网络,极大的提高了设计效率,节约了人力成本,保证了设计质量。

技术研发人员:何静,朱翔宇,鲁国林,曾凌,杨明生,许堂明,姚莉琳,吴建

受保护的技术使用者:重庆两江卫星移动通信有限公司

技术研发日:

技术公布日:2024/3/31

- 还没有人留言评论。精彩留言会获得点赞!