用于矩阵操作加速器的指令的装置、方法和系统与流程

本公开总体上关于计算机处理器架构,并且更具体地关于用于执行用于使用矩阵操作加速器电路来执行矩阵操作的指令的装置、系统和方法。

背景技术:

1、处理器或处理器集合执行来自指令集(例如,指令集架构(isa))的指令。指令集是计算机架构的关于编程的部分,并且一般包括原生数据类型、指令、寄存器架构、寻址模式、存储器架构、中断和异常处置以及外部输入和输出(i/o)。应当注意,术语“指令”在本文中可以指宏指令或指微指令,该宏指令例如提供给处理器供执行的指令,该微指令例如由处理器的解码器对宏指令解码所产生的指令。

技术实现思路

技术特征:

1.一种装置,包括:

2.如权利要求1所述的装置,其中,每个处理通道具有与所述第二数据元素宽度相等的处理通道宽度。

3.如权利要求1或2所述的装置,其中,所述第一多个源矩阵数据元素和所述第二多个源矩阵数据元素包括16位浮点数据元素,并且所述累加矩阵数据元素包括32位浮点数据元素。

4.如权利要求1至3中的任一项所述的装置,进一步包括:

5.如权利要求4所述的装置,其中,所述第一多个源矩阵数据元素或所述第二多个源矩阵数据元素的子集中的一个或多个矩阵数据元素用于在多个操作中由所述矩阵处理电路重新使用。

6.如权利要求4所述的装置,其中,所述本地缓冲器存储装置用于存储所述第一多个源矩阵数据元素的子集和所述第二多个源矩阵数据元素的子集。

7.如权利要求5所述的装置,其中,所述矩阵处理电路用于:利用所述第一多个源矩阵数据元素的子集和所述第二多个源矩阵数据元素的子集执行矩阵操作,将对应的结果数据元素存储在所述本地缓冲器存储装置中,并且将所述对应的结果数据元素与后续的矩阵操作的后续的结果数据元素组合。

8.如权利要求4至7中的任一项所述的装置,其中,所述矩阵处理电路用于阻止对所述本地缓冲器存储装置的至少一部分的回收。

9.如权利要求1至8中的任一项所述的装置,其中,所述矩阵处理电路包括布置在所述多个处理通道中的处理元件的二维网格。

10.如权利要求1至9中的任一项所述的装置,进一步包括集成电路ic,所述ic包括所述第一一个或多个向量寄存器、所述第二一个或多个向量寄存器、所述第三一个或多个向量寄存器、所述矩阵处理电路和所述操作数路由电路。

11.一种方法,包括:

12.一种方法,包括:

13.一种系统,包括:

技术总结

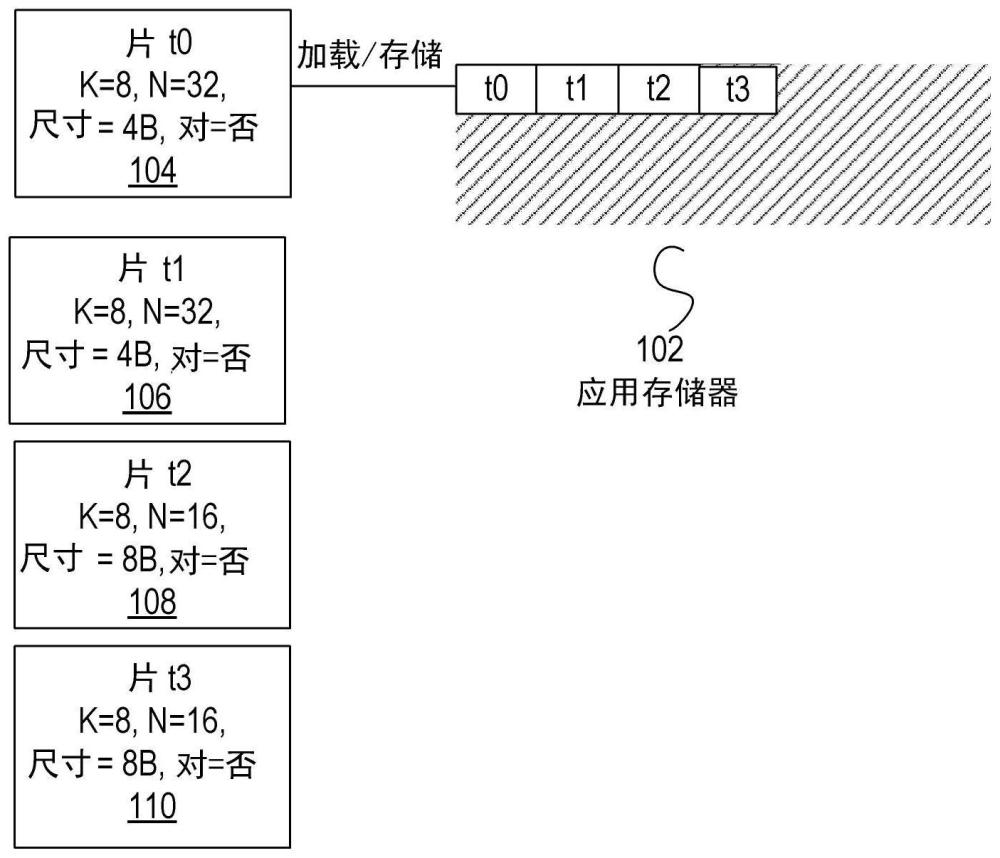

本申请公开了用于矩阵操作加速器的指令的装置、方法和系统。处理器包括矩阵操作加速器电路,该电路包括融合乘法累加电路的二维网格,二维网格可切换至调度模式,其中,该电路从第一多个寄存器加载第一缓冲器,检查第二缓冲器是否存储紧接在前的输入二维矩阵,以及当第二缓冲器存储紧接在前的输入二维矩阵时:在前一指令与单条指令的执行之间阻止对第二缓冲器的回收,对第一输入二维矩阵和紧接在前的输入二维矩阵执行操作,以及将结果存储在结果存储中,以及当第二缓冲器未存储紧接在前的输入二维矩阵时:将第二输入二维矩阵加载到第二缓冲器中,对第一输入二维矩阵和第二输入二维矩阵执行操作,以及将结果存储在结果存储中。

技术研发人员:A·格雷德斯廷,S·卢巴诺维奇,S·梅勒,S·哈劳夫,G·贝格,Z·斯波比尔,J·亚勒露兹,R·施奈德

受保护的技术使用者:英特尔公司

技术研发日:

技术公布日:2024/3/21

- 还没有人留言评论。精彩留言会获得点赞!