运算装置及方法、芯片和电子设备与流程

本公开涉及计算机,尤其涉及一种运算装置及方法、芯片和电子设备。

背景技术:

1、浮点数是计算机中一种重要的数字格式,在计算机中浮点数由符号、指数(也称阶码)和尾数三部分组成。为了满足不同业务的不同需求,计算机通常需要支持浮点数的多种计算类型,例如包括提取浮点数的小数部分。相关技术中,为了提取浮点数的小数部分,计算过程既可以使用向下取整指令和减法指令先后完成计算,也可以是在硬件上,先基于向下取整单元电路对浮点数执行向下取整操作,再将浮点数向下取整操作的结果作为加法单元电路的输入,基于加法单元电路对浮点数与浮点数向下取整的结果进行减法运算。

2、然而,使用两条指令来提取浮点数的小数部分会降低指令执行的效率,通过硬件将向下取整的结果作为加法单元电路的输入则会导致加法单元时序紧张,因为加法单元必须要在拿到向下取整单元的计算结果后才能开始计算。

技术实现思路

1、本公开提出了一种运算装置及方法、芯片和电子设备。

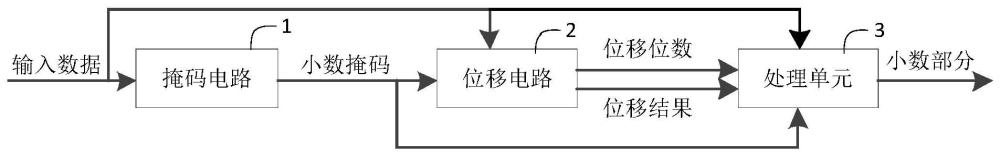

2、根据本公开的一方面,提供了一种运算装置,所述运算装置用于提取输入数据的小数部分,所述运算装置包括掩码电路、位移电路、处理电路;所述掩码电路用于获取所述输入数据的小数掩码,并将所述小数掩码输出至所述位移电路和所述处理电路,所述小数掩码用于标记所述输入数据的尾数的小数部分;所述位移电路用于根据所述小数掩码,对所述输入数据的尾数进行位移操作,得到位移位数和位移结果,并将所述位移位数和所述位移结果输出至所述处理电路;所述处理电路用于根据所述小数掩码、所述位移位数和所述位移结果,确定所述输入数据的小数部分。

3、在一种可能的实现方式中,所述处理电路包括尾数单元电路、指数单元电路、特殊值检测单元电路、装配单元电路;所述尾数单元电路用于根据所述位移结果确定结果尾数,并将所述结果尾数输出至所述装配单元电路,所述结果尾数是用浮点数形式表示所述输入数据的小数部分时的尾数;所述指数单元电路用于根据所述位移位数确定结果指数,并将所述结果指数输出至所述装配单元电路,所述结果指数是用浮点数形式表示所述输入数据的小数部分时的指数;所述特殊值检测单元电路用于根据所述小数掩码检测所述输入数据的特殊值标志,并将所述特殊值标志输出至所述装配单元电路,所述特殊值标志的类别包括无穷、非数、零、纯小数、纯整数;所述装配单元电路根据所述结果尾数、所述结果指数、所述特殊值标志,确定所述输入数据的小数部分。

4、在一种可能的实现方式中,所述掩码电路包括第一减法器、第一右移器、比较器、第一选择器,所述比较器用于对所述输入数据的指数部分与第一预设阈值进行比较,得到比较结果,并将所述比较结果输出至所述第一选择器;所述第一选择器用于在比较结果为所述输入数据的指数部分小于或等于第一预设阈值的情况下,选择所述输入数据的小数掩码为预设位数的全1数据;或者,所述第一选择器用于在比较结果为所述输入数据的指数部分大于第一预设阈值的情况下,选择通过所述第一减法器和所述右移器确定所述输入数据的小数掩码,其中,所述第一减法器用于计算所述输入数据的指数部分与第一预设阈值的第一差值,并将所述第一差值输出至所述第一右移器;所述第一右移器用于将所述预设位数的全1数据右移所述第一差值位,得到右移数据,并将所述右移数据传输至所述第一选择器;所述第一选择器用于在比较结果为所述输入数据的指数部分大于第一预设阈值的情况下,选择所述右移数据为所述输入数据的小数掩码。

5、在一种可能的实现方式中,所述位移电路包括:按位与运算器、前导零检测器、按位或运算器、前导一检测器、第二选择器、左移器、第二减法器、第二右移器、第三选择器、粘滞位检测器;所述第二选择器用于在所述输入数据大于或等于零的情况下,选择将所述按位与运算器、所述前导零检测器确定的左移位数输出至所述左移器,或者,在所述输入数据小于零的情况下,选择将所述按位或运算器、所述前导一检测器确定的左移位数输出至所述左移器;所述左移器用于根据收到的左移位数,对所述输入数据的尾数部分执行左移操作,得到左移结果,并将所述左移结果传输至所述第三选择器;所述第二减法器用于计算所述输入数据的指数部分与第二预设阈值的第二差值,并将所述第二差值作为右移位数输出至所述第二右移器;所述第二右移器用于根据收到的右移位数,对所述输入数据的尾数部分执行右移操作,得到右移结果,并将所述右移结果传输至所述第三选择器和所述粘滞位检测器,所述粘滞位检测器用于根据所述右移结果确定粘滞位的值;所述第三选择器用于在所述输入数据的指数部分小于第一预设阈值的情况下,选择所述右移结果作为位移结果,或者,在所述输入数据的指数部分大于或等于第一预设阈值的情况下,选择所述左移结果作为位移结果。

6、在一种可能的实现方式中,所述按位与运算器用于计算所述输入数据的尾数部分与所述小数掩码的按位与操作,得到按位与结果,并将所述按位与结果传输至所述前导零检测器;所述前导零检测器用于从高位至低位检测所述按位与结果,将第一个非零位之前零位的数量确定为第一左移位数;所述按位或运算器用于计算所述输入数据的尾数部分与取反后的所述小数掩码的按位或操作,得到按位或结果,并将所述按位或结果传输至所述前导一检测器;所述前导一检测器用于从高位至低位检测所述按位或结果,将第一个零位之前非零位的数量确定为第二左移位数。

7、在一种可能的实现方式中,所述尾数单元电路包括:按位取反运算器、加法器,第四选择器,所述第四选择器用于在所述输入数据大于或等于零的情况下,选择所述位移结果作为小数部分的结果尾数,或者,在所述输入数据小于零且所述粘滞位等于一的情况下,选择用所述按位取反运算器对所述位移结果执行按位取反操作后的按位取反结果,作为小数部分的结果尾数,或者,在所述输入数据小于零且所述粘滞位等于零的情况下,选择用所述加法器对所述按位取反结果执行加一操作后的加一结果,作为小数部分的结果尾数。

8、在一种可能的实现方式中,所述位移位数包括左移位数,所述位移电路还用于将所述左移位数输入至所述指数单元电路,所述指数单元电路包括第三减法器、第五选择器,所述第五选择器用于在所述输入数据小于零且所述输入数据的指数部分小于第一预设阈值的情况下,选择第一预设值作为小数部分的结果指数;或者,在所述输入数据大于或等于零,或所述输入数据小于零且所述输入数据的指数部分大于或等于第一预设阈值的情况下,选择用于所述第三减法器对所述输入数据的指数部分与所述左移位数执行减法操作后的减法结果,作为小数部分的结果指数。

9、在一种可能的实现方式中,所述特殊值检测单元电路用于在所述输入数据的尾数部分和指数部分均为零的情况下,将所述特殊值标志确定为零;或者,在所述输入数据的指数部分均为一的情况下,将所述特殊值标志确定为无穷或非数;或者,在所述输入数据的指数部分小于第一预设阈值,将所述特殊值标志确定为纯小数;或者,在所述输入数据的尾数部分与所述小数掩码进行按位与操作的结果为零,且所述输入数据不等于0或非数或无穷的情况下,将所述特殊值标志确定为纯整数。

10、在一种可能的实现方式中,所述装配单元电路包括第六选择器、第七选择器、第八选择器;所述第六选择器用于在所述特殊值标志为纯小数且所述输入数据大于零的情况下,选择所述输入数据作为第一选择结果输出至所述第七选择器,否则选择所述输入数据的符号位、所述结果指数、所述结果尾数的拼装结果作为第一选择结果输出至所述第七选择器;所述第七选择器用于在所述特殊值标志为零的情况下,选择零作为第二选择结果输出至所述第八选择器,否则选择所述第一选择结果作为第二选择结果输出至第八选择器;所述第八选择器用于在所述特殊值标志为非数或无穷的情况下,选择第二预设值作为输入数据的小数部分,否则选择第二选择结果作为输入数据的小数部分。

11、根据本公开的一方面,提供了一种运算方法,所述方法用于提取输入数据的小数部分,所述方法包括:获取所述输入数据的小数掩码,所述小数掩码用于标记所述输入数据的尾数的小数部分;根据所述小数掩码,对所述输入数据的尾数进行位移操作,得到位移位数和位移结果;根据所述小数掩码、所述位移位数和所述位移结果,确定所述输入数据的小数部分。

12、在一种可能的实现方式中,根据所述小数掩码、所述位移位数和所述位移结果,确定所述输入数据的小数部分,包括:根据所述位移结果确定结果尾数,所述结果尾数是用浮点数形式表示所述输入数据的小数部分时的尾数;根据所述位移位数确定结果指数,所述结果指数是用浮点数形式表示所述输入数据的小数部分时的指数;根据所述小数掩码检测所述输入数据的特殊值标志,所述特殊值标志的类别包括无穷、非数、零、纯小数、纯整数;根据所述结果尾数、所述结果指数、所述特殊值标志,确定所述输入数据的小数部分。

13、在一种可能的实现方式中,获取所述输入数据的小数掩码,包括:对所述输入数据的指数部分与第一预设阈值进行比较,得到比较结果;在所述比较结果为所述输入数据的指数部分小于或等于第一预设阈值的情况下,选择所述输入数据的小数掩码为预设位数的全1数据;或者,在所述比较结果为所述输入数据的指数部分大于第一预设阈值的情况下,选择右移数据为所述输入数据的小数掩码,所述右移数据为所述预设位数的全1数据右移第一差值位,所述第一差值为所述输入数据的指数部分与第一预设阈值的差值。

14、在一种可能的实现方式中,根据所述小数掩码,对所述输入数据的尾数进行位移操作,得到位移位数和位移结果,包括:在所述输入数据大于或等于零的情况下,根据所述输入数据的尾数部分与所述小数掩码,获取第一左移位数;根据所述第一左移位数对所述输入数据的尾数执行左移操作,得到左移结果;将所述第一左移位数确定为所述位移位数,将所述左移结果确定为所述位移结果;或者,在所述输入数据小于零且所述输入数据的指数部分大于或等于第一预设阈值的情况下,根据所述输入数据的尾数部分与所述小数掩码,获取第二左移位数;根据所述第二左移位数对所述输入数据的尾数执行左移操作,得到左移结果;将所述第二左移位数确定为所述位移位数,将所述左移结果确定为所述位移结果;或者,在所述输入数据小于零且所述输入数据的指数部分小于第一预设阈值的情况下,根据所述输入数据的指数部分与第二预设阈值的第二差值,获取右移位数;根据所述右移位数,对所述输入数据的尾数部分执行右移操作,得到右移结果,并根据所述右移结果确定粘滞位的值;将所述右移位数确定为所述位移位数,将所述右移结果确定为所述位移结果。

15、在一种可能的实现方式中,根据所述输入数据的尾数部分与所述小数掩码,获取第一左移位数,包括:计算所述输入数据的尾数部分与所述小数掩码的按位与操作,得到按位与结果;从高位至低位检测所述按位与结果,将第一个非零位之前零位的数量确定为第一左移位数;

16、根据所述输入数据的尾数部分与所述小数掩码,获取第二左移位数,包括:计算所述输入数据的尾数部分与取反后的所述小数掩码的按位或操作,得到按位或结果;从高位至低位检测所述按位或结果,将第一个零位之前非零位的数量确定为第二左移位数。

17、在一种可能的实现方式中,根据所述位移结果确定结果尾数,包括:在所述输入数据大于或等于零的情况下,选择所述位移结果作为小数部分的结果尾数;或者,在所述输入数据小于零且所述粘滞位等于一的情况下,将所述位移结果的按位取反结果,作为小数部分的结果尾数;或者,在所述输入数据小于零且所述粘滞位等于零的情况下,将所述位移结果的按位取反结果的加一结果,作为小数部分的结果尾数。

18、在一种可能的实现方式中,根据所述位移位数确定结果指数,包括:在所述输入数据大于或等于零,将所述输入数据的指数部分与所述第一左移位数的减法结果,作为小数部分的结果指数;或者,在所述输入数据小于零且所述输入数据的指数部分大于或等于第一预设阈值的情况下,将所述输入数据的指数部分与所述第二左移位数的减法结果,作为小数部分的结果指数;或者,在所述输入数据小于零且所述输入数据的指数部分小于第一预设阈值的情况下,选择第一预设值作为小数部分的结果指数。

19、在一种可能的实现方式中,根据所述小数掩码检测所述输入数据的特殊值标志,包括:在所述输入数据的尾数部分和指数部分均为零的情况下,将所述特殊值标志确定为零;或者,在所述输入数据的指数部分均为一的情况下,将所述特殊值标志确定为无穷或非数;或者,在所述输入数据的指数部分小于第一预设阈值,将所述特殊值标志确定为纯小数;或者,在所述输入数据的尾数部分与所述小数掩码进行按位与操作的结果为零,且所述输入数据不等于0或非数或无穷的情况下,将所述特殊值标志确定为纯整数。

20、在一种可能的实现方式中,根据所述结果尾数、所述结果指数、所述特殊值标志,确定所述输入数据的小数部分,包括:在所述特殊值标志为非数或无穷的情况下,将第二预设值作为输入数据的小数部分;或者,在所述特殊值标志为零的情况下,将零作为输入数据的小数部分;或者,在所述特殊值标志为纯小数且所述输入数据大于零的情况下,将所述输入数据作为输入数据的小数部分;否则,选择所述输入数据的符号位、所述结果指数、所述结果尾数的拼装结果作为输入数据的小数部分。

21、根据本公开的一方面,提供了一种算术逻辑单元电路,所述算术逻辑单元电路包括乘累加器,第九选择器,以及如上所述的运算装置,所述运算装置与所述乘累加器解耦合,所述第九选择器用于选择所述运算装置的结果或者所述乘累加器的结果。

22、根据本公开的一方面,提供了一种芯片,所述芯片包括如上所述的运算装置或算术逻辑单元电路。

23、根据本公开的一方面,提供了一种电子设备,所述电子设备包括主板以及如上所述的芯片。

24、根据本公开的一方面,提供了一种计算机可读存储介质,其上存储有计算机程序指令,所述计算机程序指令被处理器执行时实现上述方法。

25、本公开实施例的运算装置用于提取输入数据的小数部分,该运算装置包括掩码电路、位移电路、处理电路;掩码电路用于获取输入数据的小数掩码,并将小数掩码输出至位移电路和处理电路,小数掩码用于标记输入数据的尾数的小数部分;位移电路用于根据小数掩码,对输入数据的尾数进行位移操作,得到位移位数和位移结果,并将位移位数和位移结果输出至处理电路;处理电路用于根据小数掩码、位移位数和位移结果,确定输入数据的小数部分。通过本公开实施例的运算装置,可以在使用少量电路开销的情况下,独立实现提取浮点数小数部分的指令的计算,该运算装置与加法器或者乘加器完全解耦合,不占用加法器或者乘加器的计算资源。在处理器芯片中设置该运算装置,缓解了由于将向下取整的结果作为加法器或者乘加器的输入,所导致的加法器或者乘加器的时序紧张,从而提高处理器芯片的频率。

26、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,而非限制本公开。根据下面参考附图对示例性实施例的详细说明,本公开的其它特征及方面将变得清楚。

- 还没有人留言评论。精彩留言会获得点赞!