一种支持DSP处理器的内核屏蔽非法地址的方法及装置与流程

本发明涉及dsp处理器领域,具体涉及一种支持dsp处理器的内核屏蔽非法地址的方法及装置。

背景技术:

1、dsp处理器是一种独特的微处理器,能够快速实现各种数字信号处理算法,应用场景广泛。dsp处理器中,常采用axi总线实现片内多个内核与从设备的互联,根据axi总线协议要求,dsp处理器的内核主设备通过axi总线访问外部从设备时(包括读操作和写操作),外部从设备均需返回一个反馈信号,标志一次读/写访问的结束,但是在遇到从设备发生故障但该从设备已映射地址空间的情况,或者遇到处理器中未被映射的保留地址空间被主设备读/写访问的情况时,dsp内核无法收到反馈信号。

2、在先技术中,为了让dsp处理器的内核解决上述的无响应问题,第一种方式是采用超时软复位机制,设置超时的时钟周期数,即一个总线操作如果在设置的axi时钟周期内没有完成,则被视为总线发生了死锁;然后,及时发出中断请求到中断控制器,并将导致死锁的总线操作信息写入一组寄存器。第二种方式是通过在总线内部增加一个虚拟从设备产生虚拟响应,解决从设备不可见或故障导致的无响应问题,该方法同样需要超时判决过程,但当发生超时无响应时不产生中断及软复位,而是由dummy从设备模拟真实的从设备发出响应信号,以满足axi的传输机制要求。

3、然而,采用上述两种方式,均需要超时判决,增加了系统响应时间,难以满足高实时性系统要求;并且,解决无响应问题时,无效指令仍然按照指令流水线的过程继续执行后续操作,并且执行时脱离了正确执行的位置,发生指令跑飞问题,额外增加了访存指令流水线及总线传输的非必要开销,降低了传输效率。

技术实现思路

1、本发明的目的是提出一种支持dsp处理器的内核屏蔽非法地址的方法及装置,利用非法地址屏蔽寄存器组,分别在取指阶段和预译码阶段对无响应问题的非法地址进行屏蔽,解决的技术问题是:在发生无响应问题的情况下,如何快速屏蔽错误指令,并解决指令跑飞问题,从而保持系统的高实时性、减少传输开销、提高传输效率。

2、采取的技术方案如下:

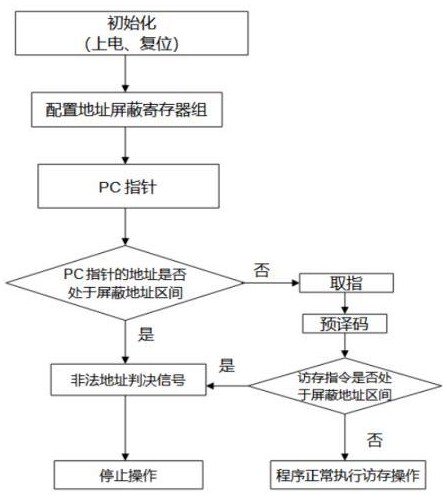

3、第一方面,本发明提出了一种支持dsp处理器的内核屏蔽非法地址的方法,包括如下步骤:

4、s1、将dsp处理器的内核初始化,包括:对dsp处理器的内核进行上电和复位;

5、s2、在dsp处理器的内核中,配置一组非法地址屏蔽寄存器,包括一个起始地址寄存器和一个结束地址寄存器,将起始地址寄存器和结束地址寄存器覆盖的地址范围作为屏蔽地址区间;在dsp处理器的内核中,配置第一比较器和第二比较器,用于对位于屏蔽地址区间的指令发出非法地址判决信号;在dsp处理器的内核中,还配置有第一选通器和第二选通器,用于阻断指令或传输指令;

6、s3、利用pc计数器或转移指令获取pc指针,利用步骤s2中的第一比较器判断pc指针的地址是否位于屏蔽地址区间;若是,则利用第一比较器发出非法地址判决信号,控制第一选通器阻断传输,pc指针停止操作,完成对非法地址的屏蔽;若否,则控制第一选通器传输pc指针,进行预译码操作,所述预译码包括:利用pc指针对程序存储器进行取指,并将取指得到的指令传输到指令预译码器进行预译码,获得访存指令的地址;

7、s4、利用步骤s2中的第二比较器判断步骤s3中访存指令的地址是否位于屏蔽地址区间;若是,则利用第二比较器发出非法地址判决信号,控制第二选通器阻断传输,访存指令停止操作,完成对非法地址的屏蔽;若否,则控制第二选通器传输访存指令,进行译码,并按照译码后的指令内容完成访存操作。

8、利用非法地址寄存器组能够有效屏蔽无响应指令,并且是在取指阶段和译码阶段进行两次非法地址判断,能够尽早的去除无响应指令的不良影响,减少后续的传输开销。

9、优选地,dsp处理器的内核的数量为一个或多个;在dsp处理器的内核的数量为一个时,按照步骤s1~步骤s4对内核进行处理;在dsp处理器的内核的数量为多个时,将每个内核同时按照步骤s1~步骤s4进行处理。dsp处理器的内核数量不固定,通过对每个内核进行两次屏蔽判断,能够有效保证整体的传输效率。

10、优选地,dsp处理器的内核的数量为多个时,若每个内核进行的工作相同,则每个内核中设置的屏蔽地址区间相同;若存在不同的内核进行不同的工作,则对进行不同工作的内核设置不同的屏蔽地址区间。dsp处理器的内核可能会进行相同的工作,也可能会进行不同的工作,并且每个内核接收的外界指令不一定相同,通过对每个内核划分对应的屏蔽地址区间,能够让每个内核准确的完成自身工作。

11、优选地,步骤s2中,屏蔽地址区间包括内核中未被映射的保留地址,以及内核中已映射地址的范围内未被使用的从设备对应的地址。未被映射的保留地址,以及内核中已映射地址的范围内未被使用的从设备对应的地址,这两种非法地址对应的情况均会引发无响应问题,因此将屏蔽地址区间包括这两种方法地址,能够有效的屏蔽掉非法地址,提高传输效率。

12、优选地,步骤s2中,配置一组非法地址屏蔽寄存器的方法为:在dsp处理器的内核中配置两个csr寄存器作为保留项,在需要配置一组非法地址屏蔽寄存器时,将两个csr寄存器分别修改为起始地址寄存器、结束地址寄存器。csr寄存器作为保留项,能够扩展成非法地址寄存器,从而处理中断和异常状况,实现非法地址屏蔽。

13、优选地,步骤s3中,利用pc指针对程序存储器进行取指时,取指的指令数量等于内核在一个时钟周期内支持指令译码的最大数量。取指的指令数量设为内核在一个时钟周期内支持的指令译码的最大数量,能够最快速的完成指令操作,特别是需要多次处理大量数据时,每次取指的指令都是最大数量,能够保证运行的效率最高。

14、第二方面,本发明提出了一种支持dsp处理器的内核屏蔽非法地址的装置,包括:

15、信号输入模块,包括:第一多路复用器、pc计数器、第二多路复用器、控制单元;其中,第一多路复用器接收外界输入指令和控制单元的第一跳转指令,并选择合适的传输路径传输到pc计数器,获得pc指针,第二多路复用器接收pc指针和控制单元的第二跳转指令,并选择合适的传输路径进行传输;

16、非法地址判决模块,包括:第一比较器、第一选通器、程序存储器、指令预译码器、非法地址屏蔽寄存器组、第二比较器和第二选通器;其中,第一比较器接收信号输入模块中第二多路复用器传输的指令并与地址屏蔽寄存器组中的屏蔽地址区间进行对比,在第二多路复用器传输的指令位于屏蔽地址区间时,利用第一比较器发出非法地址判决信号,通知第一选通器阻断指令,在第二多路复用器传输的指令未落入屏蔽地址区间时,第一选通器将传输的指令进行传输,驱使pc指针进行对程序存储器进行取指操作;指令预译码器接收取指操作获得的指令,进行预译码,获得访存指令的地址,利用第二比较器判断访存指令的地址是否位于屏蔽地址区间,若是,第二比较器发出非法地址判决信号,控制第二选通器阻断指令,若否,则第二选通器将访存指令进行传输;

17、译码与执行模块,包括:指令译码器、指令执行单元和对外接口;其中,指令译码器接收非法地址判决模块中第二选通器传输的访存指令,提取出访存指令的内容并传输到指令执行单元进行访存操作,在完成访存操作后通过对外接口进行输出。

18、利用三个模块,实现对传输指令的接收与跳转、屏蔽非法地址,以及译码与执行,使得该装置有效的屏蔽了发生无响应情况时非法地址对传输的影响,并且在取指之前就避免了非法地址对应的指令可能引起的跑飞问题,减少了传输开销,提升了传输的效率。

19、优选地,dsp处理器的内核的数量为一个或多个;在dsp处理器的内核的数量为一个时,按照权利要求7中的信号输入模块、非法地址判决模块、译码与执行模块对内核进行设置;在dsp处理器的内核的数量为多个时,按照权利要求7中的信号输入模块、非法地址判决模块、译码与执行模块对每个内核进行设置。每个内核设置相同的模块,使得每个内核均能够及时屏蔽非法地址,既保证了每个内核的传输效率和准确性,也保证了整个dsp处理器的传输效率和准确性。

20、优选地,非法地址判决模块中,非法地址屏蔽寄存器组是由两个csr寄存器扩展为起始地址寄存器和结束地址寄存器,起始地址寄存器和结束地址寄存器覆盖的地址范围为屏蔽地址区间。扩展csr寄存器为非法地址屏蔽寄存器组,能够在遇到无响应问题时,有效的进行异常和中断的处理,及时屏蔽掉非法地址,保护传输的效率。

21、本发明与现有技术相比具有的有益效果如下:

22、本发明利用非法地址屏蔽寄存器组分别在取指操作之前以及预译码阶段进行两次非法地址判断,能够在发生无响应问题时,快速的屏蔽掉非法地址的影响,减少了非法地址对应的无效指令在后续的操作过程,避免出现指令跑飞问题;并且,本发明无需进行超时判决,不会增加系统响应时间,能够满足系统的高实时性要求。

- 还没有人留言评论。精彩留言会获得点赞!