用于存算一体的操作原语生成方法和存算一体逻辑电路

本发明属于微电子器件及电路领域,更具体地,涉及用于存算一体的操作原语生成方法和存算一体逻辑电路。

背景技术:

1、在云端大模型中经常会出现一些各类型的复杂运算,常见的有矩阵向量乘法、注意力机制、相似性搜索、集合运算等。存算一体电路往往用于对矩阵向量乘法进行并行计算,然而当遇到非矩阵乘法运算时,需要将数据搬移到其余处理器上进行运算。如果存算一体电路本身可根据需要配置为相应的运算核,则会带来非常高的灵活性,而且可以利用其天然的并行性对其余运算进行加速,从而带来整体性能的提升。当前还没有专利和文献针对存算一体电路进行操作原语及其电路架构层面的分析和研究。

技术实现思路

1、针对现有技术的缺陷,本发明的目的在于提供用于存算一体的操作原语生成方法和存算一体逻辑电路,旨在解决现有技术存算一体电路进行操作原语及其电路架构的空白的问题。

2、为实现上述目的,第一方面,本发明提供了一种用于存算一体的操作原语生成方法,包括:

3、接收对读指令和写指令的标记位的指定;

4、接收对各种双目布尔逻辑运算的4位运算指令码的指定;

5、接收对数据码编码方式的指定;

6、按照上述指定,生成操作原语,所述操作原语由指令码和数据码构成,所述指令码由读/写标记位和4位运算指令码构成。

7、优选地,所述双目布尔逻辑运算,分别是and、nand、or、nor、xor、xnor、imp、nimp、r-imp和r-nimp。

8、为实现上述目的,第二方面,本发明提供了一种数据-指令译码器,包括:

9、信号源,用于提供两路信号,分别为读电压和写电压;

10、译码逻辑电路,用于接收操作原语中数据码y和4位运算指令码,生成逻辑电压ya和yb;

11、第一两通道模拟开关,输入端分别接读电压和写电压,控制端接操作原语中读/写标记位;

12、第二两通道模拟开关,输入端分别接第一两通道模拟开关输出端和地电压,控制端接逻辑电压ya,输出工作电压ya;

13、第三两通道模拟开关,输入端分别接第一两通道模拟开关输出端和地电压,控制端接逻辑电压yb,输出工作电压yb;

14、所述操作原语采用如第一方面所述的方法生成。

15、优选地,若采用ya=y的编码模式时,y=0时,(ya,yb)=(0,1),y=1时,(ya,yb)=(1,0),若采用yb=y的模式,y=0时,(ya,yb)=(1,0),y=1时,(ya,yb)=(0,1)。

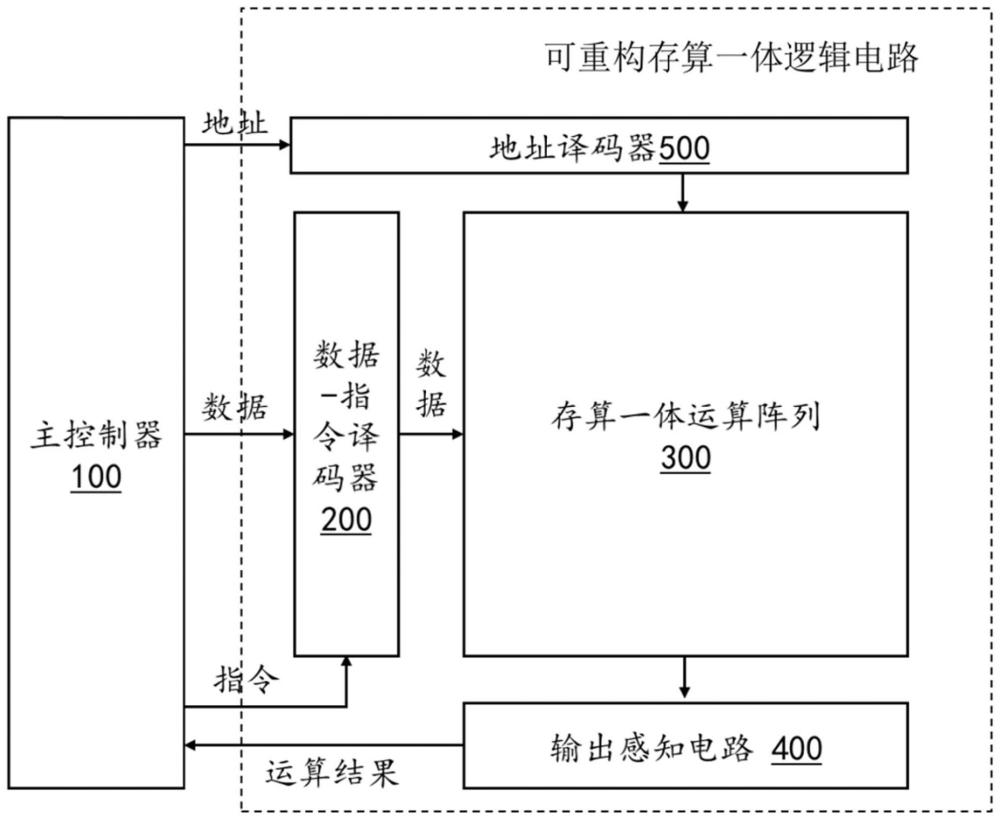

16、为实现上述目的,第三方面,本发明提供了一种可重构存算一体逻辑电路,包括:

17、地址译码器,用于接收主控制器发送的地址信号,将地址信号译码为开关信号,输出控制信号至存算一体运算阵列,以激活存算一体运算阵列中对应的区域;

18、如第二方面所述的数据-指令译码器,用于接收主控制器发送的运算对象和操作指令,根据操作指令的类型,将数据编码为不同的格式,输出至存算一体运算阵列;

19、存算一体运算阵列,用于接收数据-指令译码器的输入数据,由激活区域执行计算,输出计算结果对应的工作电压/电流给输出感知电路;

20、输出感知电路,用于将存算一体运算阵列的输出转换为数字信号,作为最终运算结果发送给主控制器。

21、优选地,执行的运算的两个运算对象分别为x和y,其中,y在计算开始之前通过写指令载入存算一体运算阵列中,x和操作指令再一起通过读指令载入存算一体运算阵列中,以实现相应运算。

22、优选地,在除静态随机存储器之外的其余类型存储器中,需要两个单元映射一个数,分别为ya和yb,且必须满足yb=~ya,有两种编码方式,ya=y,或yb=y,在静态随机存储器中,只需一个单元即可。

23、优选地,所述输出感知电路为灵敏放大器或者模数转换器。

24、优选地,所述电路有两种运算模式,分别为标量运算模式和矢量运算模式,其中,

25、标量运算模式下,运算对象x和y均为1比特数据,执行的是两者之间的布尔逻辑运算;

26、矢量运算模式下,运算对象x和y为矢量或矩阵,执行的是某一种逻辑的累加运算。

27、优选地,还包括:

28、位于数据-指令译码器和存算一体运算阵列之间的移位寄存器,用于在矢量运算模式下,保存数据-指令译码器的每次逻辑运算结果,将结果累加输出至存算一体运算阵列。

29、总体而言,通过本发明所构思的以上技术方案与现有技术相比,具有以下有益效果:

30、本发明提供用于存算一体的操作原语生成方法和存算一体逻辑电路,抽象出基础的操作原语和操作指令,指导存算一体电路设计,降低电路设计的复杂度;通过挖掘存储器自身的逻辑特性,集合双比特映射方法,在不改变电路结构的情况下,实现十种完整地双目逻辑函数,提高存算一体电路的灵活性和可配置性,以此来适配各类复杂的计算需求,同时本发明提出的存算一体操作原语适用于各类存储介质,使得基于不同存储介质的存算一体电路均可共用一套编译系统,大程度降低了软硬件衔接的难度以及编译难度。

技术特征:

1.一种用于存算一体的操作原语生成方法,其特征在于,包括:

2.如权利要求1所述的方法,其特征在于,所述双目布尔逻辑运算,分别是and、nand、or、nor、xor、xnor、imp、nimp、r-imp和r-nimp。

3.一种数据-指令译码器,其特征在于,包括:

4.如权利要求3所述的译码器,其特征在于,若采用ya=y的编码模式时,y=0时,(ya,yb)=(0,1),y=1时,(ya,yb)=(1,0),若采用yb=y的模式,y=0时,(ya,yb)=(1,0),y=1时,(ya,yb)=(0,1)。

5.一种可重构存算一体逻辑电路,其特征在于,包括:

6.如权利要求5所述的电路,其特征在于,执行的运算的两个运算对象分别为x和y,其中,y在计算开始之前通过写指令载入存算一体运算阵列中,x和操作指令再一起通过读指令载入存算一体运算阵列中,以实现相应运算。

7.如权利要求5所述的电路,其特征在于,在除静态随机存储器之外的其余类型存储器中,需要两个单元映射一个数,分别为ya和yb,且必须满足yb=~ya,有两种编码方式,ya=y,或yb=y,在静态随机存储器中,只需一个单元即可。

8.如权利要求5所述的电路,其特征在于,所述输出感知电路为灵敏放大器或者模数转换器。

9.如权利要求5所述的电路,其特征在于,所述电路有两种运算模式,分别为标量运算模式和矢量运算模式,其中,

10.如权利要求5所述的电路,其特征在于,还包括:

技术总结

本发明公开用于存算一体的操作原语生成方法和存算一体逻辑电路,属于微电子器件领域。包括:地址译码器,用于接收主控制器发送的地址信号,译码为开关信号,输出控制信号至存算一体运算阵列,以激活对应区域;数据‑指令译码器,用于接收主控制器发送的运算对象和操作指令,将数据编码为不同的格式,输出至存算一体运算阵列;存算一体运算阵列,用于由激活区域执行计算,输出计算结果对应的工作电压/电流给输出感知电路;输出感知电路,用于将工作电压/电流转换为数字信号,发送给主控制器。本发明抽象出基础的操作原语和操作指令,指导存算一体电路设计,降低电路设计复杂度;提高存算一体电路的灵活性和可配置性,以适配各类复杂的计算需求。

技术研发人员:李祎,杨岭,缪向水

受保护的技术使用者:华中科技大学

技术研发日:

技术公布日:2024/4/8

- 还没有人留言评论。精彩留言会获得点赞!