一种基于FPGA的信号处理电路的制作方法

本技术属于fpga信号处理,具体涉及一种基于fpga的信号处理电路。

背景技术:

1、fpga(field programmable gate array)是在pal(可编程阵列逻辑)、gal(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(asic)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

2、现有的fpga在实际应用中没有配套通用的相关信号处理电路,从而使得每次在运用到具体领域时,均需重新设置,这无疑是低效率和增加成本。

3、因此,针对上述问题,予以进一步改进。

技术实现思路

1、本实用新型的主要目的在于提供一种基于fpga的信号处理电路,其通过时钟产生模块、dsp模块、flash模块、eeprom模块和接口模块在fpga模块对应的功能区域进行通用设置,从而在后期使用过程中具有效率高、成本低和实用性高等优点。

2、为达到以上目的,本实用新型提供一种基于fpga的信号处理电路,包括fpga模块、时钟产生模块(用于产生时钟信号)和dsp模块(用于数字信号处理),所述时钟产生模块和所述dsp模块分别与所述fpga模块电性连接,其中:

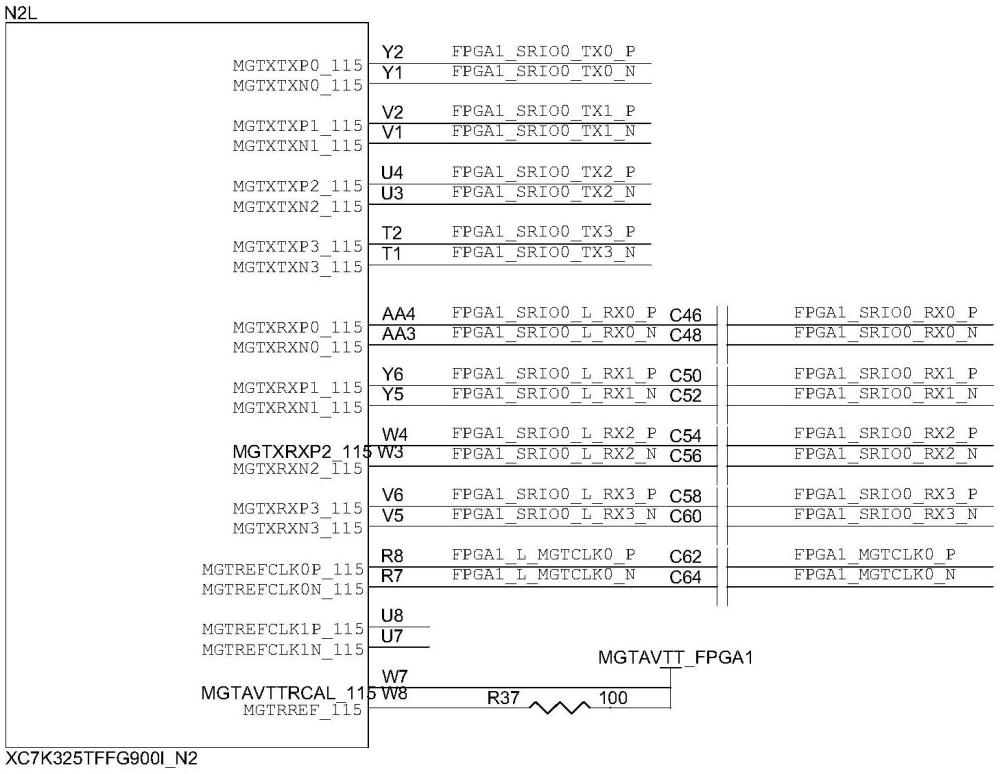

3、所述pfga模块包括芯片n2l、芯片n2m、芯片n2n和芯片n2o(上述4个芯片实际为一个整体芯片);

4、所述时钟产生模块包括时钟发生器n38和缓冲器n41,所述时钟发生器n38的17管脚通过电容c62与所述芯片n2l的r8端电性连接并且所述时钟发生器n38的16管脚通过电容c64与所述芯片n2l的r7端电性连接,所述时钟发生器n38的20管脚通过电容c63与所述芯片n2o的c8端电性连接并且所述时钟发生器n38的21管脚通过电容c65与所述芯片n2o的c7端电性连接,所述时钟发生器n38的23管脚通过电容c81与所述芯片n2n的g8端电性连接并且所述时钟发生器n38的22管脚通过电容c83与所述芯片n2n的g7端电性连接;所述时钟发生器n38的29管脚与所述缓冲器n41的7管脚电性连接并且所述时钟发生器n38的28管脚与所述缓冲器n41的6管脚电性连接;

5、所述dsp模块包括芯片n22i,所述芯片n22i的aj12端通过电容c267与所述芯片n2l的y2端电性连接并且所述芯片n22i的aj11端通过电容c269与所述芯片n2l的y1端电性连接,所述芯片n22i的ah11端通过电容c271与所述芯片n2l的v2端电性连接并且所述芯片n22i的ah10端通过电容c272与所述芯片n2l的v1端电性连接,所述芯片n22i的ah13端通过电容c273与所述芯片n2l的u4端电性连接并且所述芯片n22i的ah14端通过电容c274与所述芯片n2l的u3端电性连接,所述芯片n22i的aj14端通过电容c275与所述芯片n2l的t2端电性连接并且所述芯片n22i的aj15端通过电容c276与所述芯片n2l的t1端电性连接;所述芯片n22i的af11端通过电容c46与所述芯片n2l的aa4端电性连接并且所述芯片n22i的af10端通过电容c48与所述芯片n2l的aa3端电性连接,所述芯片n22i的ag12端通过电容c50与所述芯片n2l的y6端电性连接并且所述芯片n22i的ag11端通过电容c52与所述芯片n2l的y5端电性连接,所述芯片n22i的ag14端通过电容c54与所述芯片n2l的w4端电性连接并且所述芯片n22i的ag15端通过电容c56与所述芯片n2l的w3端电性连接,所述芯片n22i的af13端通过电容c62与所述芯片n2l的r8端电性连接并且所述芯片n22i的af14端通过电容c64与所述芯片n2l的r7端电性连接。

6、作为上述技术方案的进一步优选的技术方案,基于fpga的信号处理电路还包括flash模块,所述flash模块包括存储器n26,所述dsp模块还包括芯片n22h,其中:

7、所述存储器n26的7管脚通过电阻152与所述芯片n22h的ag1电性连接,所述存储器n26的8管脚通过电阻162与所述芯片n22h的ad2电性连接,所述存储器n26的16管脚通过电阻153与所述芯片n22h的ae1电性连接,所述存储器n26的15管脚通过电阻154与所述芯片n22h的ab1电性连接。

8、作为上述技术方案的进一步优选的技术方案,基于fpga的信号处理电路还包括eeprom模块,所述eeprom模块包括存储器n27,其中:

9、所述存储器n27的6管脚与所述芯片n22h的ad3管脚电性连接,所述存储器n27的5管脚与所述芯片n22h的ac4管脚电性连接。

10、作为上述技术方案的进一步优选的技术方案,所述存储器n26的9管脚通过电阻r163连接电源端。

11、作为上述技术方案的进一步优选的技术方案,所述存储器n27的2管脚、3管脚和4管脚均接地。

技术特征:

1.一种基于fpga的信号处理电路,其特征在于,包括fpga模块、时钟产生模块和dsp模块,所述时钟产生模块和所述dsp模块分别与所述fpga模块电性连接,其中:

2.根据权利要求1所述的一种基于fpga的信号处理电路,其特征在于,基于fpga的信号处理电路还包括flash模块,所述flash模块包括存储器n26,所述dsp模块还包括芯片n22h,其中:

3.根据权利要求2所述的一种基于fpga的信号处理电路,其特征在于,基于fpga的信号处理电路还包括eeprom模块,所述eeprom模块包括存储器n27,其中:

4.根据权利要求3所述的一种基于fpga的信号处理电路,其特征在于,所述存储器n26的9管脚通过电阻r163连接电源端。

5.根据权利要求4所述的一种基于fpga的信号处理电路,其特征在于,所述存储器n27的2管脚、3管脚和4管脚均接地。

技术总结

本技术公开了一种基于FPGA的信号处理电路,包括FPGA模块、时钟产生模块和DSP模块,所述时钟产生模块和所述DSP模块分别与所述FPGA模块电性连接,所述PFGA模块包括芯片N2L、芯片N2M、芯片N2N和芯片N2O;所述时钟产生模块包括时钟发生器N38和缓冲器N41,所述时钟发生器N38的17管脚通过电容C62与所述芯片N2L的R8端电性连接并且所述时钟发生器N38的16管脚通过电容C64与所述芯片N2L的R7端电性连接。本技术公开的一种基于FPGA的信号处理电路,其通过时钟产生模块、DSP模块、FLASH模块、EEPROM模块和接口模块在FPGA模块对应的功能区域进行通用设置,从而在后期使用过程中具有效率高、成本低和实用性高等优点。

技术研发人员:邵乐天,张峻涛,王文勇

受保护的技术使用者:浙江天泓波控电子科技有限公司

技术研发日:20230828

技术公布日:2024/2/25

- 还没有人留言评论。精彩留言会获得点赞!