电路的混合逻辑综合优化方法、装置及电子设备与流程

本技术涉及电路,尤其是涉及一种电路的混合逻辑综合优化方法、装置及电子设备。

背景技术:

1、在数字集成电路设计流程的逻辑综合中,会将电路的rtl级硬件描述语言转换成一种或多种通用的图结构的逻辑表示方式,目前学术界常用的逻辑表示方式有与非图(and-inverter graph, aig)、多数非图(majority-inverter graph, mig)、异或与图(xor-and graph, xag)和异或多数图(xor-majority graph, xmg)等,再使用其中一种表示方式对应的优化方法对电路进行优化。很少会将一块电路使用多种表示方式进行表示,再进行优化。该发明就是一种混合表示方式的逻辑综合优化方法。

2、目前常见的一种混合逻辑综合方法,是首先对电路进行分区,然后对分区的子电路采用不同的逻辑表示方式,分别对分区电路进行优化,最终合并优化后的子电路。该方法中,分区的方式是使用一种固定的分区方法,即,按照预设数量的节点数对电路进行分区,没有根据实际电路的尺寸来动态计算分区的大小;没有对感兴趣的那部分电路做出区别;没有感知电路深度,并没有特别关注关键路径,可能会破坏关键路径的完整性,导致丧失了对关键路径独特优化的机会。

技术实现思路

1、本技术的目的在于提供一种电路的混合逻辑综合优化方法、装置及电子设备,基于电路的大小和深度,自适应确定平均分区大小,以及确定多个主输出节点分别对应的关键路径节点集,然后基于关键路径节点集和平均分区大小,进行电路中的关键路径分区,再次分区后对各分区电路进行优化处理,可以提高电路整体的优化效果。

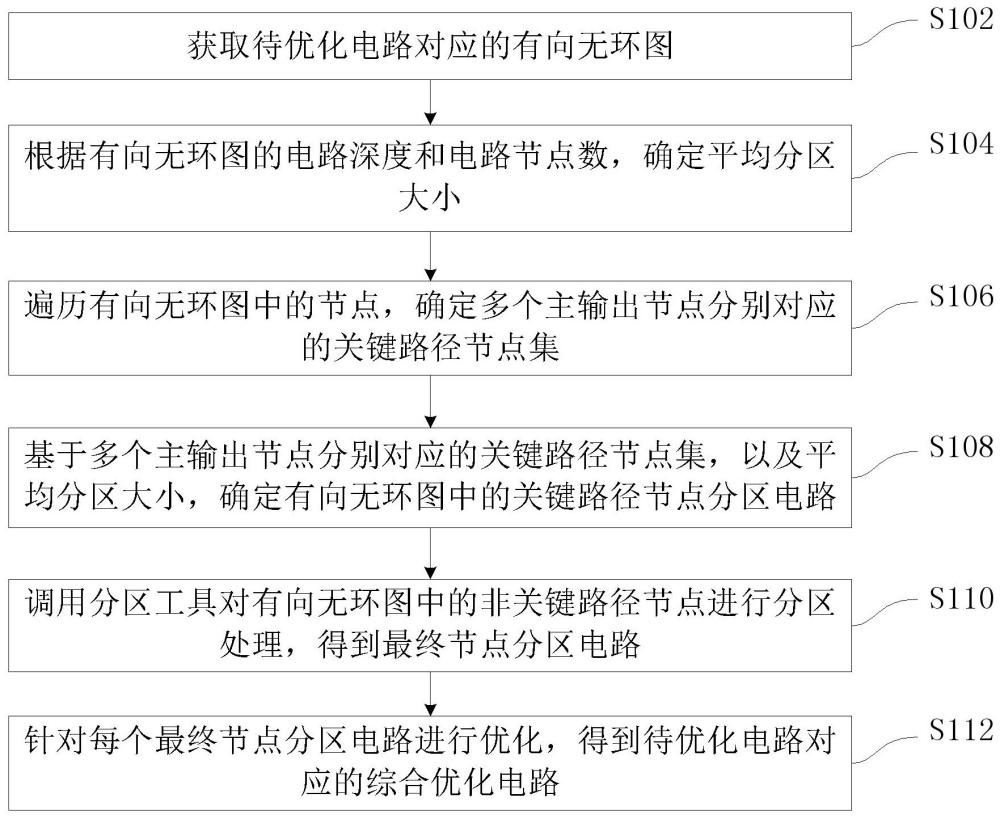

2、第一方面,本技术提供一种电路的混合逻辑综合优化方法,方法包括:获取待优化电路对应的有向无环图;待优化电路为rtl级verilog网表;有向无环图为对待优化电路进行目标逻辑表示转换得到的;根据有向无环图的电路深度和电路节点数,确定平均分区大小;遍历有向无环图中的节点,确定多个主输出节点分别对应的关键路径节点集;基于多个主输出节点分别对应的关键路径节点集,以及平均分区大小,确定有向无环图中的关键路径节点分区电路;调用分区工具对有向无环图中的非关键路径节点进行分区处理,得到最终节点分区电路;针对每个最终节点分区电路进行优化,得到待优化电路对应的综合优化电路。

3、进一步地,上述根据有向无环图的电路深度和电路节点数,确定平均分区大小的步骤,包括:判断电路节点数是否大于预设分区大小的两倍;如果是,将预设分区大小和电路深度中的最大值作为平均分区大小;如果否,将电路深度和1/5的电路节点数中的最大值作为平均分区大小。

4、进一步地,上述遍历有向无环图中的节点,确定多个主输出节点分别对应的关键路径节点集的步骤,包括:以第一个主输出节点为当前输出节点,执行以下层级判断步骤:判断当前输出节点对应的层级是否等于电路深度;如果否,以下一个主输出节点作为当前输出节点,继续执行层级判断步骤;如果是,将当前输出节点作为当前节点,执行以下遍历查找步骤:从当前节点对应的多个扇入节点中,查找满足条件的目标扇入节点;将目标扇入节点作为当前节点,继续执行遍历查找步骤,直到遍历至主输入节点,基于当前输出节点和对应查找到的所有目标扇入节点,确定当前输出节点对应的关键路径节点集。

5、进一步地,上述从当前节点对应的多个扇入节点中,查找满足条件的目标扇入节点的步骤,包括:将将当前节点对应的多个扇入节点中,层级与当前节点的层级相差为1的扇入节点,确定为目标扇入节点;或者,将当前节点对应的多个扇入节点中,时序裕度最小的扇入节点,确定为目标扇入节点。

6、进一步地,上述各节点对应的时序裕度的计算过程如下:获取待优化电路对应的设计约束文件;根据设计约束文件中的输入延时和输出延时,确定各主输入节点分别对应的到达时间,和各主输出节点分别对应的需求时间;从主输入节点到主输出节点方向依次遍历各节点,针对每个当前节点,根据当前节点对应的多个扇入节点分别对应的到达时间,分别计算当前节点的到达时间;将基于多个扇入节点计算出的多个到达时间中的最大到达时间,确定为当前节点的到达时间;从主输出节点到主输入节点方向依次遍历各节点,针对每个当前节点,根据当前节点对应的多个扇出节点分别对应的需求时间,分别计算当前节点的需求时间;将基于多个扇出节点计算出的多个需求时间中的最小需求时间,确定为当前节点的需求时间;针对每个节点,求取节点分别对应的需求时间和到达时间之间的差值,得到节点对应的时序裕度。

7、进一步地,上述基于当前输出节点和对应查找到的所有目标扇入节点,确定当前输出节点对应的关键路径节点集的步骤,包括:如果当前输出节点为第一个主输出节点,将当前输出节点和对应查找到的所有目标扇入节点构成的集合,确定为当前输出节点对应的关键路径节点集;如果当前输出节点不是第一个主输出节点,将当前输出节点和对应查找到的所有目标扇入节点,去除掉与已经确定出的关键路径节点中重复的节点后的集合,确定为当前输出节点对应的关键路径节点集。

8、进一步地,上述基于多个主输出节点分别对应的关键路径节点集,以及平均分区大小,确定有向无环图中的关键路径节点分区电路的步骤,包括:将多个所述主输出节点中的第一个主输出节点对应的关键路径节点集作为当前节点集,执行以下节点判断步骤:判断所述当前节点集是否为最后一个节点集;如果是,将所述当前节点集确定为一个关键路径分区电路;如果否,执行以下节点数量判断步骤:判断所述当前节点集中的节点数量是否不小于所述平均分区大小;如果不小于,将所述当前节点集确定为一个关键路径节点分区电路;继续将下一个主输出节点对应的关键路径节点集重新作为所述当前节点集,继续执行所述节点判断步骤;如果小于,将所述当前节点集,与下一个主输出节点对应的关键路径节点集进行合并;将合并后的节点集重新作为所述当前节点集,继续执行所述节点判断步骤,直到遍历完所有主输出节点对应的关键路径节点集。

9、进一步地,上述针对每个最终节点分区电路进行优化,得到待优化电路对应的综合优化电路的步骤,包括:针对每个最终节点分区电路,采用多种逻辑表示方式对最终节点分区电路进行表示,针对每种逻辑表示方式,进行不同的工艺无关的优化处理,针对每种优化处理的结果作工艺映射,提取工艺映射后的电路的相关信息,确定最佳优化方式;相关信息包括:电路时延信息和/或电路面积信息;将每个最终节点分区电路对应的最佳优化方式下的优化结果进行合并,得到综合优化电路。

10、第二方面,本技术还提供一种电路的混合逻辑综合优化装置,装置包括:节点图获取模块,用于获取待优化电路对应的有向无环图;待优化电路为rtl级verilog网表;有向无环图为对待优化电路进行目标逻辑表示转换得到的;分区大小确定模块,用于根据有向无环图的电路深度和电路节点数,确定平均分区大小;关键节点确定模块,用于遍历有向无环图中的节点,确定多个主输出节点分别对应的关键路径节点集;第一分区模块,用于基于多个主输出节点分别对应的关键路径节点集,以及平均分区大小,确定有向无环图中的关键路径节点分区电路;第二分区模块,用于调用分区工具对有向无环图中的非关键路径节点进行分区处理,得到最终节点分区电路;优化模块,用于针对每个最终节点分区电路进行优化,得到待优化电路对应的综合优化电路。

11、第三方面,本技术还提供一种电子设备,包括处理器和存储器,存储器存储有能够被处理器执行的计算机可执行指令,处理器执行计算机可执行指令以实现上述第一方面所述的方法。

12、第四方面,本技术还提供一种计算机可读存储介质,计算机可读存储介质存储有计算机可执行指令,计算机可执行指令在被处理器调用和执行时,计算机可执行指令促使处理器实现上述第一方面所述的方法。

13、本技术提供的电路的混合逻辑综合优化方法、装置及电子设备中,首先获取待优化电路对应的有向无环图;待优化电路为rtl级verilog网表;有向无环图为对待优化电路进行目标逻辑表示转换得到的;根据有向无环图的电路深度和电路节点数,确定平均分区大小;遍历有向无环图中的节点,确定多个主输出节点分别对应的关键路径节点集;基于多个主输出节点分别对应的关键路径节点集,以及平均分区大小,确定有向无环图中的关键路径节点分区电路;调用分区工具对有向无环图中的非关键路径节点进行分区处理,得到最终节点分区电路;针对每个最终节点分区电路进行优化,得到待优化电路对应的综合优化电路。该方式中,基于电路的大小和深度,自适应确定平均分区大小,以及确定多个主输出节点分别对应的关键路径节点集,然后基于关键路径节点集和平均分区大小,进行电路中的关键路径分区,再次分区后对各分区电路进行优化处理,可以提高电路整体的优化效果。

- 还没有人留言评论。精彩留言会获得点赞!