一种总线性能监测的方法和装置与流程

本发明涉及性能监测领域,特别是涉及一种总线性能监测的方法和装置。

背景技术:

1、在现有soc(system on chip,简写为soc)芯片设计中,通常会进行多个不同功能的知识产权(intellectual property,简写为ip)模块的集成,各类功能的ip之间通过总线连接,因此,总线性能是影响整个soc系统性能的关键因素。在soc的硅后验证过程中,ip之间协同工作过程中可能会存在因总线卡死、总线延迟太大和总线带宽不够等情况,导致系统性能无法满足设计需求,因此硅后测试中需要包含总线性能监测。

2、在硅后验证的过程中,对于总线中存在的故障或问题定位手段非常局限。目前关于硅后验证的总线性能监测的实现技术方法有:

3、1、将芯片的内部逻辑信号通过引脚信号引出。缺陷:芯片的引脚数量有限,总线的信号数量一般较大,并且总线信号的频率较高,而芯片引脚支持的频率一般较低,无法直接将高频信号直接引出。因此,在不影响芯片正常功能的前提下通过观察将总线逻辑信号从芯片引脚引出很难完全监测到总线信息。

4、2、只监测总线的平均传输效率以及一段时间内的系统总线的数据流量。缺陷:只能监测到平均传输效率和一段时间内的数据传输总量,对总线延时等信息没有相关记录,而总线延迟也是总线性能的关键指标之一。

5、鉴于此,如何克服现有技术所存在的缺陷,解决现有的硅后验证过程中总线性能监测不便的现象,是本技术领域待解决的问题。

技术实现思路

1、针对现有技术的以上缺陷或改进需求,本发明解决了硅后验证过程中总线性能监测不便的问题。

2、本发明实施例采用如下技术方案:

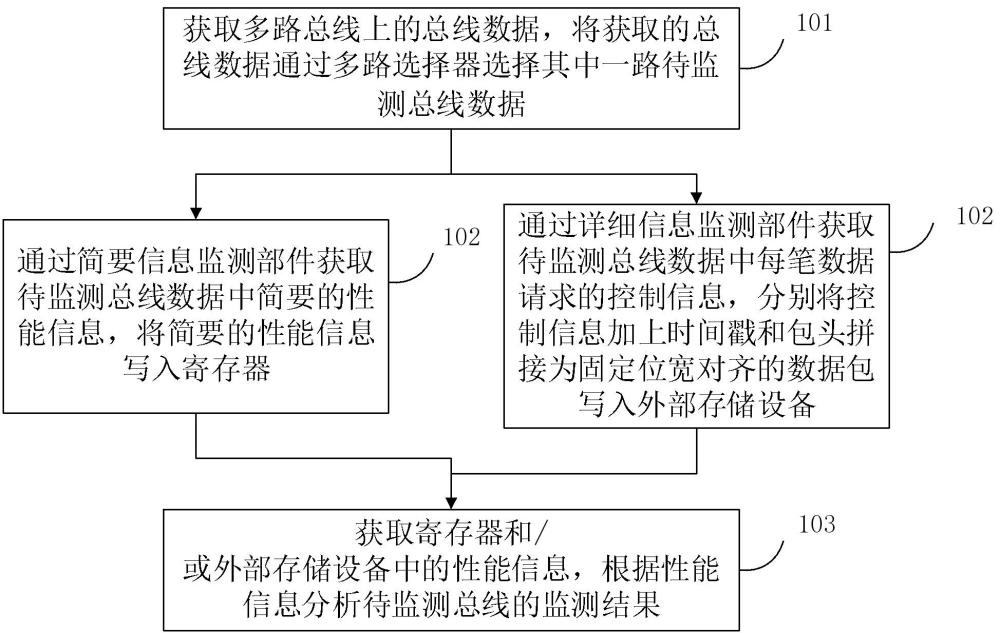

3、第一方面,本发明提供了一种总线性能监测的方法,具体为:获取多路总线上的总线数据,将获取的总线数据通过多路选择器选择其中一路待监测总线数据;通过简要信息监测部件获取待监测总线数据中简要的性能信息,将简要的性能信息写入寄存器,和/或,通过详细信息监测部件获取待监测总线数据中每笔数据请求的控制信息,分别将控制信息加上时间戳和包头拼接为固定位宽对齐的数据包写入外部存储设备;获取寄存器和/或外部存储设备中的性能信息,根据性能信息分析待监测总线的监测结果。

4、优选的,所述通过简要信息监测部件获取待监测总线数据中简要的性能信息,具体包括:当简要信息监测部件监测到待监测总线上的数据请求时,根据配置的数据请求的数量进行相应次数的数据传输监测计算平均延时,同时实时更新总线传输的最大时延和最小时延,监测每次数据传输时的待监测数据,根据所有数据传输的待监测数据计算待监测总线的简要的性能信息。

5、优选的,所述通过详细信息监测部件获取待监测总线数据中每笔数据请求的控制信息,分别将控制信息加上时间戳和包头拼接为固定位宽对齐的数据包,具体包括:获取待监测总线数据中的待监测数据,将每个获取到的待监测数据和该待监测数据的时间戳信息并加上包头按照指定格式打包,生成第一位宽的第一数据包,对第一数据包进行第一次数据缓存;获取第一次数据缓存的第一数据包,提取第一数据包中有效的待监测数据,根据通道有效标志和第一数据包的指定格式对第一数据包进行有效数据提取,将提取后的有效数据按照指定位宽对齐后,拼接成第二位宽的第二数据包,对第二数据包进行第二次缓存,将缓存的第二数据包作为拼接后的数据包。

6、优选的,所述获取待监测总线数据中的待监测数据,将每个获取到的待监测数据和该待监测数据的时间戳信息并加上包头按照指定格式打包,生成第一位宽的第一数据包,还包括:获取待监测总线的每个通道中的待监测数据,将一个通道中同一时间戳的待监测数据按照指定顺序组成该通道相应时间戳的数据包,并将同一时间戳的数据包和相应的时间戳进行绑定,再将所有通道中绑定了同一时间戳的数据包按照通道顺序加上通道有效标志组成该时间戳的第一数据包。

7、优选的,当相应时间戳的待监测数据中存在一个或多个无效的待监测数据时,所述将一个通道中同一时间戳的待监测数据按照指定顺序组成该通道相应时间戳的数据包,具体包括:将无效通道的待监测数据使用相应位宽的0进行填充,再将填充后的待监测数据组成数据包。

8、优选的,所述根据通道有效标志和第一数据包的指定格式对第一数据包进行有效数据提取,将提取后的有效数据按照指定位宽对齐后,具体包括:根据第一数据包的通道有效标志的值确定监测的有效通道,根据有效通道的待监测数据确定第一数据包的有效监测数据长度,对有效监测数据提取后使其按照指定位宽对齐得到有效数据包。

9、优选的,使用详细信息监测部件时,所述根据监测信息分析待监测总线的监测结果,具体包括:由获取到的第一个有效数据包开始,获取当前有效数据包的通道有效标志中每个比特位的值,以及每个比特位对应通道的待监测数据的数据长度;根据待监测数据的数据长度获取当前有效数据包中的每个待监测数据,根据通道有效标志中对应的位置获取对应通道的监测信息;根据比特位的值和相应通道待监测数据的长度计算当前有效数据包的长度,根据当前有效数据包的长度获取下一个当前有效数据包,直至获取到所需分析的全部有效数据包,根据获取到的全部有效数据包中的待监测信息分析待监测总线的性能监测结果。

10、另一方面,本发明提供了一种总线性能监测的装置,具体为:包括:寄存器、多路选择器、简要信息监测部件和详细信息监测部件,用于实现第一方面提供的总线性能监测的方法,具体的:寄存器用于保存外部配置信息,以及简要信息监测部件所获取到的性能信息;多路选择器用于获取外部待监测总线数据中需要监测的一路或多路总线数据,将获取的总线数据发送至被选择的简要信息监测部件和/或详细信息监测部件;简要信息监测部件用于根据获取的总线数据和外部配置信息获取简要的性能信息,并将简要的性能信息写入寄存器;详细信息监测部件用于根据获取的总线数据和外部配置信息获取详细的性能信息,并将详细的监测信息写入外部的存储设备。

11、优选的,所述简要信息监测部件包括:读数据简要信息监测模块和写数据简要信息监测模块;读数据简要信息监测模块监测到外部待监测总线数据中的读数据行为时,用于计算获取的总线数据中简要的性能信息;写数据简要信息监测模块监测到外部待监测总线数据中的写数据行为时,用于计算获取的总线数据中简要的性能信息。

12、优选的,所述详细信息监测部件包括:组包模块、数据处理及缓存模块和写存储模块,具体包括:组包模块由获取的总线数据中获取需要监测的数据,并将待监测数据打包固定长度的第一位宽的第一数据包;数据处理及缓存模块将第一数据包进行有效数据提取,并按照指定位宽对齐后,按照第二位宽进行拼接缓存,直至缓存的数据量满足配置的要求或者超时的条件时,则开始将数据传输到写存储模块当中;写存储模块用于将第二数据包作为详细的监测信息写入外部存储设备中。

13、与现有技术相比,本发明提供的装置有益效果在于:在芯片设计前期在装置中加入总线性能监测的设计,通过性能监测装置提前预埋芯片总线可观测的手段,通过多路选择器选择性的观测不同总线通道的传输性能,通过简要信息监测部件和详细信息监测部件获取总线数据中不同的性能数据,通过寄存器或外部的存储设备保存获取到的性能数据,实现硅后验证中各种总线性能数据的监测。

- 还没有人留言评论。精彩留言会获得点赞!