一种时钟发生器、参数调整方法、系统、装置及介质与流程

本发明涉及时钟领域,特别涉及一种时钟发生器、参数调整方法、系统、装置及介质。

背景技术:

1、在当前各服务器厂商竞品cpu(central processing unit,中央处理器)方案一致的情况下,提升cpu性能成为增强服务器产品竞争力的关键。在这种情况下,最直接有效的办法是提升cpu的运行频率,即对cpu进行超频使用。然而,当前平台cpu搭配的标准化时钟发生器芯片只能输出固定的标准频点,无法根据需求对cpu时钟进行适度调节以提升cpu的性能。

2、由于现有的标准化时钟发生器芯片无法灵活调节输出频率,无法在允许范围内对输出频率进行调整以满足服务器超频应用等用户定制化需求,限制了对cpu性能的灵活提升,限制了服务器产品在竞争中发挥更大的优势。

技术实现思路

1、本发明的目的是提供一种时钟发生器、参数调整方法、系统、装置及介质,通过允许用户调节分频系数,并根据用户的需求进行频率调整,从而将其应用于cpu时,实现了对cpu时钟进行灵活调节以提升cpu的性能,可以满足服务器超频应用等用户定制化需求,以提升服务器产品在竞争中的优势。

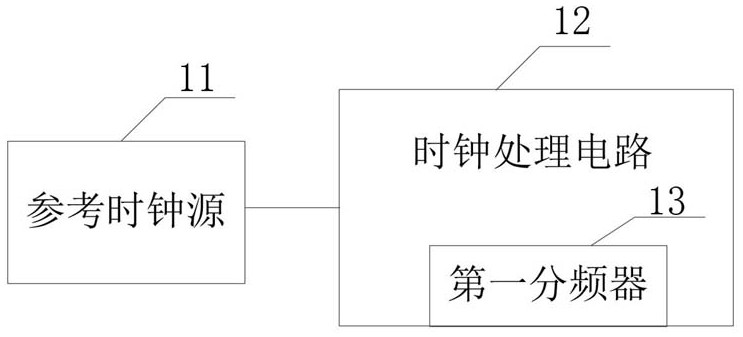

2、为解决上述技术问题,本发明提供了一种时钟发生器,包括:

3、参考时钟源,用于输出第一频率的参考时钟信号;

4、设置有第一分频器的时钟处理电路,与所述参考时钟源连接;

5、所述第一分频器用于根据用户发送的第一目标配置指令调整自身的分频系数;

6、所述时钟处理电路用于根据所述第一分频器的分频系数对所述第一频率的参考时钟信号进行频率调整,得到目标时钟信号。

7、在一种实施例中,所述时钟处理电路还包括:

8、锁相环电路,所述锁相环电路与所述参考时钟源连接,所述第一分频器与所述锁相环电路连接;

9、所述锁相环电路用于根据所述第一分频器的分频系数对所述第一频率的参考时钟信号进行频率调整,得到所述目标时钟信号。

10、在一种实施例中,所述锁相环电路具体用于根据所述第一分频器的分频系数对所述第一频率的参考时钟信号进行倍频,得到倍频后的第一时钟信号时;

11、所述时钟处理电路还包括:

12、分频电路,与所述锁相环电路连接;

13、所述分频电路用于对所述第一时钟信号进行预设倍数的分频,得到所述目标时钟信号。

14、在一种实施例中,所述时钟处理电路还包括参考分频器,所述参考分频器设有参考分频系数,所述锁相环电路包括相位比较器、环路滤波器和压控振荡器;

15、所述参考分频器的输入端与所述参考时钟源连接,所述相位比较器的输入端分别与所述参考分频器的输出端和所述第一分频器的输出端连接,所述相位比较器的输出端与所述环路滤波器的输入端连接,所述环路滤波器的输出端与所述压控振荡器的输入端连接,所述环路滤波器的输出端与所述第一分频器的输入端连接;

16、所述参考分频器根据所述参考分频系数对所述参考时钟信号进行分频,所述相位比较器根据所述参考分频器输出的时钟信号及所述第一分频器输出的时钟信号确定时钟误差并输入至所述压控振荡器,所述压控振荡器根据所述时钟误差调整所述压控振荡器的控制电压以调整所述压控振荡器输出的时钟信号的第一时钟信号的频率。

17、在一种实施例中,所述锁相环电路的个数为多个时,多个所述锁相环电路与多个所述第一分频器一一对应连接。

18、在一种实施例中,还包括:

19、第一配置寄存器,与所述第一分频器连接,用于存储与所述第一目标配置指令对应的第一目标分频系数;

20、所述第一分频器具体用于根据所述第一配置寄存器中的第一目标分频系数将自身的分频系数调整为所述第一目标分频系数。

21、在一种实施例中,所述分频电路包括:

22、整数分频器,与所述锁相环电路连接,用于对所述第一时钟信号进行预设整数倍的分频,得到所述目标时钟信号。

23、在一种实施例中,所述整数分频器的分频系数是根据用户发送的第二目标配置指令对应调整的。

24、在一种实施例中,所述分频电路还包括:

25、第二配置寄存器,与所述整数分频器连接,用于存储与所述第二目标配置指令对应的第二目标分频系数,所述第二目标分频系数为整数;

26、所述整数分频器具体用于根据所述第二配置寄存器中的第二目标分频系数将自身的分频系数调整为所述第二目标分频系数。

27、在一种实施例中,所述分频电路包括:

28、小数分频器,与所述锁相环电路连接,用于对所述第一时钟信号进行预设小数倍的分频,得到所述目标时钟信号。

29、在一种实施例中,所述小数分频器的分频系数是根据用户发送的第三目标配置指令对应调整的。

30、在一种实施例中,所述分频电路还包括:

31、第三配置寄存器,与所述小数分频器连接,用于存储与所述第三目标配置指令对应的第三目标分频系数,所述第三目标分频系数为小数;

32、所述小数分频器具体用于根据所述第三配置寄存器中的第三目标分频系数将自身的分频系数调整为所述第三目标分频系数。

33、在一种实施例中,所述时钟处理电路还包括:

34、第一多路复用器,与所述整数分频器和所述小数分频器连接,用于根据用户需求将所述整数分频器或所述小数分频器对应的通路导通,以输出所述整数分频器或所述小数分频器输出的目标时钟信号。

35、在一种实施例中,所述第一多路复用器具体用于根据用户输入的配置信息选择所述整数分频器或所述小数分频器对应的通路导通,若自身输出的时钟信号的频率为所述目标时钟信号对应的目标频率,则直接将自身输出的时钟信号作为所述目标时钟信号;若自身输出的时钟信号的频率达到频率阈值,则选择所述小数分频器对应的通路导通,以使所述小数分频器调整自身输出的时钟信号的频率至所述目标频率;

36、其中,所述用户输入的配置信息根据所述目标频率确定,所述频率阈值为所述目标频率的预设范围内的任意值。

37、在一种实施例中,所述时钟处理电路还包括输入端用于输入其他装置的时钟信号的相位调整锁相环电路,所述相位调整锁相环电路用于对所述其他装置的时钟信号的相位进行检测机调整,以输出与所述目标时钟信号同步的时钟信号。

38、在一种实施例中,还包括:

39、第二多路复用器,与所述整数分频器、所述小数分频器及所述相位调整锁相环电路连接,用于根据用户需求将所述整数分频器或所述小数分频器或所述相位调整锁相环电路对应的通路导通,以输出所述整数分频器或所述小数分频器或所述相位调整锁相环电路输出的时钟信号。

40、为解决上述技术问题,本发明还提供了一种时钟发生器的参数调整方法,应用于上述所述的时钟发生器,包括:

41、获取用户发送的第一目标配置指令;

42、对所述第一目标配置指令进行解析,得到第一目标分频系数;

43、将第一分频器的分频系数调整为所述第一目标分频系数,以使时钟处理电路基于所述第一目标分频系数对第一频率的参考时钟信号进行频率调整,得到目标时钟信号。

44、在一种实施例中,所述时钟发生器还包括与所述第一分频器连接的第一配置寄存器;对所述第一目标配置指令进行解析,得到第一目标分频系数之后,还包括:

45、将所述第一目标分频系数写入所述第一配置寄存器中;

46、将所述第一分频器的分频系数调整为所述第一目标分频系数,包括:

47、在接收到参数刷新指令时,将所述第一配置寄存器中存储的所述第一目标分频系数刷新至所述第一分频器中。

48、为解决上述技术问题,本发明还提供了一种时钟发生器的参数调整系统,应用于上述所述的时钟发生器,包括:

49、指令获取单元,用于获取用户发送的第一目标配置指令;

50、解析单元,用于对所述第一目标配置指令进行解析,得到第一目标分频系数;

51、参数调整单元,用于将第一分频器的分频系数调整为所述第一目标分频系数,以使时钟处理电路基于所述第一目标分频系数对第一频率的参考时钟信号进行频率调整,得到目标时钟信号。

52、为解决上述技术问题,本发明还提供了一种时钟发生器的参数调整装置,包括:

53、存储器,用于存储计算机程序;

54、处理器,用于在执行计算机程序时,实现上述所述的时钟发生器的参数调整方法的步骤。

55、为解决上述技术问题,本发明还提供了一种计算机可读存储介质,所述计算机可读存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现上述所述的时钟发生器的参数调整方法的步骤。

56、本发明提供了一种时钟发生器、参数调整方法、系统、装置及介质,涉及时钟领域,由于解决时钟发生器产生的时钟信号的频率不可调的问题。该方案中包括参考时钟源、设置有第一分频器的时钟处理电路,第一分频器用于根据用户发送的第一目标配置指令调整自身的分频系数;时钟处理电路用于根据第一分频器的分频系数对第一频率的参考时钟信号进行频率调整,得到目标时钟信号。可见,本发明的时钟发生器通过允许用户调节分频系数,并根据用户的需求进行频率调整,从而将其应用于cpu时,实现了对cpu时钟进行灵活调节以提升cpu的性能,可以满足服务器超频应用等用户定制化需求,以提升服务器产品在竞争中的优势。

- 还没有人留言评论。精彩留言会获得点赞!