一种基于神经网络自编码器的核脉冲信号处理架构及方法

本发明涉及核脉冲信号滤波,特别是涉及一种基于神经网络自编码器的核脉冲信号处理架构及方法。

背景技术:

1、在辐射探测中,噪声会影响阈值触发、脉冲信号形状甄别以及系统的能量分辨率。传统方法主要通过模拟或数字cr-rc(cr-rcm滤波器,cr-rcm filter)、梯形成型以及dplms最优滤波对系统噪声进行抑制,但这些方法不仅对噪声的抑制能力一般,并且会不同程度的使信号失真。为此有必要研制出一种在保留核脉冲信号波形细微特征、最小化信号失真度情况下,同时能对噪声进行最大程度的在线抑制的核脉冲信号滤波降噪方法。

技术实现思路

1、本发明的目的是提供一种基于神经网络自编码器的核脉冲信号处理架构及方法,能够提高核脉冲信号的滤波降噪效果,同时降低滤波降噪处理后核脉冲信号的失真度。

2、为实现上述目的,本发明提供了如下方案:

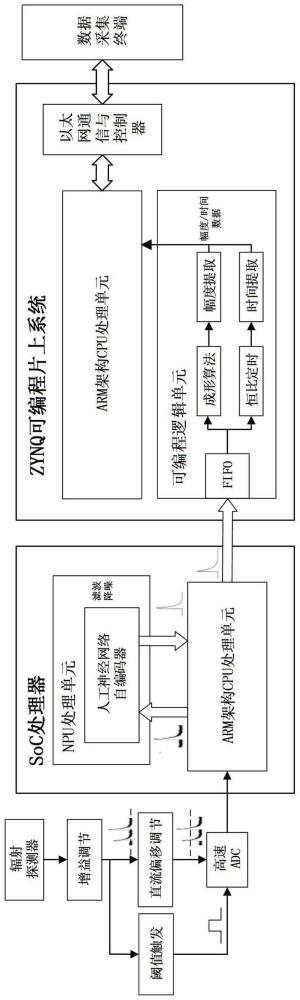

3、一种基于神经网络自编码器的核脉冲信号处理架构,包括:依次连接的核脉冲信号预处理模块、soc(systemonchip,芯片级系统)处理器和zynq可编程片上系统;

4、所述zynq(zynq-7000all programmable soc,全可编程片上系统)可编程片上系统与信号采集终端连接;

5、所述核脉冲信号预处理模块用于对原始信号依次进行滤波处理、放大处理和电压偏置处理,在放大处理后的原始信号中存在核脉冲信号时,对电压偏置处理后的原始信号进行模数转换处理,得到待降噪核脉冲数字信号;所述原始信号为随机叠加有核脉冲信号的基线信号;

6、所述soc处理器集成有训练后的神经网络自编码器模型;所述soc处理器用于将所述待降噪核脉冲数字信号加载到输入结构体变量中,将所述输入结构体变量输入到所述训练后的神经网络自编码器模型中得到滤波降噪处理后的核脉冲信号,将滤波降噪处理后的核脉冲信号缓存在输出结构体变量中,将输出结构体变量中滤波降噪处理后的核脉冲信号传输至所述zynq可编程片上系统;所述训练后的神经网络自编码器模型是利用含噪核脉冲数字信号和无噪核脉冲数字信号对神经网络自编码器模型进行自监督训练后得到的;

7、所述zynq可编程片上系统集成有多种数字化算法;所述zynq可编程片上系统用于利用多种所述数字化算法,提取滤波降噪处理后的核脉冲信号的参数信息,存储所述参数信息并将所述参数信息传输至所述信号采集终端。

8、可选的,所述数字化算法包括成形算法、幅度提取算法、恒比定时数字化算法和时间提取算法。

9、可选的,所述核脉冲信号预处理模块包括:增益调节电路、直流偏移调节电路、阈值触发电路和高速adc(模数转换器,analog-to-digital converter)电路;

10、所述增益调节电路分别与所述直流偏移调节电路和所述阈值触发电路连接;所述直流偏移调节电路和所述阈值触发电路均与所述高速adc电路连接;所述高速adc电路与所述soc处理器连接;

11、所述增益调节电路用于对原始信号依次进行滤波处理和放大处理,得到放大处理后的原始信号;

12、所述直流偏移调节电路用于对放大处理后的原始信号进行电压偏置处理,得到电压偏置处理后的原始信号;

13、所述阈值触发电路用于根据放大处理后的原始信号生成触发信号;所述阈值触发电路用于在放大处理后的原始信号的信号幅值达到幅值阈值时输出高电平为触发信号,在放大处理后的原始信号的信号幅值小于幅值阈值时输出低电平为触发信号;

14、所述高速adc电路用于在触发信号为高电平时,对电压偏置处理后的原始信号进行模数转换处理,得到待降噪核脉冲数字信号。

15、可选的,所述核脉冲信号预处理模块还包括:辐射探测器;

16、所述辐射探测器与所述增益调节电路连接;所述辐射探测器用于获取原始信号。

17、可选的,所述soc处理器包括:第一cpu(中央处理器,central processing unit)处理单元和npu(嵌入式神经网络处理器,neural-networkprocess units)处理单元;

18、所述第一cpu处理单元分别与所述核脉冲信号预处理模块、所述npu处理单元和所述zynq可编程片上系统连接;

19、所述第一cpu处理单元用于将所述待降噪核脉冲数字信号加载到输入结构体变量;

20、所述npu处理单元集成有训练后的神经网络自编码器模型;所述npu处理单元用于将所述输入结构体变量输入到所述训练后的神经网络自编码器模型中得到滤波降噪处理后的核脉冲信号,将滤波降噪处理后的核脉冲信号缓存在输出结构体变量中;

21、所述第一cpu处理单元还用于将输出结构体变量中滤波降噪处理后的核脉冲信号传输至所述zynq可编程片上系统。

22、可选的,所述zynq可编程片上系统包括:可编程逻辑单元和第二cpu处理单元;

23、所述可编程逻辑单元分别与所述soc处理器和所述第二cpu处理单元连接;所述第二cpu处理单元还与信号采集终端连接;

24、所述可编程逻辑单元集成有多种数字化算法;所述可编程逻辑单元用于利用多种所述数字化算法,提取滤波降噪处理后的核脉冲信号的参数信息;

25、所述第二cpu处理单元用于存储所述参数信息并将所述参数信息传输至所述信号采集终端。

26、可选的,所述神经网络自编码器模型为全连接神经网络或卷积神经网络。

27、一种基于神经网络自编码器的核脉冲信号处理方法,包括:

28、获取原始信号;所述原始信号为随机叠加有核脉冲信号的基线信号;

29、对原始信号依次进行滤波处理、放大处理和电压偏置处理;

30、在放大处理后的原始信号中存在核脉冲信号时,对电压偏置处理后的原始信号进行模数转换处理,得到待降噪核脉冲数字信号;

31、将所述待降噪核脉冲数字信号加载到输入结构体变量中;

32、将所述输入结构体变量输入到训练后的神经网络自编码器模型中,得到输出结构体变量;所述输出结构体变量包括滤波降噪处理后的核脉冲信号;所述训练后的神经网络自编码器模型是利用含噪核脉冲数字信号和无噪核脉冲数字信号对神经网络自编码器模型进行自监督训练后得到的;

33、利用多种数字化算法,提取滤波降噪处理后的核脉冲信号的参数信息;

34、存储并传输所述参数信息。

35、可选的,在所述获取原始信号之前,还包括:

36、构建神经网络自编码器模型;所述神经网络自编码器模型为全连接神经网络或卷积神经网络;

37、将含噪核脉冲数字信号输入到神经网络自编码器模型中,得到去噪核脉冲数字信号;

38、根据去噪核脉冲数字信号和无噪核脉冲数字信号确定损失函数值;

39、根据所述损失函数值,调整神经网络自编码器模型的参数并返回步骤“将含噪核脉冲数字信号输入到神经网络自编码器模型中,得到去噪核脉冲数字信号”直至连续预设次数次迭代的损失函数值均小于损失函数值阈值,得到训练后的神经网络自编码器模型。

40、可选的,所述神经网络自编码器模型包括依次连接的输入层、多编码层、多解码层和输出层;

41、所述多编码层包括依次连接的多个编码层;

42、所述多解码层包括依次连接的多个解码层;

43、所述编码层的数量等于所述解码层的数量。

44、根据本发明提供的具体实施例,本发明公开了以下技术效果:

45、本发明提供的一种基于神经网络自编码器的核脉冲信号处理架构及方法,通过在npu中部署神经网络自编码器,可以将中大规模的神经网络自编码器部署在嵌入式设备中,从而最大程度的发挥神经网络自编码器的滤波降噪能力,克服了传统基于fpga(field-programmable gatearray,现场可编程门阵列)的核脉冲信号处理器硬件架构对神经网络模型运算效率低、功耗高、受逻辑资源限制无法部署中大规模的神经网络自编码器限制噪声抑制能力的缺点;通过部署在npu中的神经网络自编码器对输入的核脉冲信号进行处理,在取得了相比于传统数字算法更优的噪声抑制效果情况下,同时保留了核脉冲信号的原始波形特征,克服了传统模拟方法或数字滤波算法对噪声抑制能力一般,且在滤波过程中造成核脉冲信号失真的缺点。

- 还没有人留言评论。精彩留言会获得点赞!