矩阵运算电路、处理器、集成电路系统、电子组件及设备的制作方法

本公开涉及集成电路,尤其涉及一种矩阵运算电路、处理器、集成电路系统、电子组件及电子设备。

背景技术:

1、矩阵乘和矩阵乘加运算在人工智能与高性能计算领域得到广泛应用。例如,卷积神经网络的卷积计算可转化为矩阵乘或矩阵乘加运算,又例如,transformer神经网络中也大量使用矩阵乘或矩阵乘加运算。

2、特别是在人工智能计算领域,矩阵具有一定的稀疏性,即矩阵的某些元素为0值。存储和计算这些0值数据是无效的,故在矩阵乘或矩阵乘加运算过程中,通过稀疏压缩可提升矩阵乘或矩阵乘加计算单元的利用率,从而提高计算速率并有效降低功耗。

3、目前,一种对有稀疏性的矩阵进行稀疏压缩的常用方式是采用软件方式对矩阵进行压缩后再进行计算,这种方式不适用于二维、三维高速乘加电路。另一种常用方式通过细粒度结构化稀疏将训练好的网络权重裁剪为稀疏度固定为50%的稀疏矩阵,但此方式需要提前对网络进行专门的训练处理,且对于原本稀疏度小于50%的矩阵,其加速效果并不理想。

技术实现思路

1、本公开的目的是提供一种电路结构简单的矩阵运算电路、处理器、集成电路系统、电子组件及电子设备,以支持在二维、三维硬件点乘(或乘加)运算的同时实现稀疏压缩。

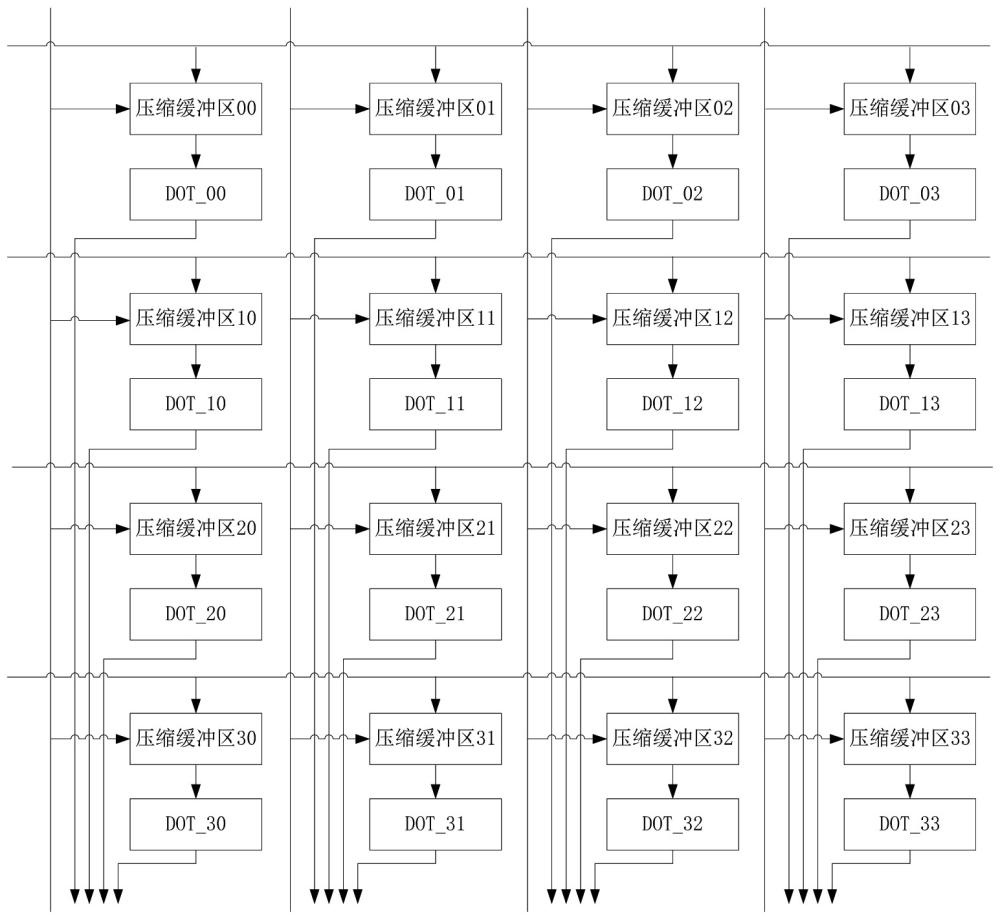

2、根据本公开的一个方面,提供一种矩阵运算电路,该矩阵运算电路包括m×n个运算单元和m×n个压缩缓存单元。第(i,j)个压缩缓存单元用于缓存a矩阵的第i行数据和b矩阵的第j列数据,丢弃0值数据对以实现对上述第i行数据和上述第j列数据的压缩,以k2个数据对/时钟周期的速度向第(i,j)个运算单元输出压缩后的第i行数据和第j列数据,其中,a矩阵为m×k1矩阵,b矩阵为k1×n矩阵,k2为运算单元一个时钟周期内可以处理的数据对数量。第(i,j)个运算单元用于通过至少一个时钟周期对上述压缩后的第i行数据和第j列数据执行点乘运算。

3、本公开实施例提供的矩阵运算电路支持矩阵的点乘运算,进一步的,本公开实施例提供的矩阵运算电路还可以支持矩阵的乘加运算。如果矩阵运算电路支持矩阵的乘加运算,那么,第(i,j)个压缩缓存单元还用于缓存c矩阵的元素数据cij,第(i,j)个运算单元还用于对点乘运算结果与元素数据cij执行加法运算。

4、本公开实施例中,无论支持点乘运算的矩阵运算电路,还是支持乘加运算的矩阵运算电路,可选的,一笔运算在第(i,j)个运算单元的运算结束,第(i,j)个运算单元和第(i,j)个压缩缓存单元的时钟关闭,直至下一笔运算开始。

5、第(i,j)个压缩缓存单元查找0值数据对的实现方式可以有多种。在上述矩阵运算电路的任一实施例基础上,一种可行的实现方式中,第(i,j)个压缩缓存单元根据第一位图查找0值数据对,其中,第一位图用于标记数据对的取值是否为0。另一种可行的实现方式中,第(i,j)个压缩缓存单元根据第二位图查找0值数据,0值数据对应的数据对为0值数据对,其中,第二位图用于标记a矩阵的第i行各个元素数据是否为0,或者,第二位图用于标记b矩阵的第j列各个元素数据是否为0。又一种可行的实现方式中,第(i,j)个压缩缓存单元直接识别缓存的a矩阵的第i行的各个元素数据是否存在0值,和/或缓存的b矩阵的第j列的各个元素数据是否存在0值,0值元素数据对应的数据对即为0值数据对。

6、如果运算单元一个时钟周期内可以处理的数据k2对数量小于k1,那么运算单元可能无法在一个时钟周期内完成a矩阵的第i行数据和b矩阵第j列数据的点乘运算。为应对这种情况,在上述矩阵运算电路的任一实施例基础上,第(i,j)个运算单元包括数据累加模块,用于累加上述压缩后的第i行数据和第j列数据的点乘运算在上述至少一个时钟周期的运算结果。

7、在上述矩阵运算电路的任一实施例基础上,矩阵运算电路可以包括m条行广播总线,第i条行广播总线与用于缓存上述第i行数据的n个压缩缓存单元通信,用于向n个压缩缓存单元广播上述第i行数据;矩阵运算电路还可以包括n条列广播总线,第j条列广播总线与用于缓存上述第j列数据的m个压缩缓存单元通信,用于向m个压缩缓存单元广播上述第j列数据。

8、在上述矩阵运算电路的任一实施例基础上,矩阵运算电路还可以包括输入缓存单元,用于缓存待进行矩阵运算的矩阵的数据。

9、在上述矩阵运算电路的任一实施例基础上,矩阵运算电路还可以包括译码单元,用于根据矩阵运算指示生成数据传输控制信息和运算控制信息,运算控制信息用于控制运算单元工作以完成矩阵运算指示。

10、在上述矩阵运算电路的任一实施例基础上,矩阵运算电路还可以包括矩阵取数与送数单元,用于根据数据传输控制信息,从输入缓存单元读取待进行矩阵运算的矩阵的数据送入压缩缓存单元。

11、根据本公开的另一方面,本公开提供一种矩阵运算电路,包括至少两个矩阵运算子电路,每个矩阵运算子电路包括m×n个运算单元和m×n个压缩缓存单元。其中,第n个矩阵运算子电路的第(i,j)个压缩缓存单元用于缓存an矩阵的第i行数据和bn矩阵的第j列数据,丢弃0值数据对以实现对上述第i行数据和上述第j列数据的压缩,以k2n个数据对/时钟周期的速度向第n个矩阵运算子电路的第(i,j)个运算单元输出压缩后的第i行数据和第j列数据,an矩阵为m×k1n矩阵,bn矩阵为k1n×n矩阵,k2n为第n个矩阵运算子电路的运算单元一个时钟周期内可以处理的数据对数量;第n个矩阵运算子电路的第(i,j)个运算单元用于通过至少一个时钟周期对上述压缩后的第i行数据和第j列数据执行点乘运算。上述至少两个矩阵运算子电路通过连接单元连接,以实现上述至少两个矩阵运算子电路的运算结果相加。

12、本公开实施例提供的矩阵运算电路支持矩阵的点乘运算,进一步的,本公开实施例提供的矩阵运算电路还可以支持矩阵的乘加运算。如果矩阵运算电路支持矩阵的乘加运算,那么,第n个矩阵运算子电路的第(i,j)个压缩缓存单元还用于缓存c矩阵的元素数据cij,第n个矩阵运算子电路的第(i,j)个运算单元还用于对点乘运算结果与元素数据cij执行加法运算。

13、本公开实施例中,无论支持点乘运算的矩阵运算电路,还是支持乘加运算的矩阵运算电路,可选的,一笔运算在第n个矩阵运算子电路的第(i,j)个运算单元的运算结束,第n个矩阵运算子电路的第(i,j)个运算单元和第n个矩阵运算子电路的第(i,j)个压缩缓存单元的时钟关闭,直至下一笔运算开始。

14、压缩缓存单元查找0值数据对的实现方式可以有多种。在上述第二方面的矩阵运算电路的任一实施例基础上,一种可行的实现方式中,第n个矩阵运算子电路的第(i,j)个压缩缓存单元根据第一位图查找0值数据对,其中,第一位图用于标记数据对的取值是否为0。另一种可行的实现方式中,第n个矩阵运算子电路的第(i,j)个压缩缓存单元根据第二位图查找0值数据,0值数据对应的数据对为0值数据对,其中,第二位图用于标记an矩阵的第i行各个元素数据是否为0,或者,第二位图用于标记bn矩阵的第j列各个元素数据是否为0。又一种可行的实现方式中,第n个矩阵运算子电路的第(i,j)个压缩缓存单元直接识别缓存的an矩阵的第i行的各个元素数据是否存在0值,和/或缓存的bn矩阵的第j列的各个元素数据是否存在0值,0值元素数据对应的数据对即为0值数据对。

15、如果第n个矩阵运算子电路的运算单元一个时钟周期内可以处理的数据k2对数量小于k1,那么第n个矩阵运算子电路的运算单元可能无法在一个时钟周期内完成an矩阵的第i行数据和bn矩阵第j列数据的点乘运算。为应对这种情况,在上述第二方面的矩阵运算电路的任一实施例基础上,第n个矩阵运算子电路的第(i,j)个运算单元包括数据累加模块,用于累加上述压缩后的第i行数据和第j列数据的点乘运算在上述至少一个时钟周期的运算结果。

16、在上述第二方面的矩阵运算电路的任一实施例基础上,一种可行的实现方式中,矩阵运算电路还可以包括m条行广播总线和/或n条列广播总线。第i条行广播总线与各个矩阵运算子电路的用于缓存an矩阵的第i行数据的压缩缓存单元通信,用于向该压缩缓存单元广播a矩阵的第i行数据,a矩阵的第i行数据包括各个an矩阵的第i行数据。第j条列广播总线与各个矩阵运算子电路的用于缓存bn矩阵的第j列数据的压缩缓存单元通信,用于向该压缩缓存单元广播b矩阵的第j列数据,b矩阵的第j列数据包括各个bn矩阵的第j列数据。另一种可行的实现方式中,每个矩阵运算子电路可以包括m条行广播总线和/或n条列广播总线。第i条行广播总线与用于缓存an矩阵的第i行数据的n个压缩缓存单元通信,用于向这n个压缩缓存单元广播该第i行数据。第j条列广播总线与用于缓存bn矩阵的第j列数据的m个压缩缓存单元通信,用于向这m个压缩缓存单元广播该第j列数据。

17、在上述第二方面的矩阵运算电路的任一实施例基础上,矩阵运算电路还可以包括以下至少一个单元:

18、输入缓存单元,用于缓存待进行矩阵运算的矩阵的数据;

19、译码单元,用于根据矩阵运算指示生成数据传输控制信息和运算控制信息,运算控制信息用于控制运算单元工作以完成矩阵运算指示;

20、矩阵取数与送数单元,用于根据数据传输控制信息,从输入缓存单元读取待进行矩阵运算的矩阵的数据送入压缩缓存单元。

21、根据本公开的另一方面,本公开提供一种处理器,该处理器包括上述任一实施例所述的矩阵运算电路。

22、根据本公开的另一方面,提供一种集成电路系统,包括上述任一实施例所述的矩阵运算电路。

23、根据本公开的另一方面,提供一种电子组件,包括上述实施例所述的处理器和/或上述实施例所述的集成电路系统。

24、根据本公开的另一方面,提供一种电子设备,包括上述任一实施例所述的电子组件。

- 还没有人留言评论。精彩留言会获得点赞!