一种存储器测试装置的制作方法

[0001]

本发明属于数字集成电路测试领域,具体涉及一种存储器测试装置。

背景技术:

[0002]

电路测试特别是数字电路测试,在电路包括电路板和系统的研制、生产和使用过程中都是一项十分重要的技术。存储器是数字电路的重要组成部分,存储器测试是测试技术中的一个重要领域。存储器测试的两个重要指标是对各类故障的检测能力故障覆盖率和完成检测所需要的时间。

[0003]

非易失性存储器具有掉电仍能保持信息的特点而成为存储器家族的热门领域。flash存储器作为非易失性存储器中发展最为迅速的一种,其密度和复杂程度日益提高,可能存在的缺陷类型越来越多,给soc芯片及其嵌入式存储器的测试带来了困难。为解决flash测试中的这些问题,人们提出了应用内建自测试或利用嵌入式软件等测试方法测试相关性能,都取得了比较好的效果,但这些方法大多单一,更不适用于批量的产品测试。

[0004]

目前军用存储器生产测试存在的缺点:

[0005]

1、单颗芯片测试时间随容量增大呈倍数上升,导致占用机台测试时间增大,使得测试成本越来越高。在需求量大的情况下,预筛选将成为节省成本的关键。

[0006]

2、目前市场上的编程器仅支持一次数据擦除、编程、校验等基本操作,不具有多功能、多数据、多模式、不同算法全覆盖的集成能力,也不具有详细的运行过程记录。因此普通编程器在生产测试过程中不仅效率低,而且故障覆盖率低。

[0007]

3、在需求量大的情况下,若采购多个编程器,其配套成本升高,不利于降低成本。

[0008]

4、在预筛选过程中,有时需要进行电压拉偏测试提高筛选效率和良率,而普通编程器不支持该操作,降低了筛选效率,增加了测试成本。

技术实现要素:

[0009]

有鉴于此,本发明的目的在于实现存储器测试的预筛选、多功能、多数据、多模式、不同算法全覆盖的集成能力的高效、低成本测试。

[0010]

为解决上述技术问题,本发明提供了一种存储器测试装置,该测试装置包括:储器集成测试平台mitp和pc机,所述储器集成测试平台mitp包括spartan6 fpga最小系统、电源配电网络pdn、串口电路、led电路和存储器测试接口电路,电源配电网络pdn、串口电路、led电路和存储器测试接口电路分别与spartan6 fpga最小系统双向通信;待测存储器芯片通过存储器测试接口与mitp进行连接,mitp与pc机通过串口电路实现串口通信;所述spartan6 fpga最小系统为除电源以外能维持fpga正常工作的最小基本单元,包括时钟电路、复位电路和配置电路,所述时钟电路为fpga提供必要的工作时钟源,复位电路为fpga提供稳定可靠地复位脉冲输出,采用max811芯片作为复位脉冲输出芯片;配置电路采用as配置模式,采用jtag边界扫描接口,用于debug调试与程序固化编程。

[0011]

所述pc机采用windows 7 sp1 64位操作系统;所述时钟电路包括50mhz和125mhz

两路时钟源,通过设计可选的参考时钟,减少硬件改动;所述配置电路采用hwd32p作为as配置芯片。

[0012]

所述测试装置还包括软件部分,所述软件包括pc机中运行的存储器监控软件和所述mitp中运行的存储器集成测试软件;所述存储器监控软件的通过第一串口通信模块、信息处理模块、ui交互模块、存储模块和显示模块实现;所述第一串口通信模块主要实现与mitp中运行的存储器集成测试软件的串口数据帧的收发,将接收的数据帧送入信息处理模块进行解析,将信息处理模块封装的数据帧发送至mitp;信息处理模块根据串口通信协议实现数据帧的解析与封装以及对控制信息的仲裁,ui交互模块主要实现人机交互功能,及时响应测试人员的控制需求,存储模块完成对必要信息的存储并生成日志文件供后续查阅,显示模块主要通过软件显示窗口对操作过程信息完成实时显示;所述存储器集成测试软件通过第二串口通信模块、时钟模块、复位模块、ram缓存模块、逻辑仲裁模块和测控模块实现;所述第二串口通信模块包括串口接收模块、串口发送模块、波特率发生模块、crc校验模块;所述第二串口通信模块主要实现数据帧的解析和封装,其中:串口接收模块用于数据帧的接收与解析,串口发送模块用于数据帧的封装与发送,串口接收模块和串口发送模块均通过波特率发生模块产生的波特率脉冲完成数据的接收与发送,在接收与发送过程中,各自采用crc校验模块对数据帧进行16位crc校验,在串口接收模块解析过程中,通过ram缓存模块将存储器监控软件下发的测试数据进行缓存;所述测控模块包括多个功能测试模块,每个功能测试模块包含一个fifo缓存模块;所述逻辑仲裁模块用于选择启动测控模块,以及数据包发送顺序的逻辑仲裁;所述复位模块采用全局异步复位;所述时钟模块、ram缓存模块、fifo缓存模块采用xilinx官方ip核进行设计。

[0013]

进一步的,所述信息处理模块对控制信息的仲裁具体为:当校验失败时,立即放弃当前数据包并中断操作,当校验通过时,将提取数据帧中的设备类型、错误码、运行状态码和有效返回地址,并根据错误码、运行状态码完成仲裁;通过显示模块输出显示当前运行状态,当测试结束时将运行过程信息存储至指定日志文件中;ui交互模块通过按钮控件实现对测试的有效启动与停止,所述控制按钮包括打开串口、关闭串口、开始测试、复位和退出按钮所述,打开串口、关闭串口按钮用于控制串口设备的开启与关闭,开始测试按钮用于开启后台服务线程并启动存储器功能测试,复位、退出按钮则分别用于对软件各模块的复位以及安全地退出程序操作。

[0014]

信息处理模块不仅用于串口数据帧的解析与封装,还用于对软件运行时的过程控制。

[0015]

进一步的,所述复位模块为消除异步复位引入的毛刺,采用异步复位同步释放的原则,将外部输入复位脉冲经过两个ff同步到内部逻辑当中;所述逻辑仲裁模块根据数据帧解析出的设备类型和操作码选择启动相应的测控模块,根据发送使能信号控制数据包的发送先后顺序。

[0016]

进一步的,该装置能够实现fpga配置存储器在常温环境下的全擦除及多种数据的全编程、校验、串并配置输出功能测试,具有jedec标准的nand flash在不同工作模式下的全编程、棋盘或march校验功能测试。

[0017]

进一步的,采用外部直流电压源实现对存储器电压拉偏测试并完成预筛选,可有效提高最终测试良率。

[0018]

有益效果:

[0019]

1.该装置可用于fpga配置存储器在常温环境下的全擦除及多种数据的全编程、校验、串并配置输出等功能测试,以及具有jedec标准的nand flash在不同工作模式下的全编程、棋盘或march校验等功能测试。能有效提高以上芯片的测试效率、降低测试成本。

[0020]

2.测控软件界面简洁且具有一键自动测试的功能,便于测试员进行筛选测试,降低失误率。

[0021]

3.测控软件具有日志保存功能,有利于工程师对其进行后期测试数据分析。

[0022]

4.测控软件在同一台电脑上可支持多个测试平台并行测试,提高了设备利用率。

[0023]

5.在基于该装置对1中fpga配置存储器进行线下测试过程中,利用外部直流电压源实现对其电压拉偏测试并完成预筛选,可有效提高最终测试良率。

附图说明

[0024]

图1是本发明测试装置的系统结构图

[0025]

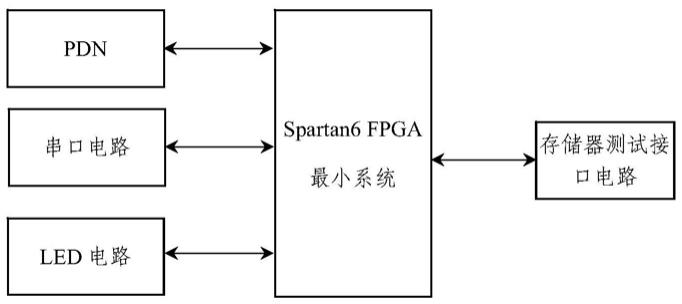

图2是mitp硬件结构框图;

[0026]

图3是本发明测试装置软件部分的功能结构框图;

[0027]

图4是存储器集成测试软件逻辑功能结构;

[0028]

图5是fpga逻辑顶层信号分布图;

[0029]

图6是存储器监控软件流程图;

[0030]

图7是采用本装置进行的hwd1603与hwd29f040测试流程;

[0031]

图8是采用本装置进行的hwd04s与hwd18v04测试流程。

具体实施方式

[0032]

下面结合附图对本发明的具体实施方式进行详细的说明。

[0033]

如图1所示,本发明提供了一种存储器测试装置,该测试装置包括:储器集成测试平台mitp和pc机。如图2所示,所述储器集成测试平台mitp包括spartan6 fpga最小系统、电源配电网络pdn、串口电路、led电路和存储器测试接口电路,电源配电网络pdn、串口电路、led电路和存储器测试接口电路分别与spartan6 fpga最小系统双向通信;待测存储器芯片通过存储器测试接口与mitp进行连接,mitp与pc机通过串口电路实现串口通信;所述spartan6 fpga最小系统为除电源以外能维持fpga正常工作的最小基本单元,包括时钟电路、复位电路和配置电路,所述时钟电路为fpga提供必要的工作时钟源,复位电路为fpga提供稳定可靠地复位脉冲输出,采用max811芯片作为复位脉冲输出芯片;配置电路采用as配置模式,采用jtag边界扫描接口,用于debug调试与程序固化编程。

[0034]

所述pc机采用windows 7 sp1 64位操作系统,基于该操作系统使用visual studio2015开发了一款基于mfc架构的存储器监控软件,该软件主要实现对整个存储器测试过程的监控与日志生成。所述时钟电路包括50mhz和125mhz两路时钟源,通过设计可选的参考时钟,减少硬件改动。所述配置电路采用hwd32p作为as配置芯片。

[0035]

在mitp系统中,供电需求见表1。鉴于mitp供电需求的多样性,主配电网络采用5v电源适配器供电,并通过ldo和集成电源芯片为系统供电。

[0036]

表1 mitp系统供电需求表

[0037]

电路模块电源需求spartan6最小系统0.75v、1.2v、1.5v、1.8v、3.3v串口电路3.3v、5v

[0038]

mitp与pc机通过串口电路采用rs232标准实现串口通信,串口电路主要由usb接口、usb转换芯片ch340e构成。

[0039]

led主要实现电路指示,并用于软件调试,它们均采用共电源连接方式以获得更高的驱动能力。

[0040]

如图3、4所示,所述测试装置还包括软件部分,所述软件包括pc机中运行的存储器监控软件和所述mitp中运行的存储器集成测试软件。所述存储器监控软件的通过第一串口通信模块、信息处理模块、ui交互模块、存储模块和显示模块实现。

[0041]

如图3、图6所示,所述第一串口通信模块主要实现与mitp中运行的存储器集成测试软件的串口数据帧的收发,将接收的数据帧送入信息处理模块进行解析,将信息处理模块封装的数据帧发送至mitp。为实现串口通信收发功能,设计了opencomm、closecomm、readcomm、writecomm四个主要方法,分别用于开启串口设备、关闭串口设备、读串口数据、写串口数据。在读串口数据过程中,设计了rthreadfunc后台线程用于循环监测读取数据流。

[0042]

信息处理模块根据串口通信协议实现数据帧的解析与封装以及对控制信息的仲裁。具体为:信息处理模块将接收的数据帧进行校验及解析,当校验失败时,立即放弃当前数据包并中断操作;当校验通过时,将提取数据帧中的设备类型、错误码、运行状态码和有效返回地址,并根据错误码、运行状态码完成仲裁。并通过显示模块输出显示当前运行状态,当测试结束时将运行过程信息存储至指定日志文件中。信息处理模块不仅用于串口数据帧的解析与封装,还用于对软件运行时的过程控制,从而设计了itpservice类用于维护后台正常运行,其中主要包括串口控制方法如开启opencomm、关闭closecomm,以及串口封装方法senddata等,后台服务控制方法如开启服务startservice、停止服务stopservice。为解析串口数据帧,设计了itpthreadfunc后台线程,用于校验数据帧和提取有效信息。并将提取的有效信息通过消息送入显示模块、存储模块进行显示、保存。

[0043]

ui交互模块主要实现人机交互功能,及时响应测试人员的控制需求,存储模块完成对必要信息的存储并生成日志文件供后续查阅,ui交互模块通过按钮控件实现对测试的有效启动与停止,所述控制按钮包括打开串口、关闭串口、开始测试、复位和退出按钮所述,打开串口、关闭串口按钮用于控制串口设备的开启与关闭,开始测试按钮用于开启后台服务线程并启动存储器功能测试,复位、退出按钮则分别用于对软件各模块的复位以及安全地退出程序操作。

[0044]

显示模块主要通过软件显示窗口对操作过程信息完成实时显示。显示模块运行在主线程中,主要用于对存储测试过程中产生的状态信息进行实时显示。通过消息接收函数onmsg(wparam wparam,lparam lparam)实时监听信息处理模块发出的消息帧,并将该消息解析后通过设计的showconsol方法输出至显示窗口,其中,wparam、lparam分别为信息处理模块传递的消息参数。

[0045]

当存储器测试成功或测试失败时,软件将通过stopservice方法结束后台服务,并通过设计的writetofile(msgconsol,_t(".\\datalog\\"),logname)函数,将消息窗口信

息msgconsol输出保存至以logname为名称的日志文件中,logname命名方式如下:

[0046]“fail/pass_芯片序号_年月日_时分.txt”。

[0047]

如图4所示,所述存储器集成测试软件通过第二串口通信模块、时钟模块、复位模块、ram缓存模块、逻辑仲裁模块和测控模块实现。所述第二串口通信模块包括串口接收模块、串口发送模块、波特率发生模块、crc校验模块。所述第二串口通信模块主要实现数据帧的解析和封装,其中:串口接收模块用于数据帧的接收与解析,串口发送模块用于数据帧的封装与发送,串口接收模块和串口发送模块均通过波特率发生模块产生的波特率脉冲完成数据的接收与发送。在接收与发送过程中,串口接收模块和串口发送模各自采用crc校验模块对数据帧进行16位crc校验,在串口接收模块解析过程中,通过ram缓存模块将存储器监控软件下发的测试数据进行缓存。所述测控模块包括包括多个功能测试模块,每个功能测试模块包含一个fifo缓存模块,用于存储器输入数据缓存处理;所述逻辑仲裁模块用于选择启动测控模块,以及数据包发送顺序的逻辑仲裁;所述复位模块采用全局异步复位;所述时钟模块、ram缓存模块、fifo缓存模块采用xilinx官方ip核进行设计。

[0048]

所述复位模块为消除异步复位引入的毛刺,采用异步复位同步释放的原则,将外部输入复位脉冲经过两个ff同步到内部逻辑当中;所述逻辑仲裁模块根据数据帧解析出的设备类型和操作码选择启动相应的测控模块,根据发送使能信号控制数据包的发送先后顺序。

[0049]

该装置能够实现存储器在常温环境下的全擦除及多种数据的全编程、校验、串并配置输出功能测试,具有jedec标准的nand flash在不同工作模式下的全编程、棋盘或march校验功能测试。

[0050]

采用外部直流电压源实现对存储器电压拉偏测试并完成预筛选,可有效提高最终测试良率。

[0051]

fpga逻辑顶层信号分布如图5所示,信号主要包括复位脉冲信号fpga_rst_n、外部时钟输入信号fpga_clk、存储器接口信号memory interfaces、串口接口信号uart interfaces等。

[0052]

采用本发明进行了fpga配置存储器,例如hwd04s与hwd18v04的测试、进行了nand flash,例如hwd29f040与hwd1603的测试,鉴于hwd04s与hwd18v04的指令集兼容性,hwd29f040与hwd1603指令集相互兼容,它们均各自采用同一个功能测试模块,测试流程如图7、图8所示。在自检测试或全片测试过程中,若测试不通过时,软件将自动结束测试过程并将错误消息进行上报。

[0053]

为兼容hwd1603与hwd29f040,在自检过程中,块擦除大小设定为16kbyte,采用word模式进行编程、校验。

[0054]

棋盘算法采用多组数据进行交替编程、校验。

[0055]

march算法采用w1->r1->(r1->wd->rd)->rall模型,该模型由控制指令帧进行选择。

[0056]

以上仅为发明的优选实施例而已,并不用以限制本发明,凡在本发明的思想原则内所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1