一种EEPROM存储器编程精度校正电路及方法与流程

一种eeprom存储器编程精度校正电路及方法

技术领域

[0001]

本发明涉及存储器精度校正技术领域,尤其涉及一种eeprom存储器编程精度校正电路及方法。

背景技术:

[0002]

电可擦除编程存储器(eeprom)是当今应用广泛的记忆元件之一。由于它既能像ram一样随时改写内容,又能像其它rom一样能长期地保存信息,因此在微机、微控制电路以及金卡(ic卡)工程中得到了广泛应用。在集成电路设计和制造中,由于设计工艺和封装等原因,实际制造同理论上有一定的差距.随着集成电路集成度的提高,集成电路高精度要求日趋明显,精度校正是实现高精度集成电路的必要手段。

[0003]

传统的eeprom精度校正方法有电阻薄膜的激光修调、熔丝烧断修调、二极管短路修调等技术。但是激光修调成本高工艺复杂;熔丝烧断修调误差大、成品率低;二极管修调技术占用芯片面积较大且是单向修调。因此,发明可靠性高及修正精度高的一种eeprom存储器编程精度校正电路成为该领域技术人员亟待解决的问题。

技术实现要素:

[0004]

本发明要解决的技术问题在于,针对现有技术的上述缺陷,提供一种eeprom存储器编程精度校正电路。

[0005]

第一方面,本发明公开了一种eeprom存储器编程精度校正电路,包括单多晶eeprom子电路、复位子电路、操作指令控制子电路、信号输入子电路及电荷泵;所述复位子电路分别与所述单多晶eeprom子电路、所述操作指令控制子电路、所述信号输入子电路及所述电荷泵电连接;所述单多晶eeprom子电路与所述信号输入子电路电连接,所述信号输入子电路与所述操作指令控制子电路电连接,所述操作指令控制子电路与所述电荷泵电连接,所述电荷泵与所述单多晶eeprom子电路电连接;所述操作指令控制子电路与所述单多晶eeprom子电路电连接;所述复位子电路用于检测eeprom存储器是否处于芯片测试模式下;在测试模式下时,所述复位子电路复位信号有效;所述复位子电路产生复位信号至所述单多晶eeprom子电路、所述操作指令控制子电路、所述信号输入子电路及所述电荷泵,所述单多晶eeprom子电路、所述操作指令控制子电路、所述信号输入子电路及所述电荷泵进入初始化状态;不作动作;若没有复位信号到来,则在测试使能信号为高电平时,通过给操作指令控制子电路的cs片选端输入不同的方波个数产生操作控制指令。

[0006]

优选地,所述操作指令控制子电路通过38译码电路产生不同的操作控制指令。

[0007]

优选地,所述信号输入子电路通过一根数据线的管脚复用进行数据传输及时钟控制。

[0008]

第二方面,本发明公开了一种一种eeprom存储器编程精度校正方法,所述方法包括:

[0009]

通过所述信号输入子电路判断电路是否处于测试模式;

[0010]

若处于测试模式,则所述复位子电路产生复位信号至所述单多晶eeprom子电路、所述操作指令控制子电路、所述信号输入子电路及所述电荷泵;

[0011]

依据所述复位信号控制所述单多晶eeprom子电路、所述操作指令控制子电路、所述信号输入子电路及所述电荷泵进入初始化状态;

[0012]

若没有复位信号到来,则在测试使能信号为高电平时,通过给信号输入子电路的cs片选端输入不同的方波个数产生操作控制指令。

[0013]

优选地,所述若没有复位信号到来,则在测试使能信号为高电平时,通过给信号输入子电路的cs片选端输入不同的方波个数产生操作控制指令包括:

[0014]

控制第一个方波产生读操作命令,将单多晶eeprom子电路中的数据读出;

[0015]

控制第二个方波产生擦操作命令,所述电荷泵产生电压以控制所述单多晶eeprom子电路擦除数据;

[0016]

控制第三个方波产生数据输入命令,通过所述信号输入子电路的管脚复用进行数据串行移位处理;

[0017]

控制第四个方波产生写操作命令,所述操作指令控制子电路产生写命令,并通过所述电荷泵产生电压输入到所述单多晶eeprom子电路,以实现对所述单多晶eeprom子电路中基准电压的调修。

[0018]

本发明的一种eeprom存储器编程精度校正电路及方法具有如下有益效果,本发明公开的一种eeprom存储器编程精度校正电路包括:单多晶eeprom子电路、复位子电路、操作指令控制子电路、信号输入子电路及电荷泵;复位子电路用于检测eeprom存储器是否处于芯片测试模式下;在测试模式下时,复位子电路复位信号有效;复位子电路产生复位信号至单多晶eeprom子电路、操作指令控制子电路、信号输入子电路及电荷泵,单多晶eeprom子电路、操作指令控制子电路、信号输入子电路及电荷泵进入初始化状态,不作动作;没有复位信号到来,则在测试使能信号为高电平时,通过给操作指令控制子电路的cs片选端输入不同的方波个数产生操作控制指令。因此,本发明通过管脚复用及单多晶eeprom结合,对eeprom存储器进行测试调修,成本低廉,功耗低,性价比高;同时能够灵活精确地调节基准源电压,有效提高了eeprom存储器的修调精度及校正精度。

附图说明

[0019]

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将结合附图及实施例对本发明作进一步说明,下面描述中的附图仅仅是本发明的部分实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他附图:

[0020]

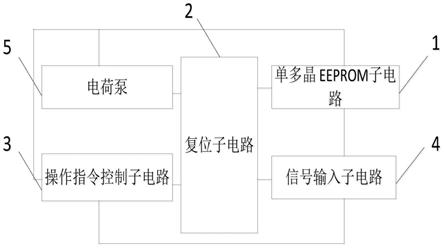

图1是本发明较佳实施例的一种eeprom存储器编程精度校正电路的电路原理框图;

[0021]

图2是本发明较佳实施例的一种eeprom存储器编程精度校正电路的单多晶eeprom子电路的电路图;

[0022]

图3是本发明较佳实施例的一种eeprom存储器编程精度校正方法的流程图;

[0023]

图4是本发明另一较佳实施例的一种eeprom存储器编程精度校正方法的流程图。

具体实施方式

[0024]

为了使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的技术方案进行清楚、完整的描述,显然,所描述的实施例是本发明的部分实施例,而不是全部实施例。基于本发明的实施例,本领域普通技术人员在没有付出创造性劳动的前提下所获得的所有其他实施例,都属于本发明的保护范围。

[0025]

本发明较佳实施例的如图1所示,本发明公开的一种eeprom存储器编程精度校正电路,包括单多晶eeprom子电路1、复位子电路2、操作指令控制子电路3、信号输入子电路4及电荷泵5;所述复位子电路2分别与所述单多晶eeprom子电路1、所述操作指令控制子电路3、所述信号输入子电路4及所述电荷泵5电连接;所述单多晶eeprom子电路1与所述信号输入子电路4电连接,所述信号输入子电路4与所述操作指令控制子电路3电连接,所述操作指令控制子电路3与所述电荷泵5电连接,所述电荷泵5与所述单多晶eeprom子电路1电连接;所述操作指令控制子电路3与所述单多晶eeprom子电路1电连接;所述复位子电路2用于检测eeprom存储器是否处于芯片测试模式下;在测试模式下时,所述复位子电路2复位信号有效;所述复位子电路2产生复位信号至所述单多晶eeprom子电路1、所述操作指令控制子电路3、所述信号输入子电路4及所述电荷泵5,所述单多晶eeprom子电路1、所述操作指令控制子电路3、所述信号输入子电路4及所述电荷泵5进入初始化状态;不作动作;若没有复位信号到来,则在测试使能信号为高电平时,通过给操作指令控制子电路3的cs片选端输入不同的方波个数产生操作控制指令。因此,本发明通过管脚复用及单多晶eeprom结合,对eeprom存储器进行测试调修,成本低廉,功耗低,性价比高;同时能够灵活精确地调节基准源电压,有效提高了eeprom存储器的修调精度及校正精度。

[0026]

优选地,所述操作指令控制子电路3通过38译码电路产生不同的操作控制指令。举例来说,当cs片选端到来第六个方波后,则产生擦操作指令。

[0027]

优选地,所述信号输入子电路4通过一根数据线的管脚复用进行数据传输及时钟控制。从而扩展了管脚功能,节约了成本,因此本发明性价比高。

[0028]

请参阅图3,本发明公开了一种eeprom存储器编程精度校正方法,所述方法包括:

[0029]

s1、通过所述信号输入子电路4判断电路是否处于测试模式;

[0030]

s2、若处于测试模式,则所述复位子电路2产生复位信号至所述单多晶eeprom子电路1、所述操作指令控制子电路3、所述信号输入子电路4及所述电荷泵5;

[0031]

s3、依据所述复位信号控制所述单多晶eeprom子电路1、所述操作指令控制子电路3、所述信号输入子电路4及所述电荷泵5进入初始化状态;

[0032]

s4、若没有复位信号到来,则在测试使能信号为高电平时,通过给信号输入子电路4的cs片选端输入不同的方波个数产生操作控制指令。

[0033]

优选地,请参阅图4,所述若没有复位信号到来,则在测试使能信号为高电平时,通过给信号输入子电路4的cs片选端输入不同的方波个数产生操作控制指令包括:

[0034]

s41、控制第一个方波产生读操作命令,将单多晶eeprom子电路1中的数据读出;

[0035]

s42、控制第二个方波产生擦操作命令,所述电荷泵5产生电压以控制所述单多晶eeprom子电路1擦除数据;

[0036]

s43、控制第三个方波产生数据输入命令,通过所述信号输入子电路4的管脚复用进行数据串行移位处理;

[0037]

s44、控制第四个方波产生写操作命令,所述操作指令控制子电路3产生写命令,并通过所述电荷泵5产生电压输入到所述单多晶eeprom子电路1,以实现对所述单多晶eeprom子电路1中基准电压的调修。

[0038]

具体地,在本实施例中,通过所述信号输入子电路4的管脚复用进行数据串行移位处理,以实现数据写入操作指令。具体的数据输入过程如下:主机要生成一个写时间隙,必须把数据线拉到低电平然后释放,开始输入数据。数据输入周期最少为60μs,最长不超过120μs。数据输入周期一开始,主机先把总线拉低1μs以表示数据输入周期开始。随后若主机想输入0,则继续拉低电平最少60μs直至数据输入周期结束,然后释放总线为高电平;若主机想输入1,在一开始拉低总线电平1μs后就释放总线为高电平,一直到数据输入周期结束。而作为从机的信号输入子电路则在检测到总线被拉低后等待15μs,然后从15μs到45μs开始对总线采样,若在采样期内总线为高电平则为1,若在采样期内总线为低电平则为0。在采样之后需要将采样的数据写入到所述单多晶eeprom子电路中。

[0039]

请参阅图2,当所述操作指令控制子电路3产生写操作命令后,此时图2中vd=16v,vcg=0;i1接高压11.4v,n型igfet n1和n型igfet n2开启;i3接高压约15v,p型igfet p1导通;i2接高电平,约6.2v,n型igfet n3导通;而n型igfet n4的导通与否,取决于数据端d。若所述信号输入子电路4采样期内总线为高电平则为1,即当d=1时,n型igfet n4关断,相当于n型igfet n3的s端悬空,p型igfetp2的d、s、b几乎都是16v,此时n型igfet n6承受高压,造成隧穿,从vcg吸取电子到浮栅上,存储电荷,逻辑“1”;若所述信号输入子电路4采样期内总线为低电平则为0,即当d=0时,n型igfet n4开启,所述单多晶eeprom子电路从vd到gnd就有了电流通路,使得p型igfet p2的d、s两端的电压被拉低,n型igfet n6管上的电压较低,不会隧穿,不能汲取电子到浮栅,逻辑“0”。因此本发明灵活精确完成了对eeprom中基准参数的修调,从而提升了eeprom存储器中晶振输出频率的稳定性和工作温度范围,提高eeprom存储器的编程精度。

[0040]

综上所述,本发明公开了一种eeprom存储器编程精度校正电路及方法,所述一种eeprom存储器编程精度校正电路包括单多晶eeprom子电路1、复位子电路2、操作指令控制子电路3、信号输入子电路4及电荷泵5;复位子电路2用于检测eeprom存储器是否处于芯片测试模式下;在测试模式下时,复位子电路2复位信号有效;复位子电路2产生复位信号至单多晶eeprom子电路1、操作指令控制子电路3、信号输入子电路4及电荷泵5,单多晶eeprom子电路1、操作指令控制子电路3、信号输入子电路4及电荷泵5进入初始化状态,不作动作;没有复位信号到来,则在测试使能信号为高电平时,通过给信号输入子电路4的cs片选端输入不同的方波个数产生操作控制指令。因此,本发明通过管脚复用及单多晶eeprom结合,对eeprom存储器进行测试调修,成本低廉,功耗低,性价比高;同时能够灵活精确地调节基准源电压,有效提高了eeprom存储器的修调精度及校正精度。

[0041]

以上对本发明所提供的一种eeprom存储器编程精度校正电路及方法进行了详细介绍,本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容仅为本发明的实施方式,并非因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括

在本发明的专利保护范围内。不应理解为对本发明的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1