包含半导体元件的存储器装置的制作方法

本发明关于包含半导体元件的存储器装置。

背景技术:

1、近年来,在大型集成电路(lsi)技术开发上,一直在追求存储器装置的高度积体化及高性能化。

2、通常的平面型金属氧化物半导体(mos)晶体管,具有在沿着半导体基板的上表面的水平方向延伸的通道(channel)。相对于此,环绕式栅极晶体管(sgt)具有在与半导体基板的上表面垂直的方向延伸的通道(参照例如专利文献1及非专利文献1)。因此,与平面型mos晶体管相比,sgt可达成更高密度化的半导体装置。将该sgt用作为选择晶体管,可实现例如连接有电容的动态随机存取存储器(dram)(参照例如非专利文献2)、连接有电阻值变化元件的相变化存储器(pcm,phase change memory)(参照例如非专利文献3)、电阻式随机存取存储器(rram,resistive random access memory)(参照例如非专利文献4)、利用电流使磁化方向变化而使电阻值变化的磁阻式随机存取存储器(mram,magneto-resistiverandom access memory)(参照例如非专利文献5)等的高度积体化。另外,还有例如不包含电容,只用一个mos晶体管构成的dram存储器单元(参照例如非专利文献7)。本技术为关于不包含电阻值变化元件或电容的可只用mos晶体管构成的动态快闪存储器(dynamic flashmemory)。

3、图15a至15d显示前述的不包含电容,只用一个mos晶体管构成的dram存储器单元的写入动作,图16a及16b显示动作上的问题点,图17a至17c显示读出动作(参照非专利文献7至10)。图15a显示写入“1”之际的状态。此处,存储器单元(memory cell)形成于soi(绝缘层上覆硅)基板1101,该存储器单元由与源极线sl连接的源极n+层1103、与位元线bl连接的汲极n+层1104、与字符线wl连接的栅极导电层1105及mos晶体管1110a的浮体(floatingbody)1102所构成,并不包含有电容,该单一个mos晶体管1110a构成dram存储器单元。在浮体1102正下方,soi基板1100的sio2层1101与浮体1102相接触。要将“1”写入此只由单一个mos晶体管1110a构成的存储器单元时,使mos晶体管1110a在线性区域动作。也就是,从源极n+层1103开始延伸的电子的通道1107会有夹止点1108,并不会到达与位元线连接的汲极n+层1104。当在与汲极n+层连接的位元线bl及与栅极导电层1105连接的字符线wl都施加高电压,且使栅极电压为汲极电压的约1/2程度而使mos晶体管1110a动作时,在汲极n+层1104附近的夹止点1108,电场强度会最大。因而,从源极n+层1103朝向汲极n+层1104流动的受到加速的电子会撞击si的晶格,撞击时丧失的运动能量会使得电子-空穴对产生(撞击游离(impact ionization)现象)。产生的大部分的电子(未图示)会到达汲极n+层1104。小部分的极热的电子会越过栅极氧化膜1109而到达栅极导电层1105。同时,产生的空穴1106会使得浮体1102充电。在此情况,因为浮体1102为p型si,所以产生的空穴使得多数载子更增多。当浮体1102中充满了产生的空穴1106使得浮体1102的电压变高到比源极n+层1103高出vb以上,再产生出的空穴就会放电到源极n+层1103。此处,vb为源极n+层1103与p层的浮体1102之间的pn接面的内建电压(built-in voltage),约为0.7v。图15b显示产生的空穴1106将浮体1102充电到饱和的情形。

4、接着,参照图15c来说明存储器单元1110b的写入“0”的动作。就共通的选择字符线wl而言,随机存在有写入“1”的存储器单元1110a及写入“0”的存储器单元1110b。图15c显示的是从“1”的状态改写为“0”的状态的情形。要写入“0”时,使位元线bl的电压为负偏压,使汲极n+层1104与p层的浮体1102之间的pn接面为顺偏压。如此一来,在前一个周期预先于浮体1102产生的空穴1106会流入与位元线bl连接的汲极n+层1104。写入动作结束,就得到充满了产生的空穴1106的存储器单元1110a(图15b)、及产生的空穴都流掉了的存储器单元1110b(图15c)这两种存储器单元的状态。充满了空穴1106的存储器单元1110a的浮体1102的电位比产生的空穴都流掉了的浮体1102高。因此,存储器单元1110a的阈值电压会比存储器单元1110b的阈值电压低。图15d显示该状况。

5、接着,参照图16a及图16b来说明由单一个mos晶体管构成的存储器单元的动作上的问题点。如图16a所示,浮体的电容量cfb为与字符线连接的栅极与浮体之间的电容量cwl、与源极线连接的源极n+层1103与浮体1102之间的pn接面的接面电容量csl、与位元线连接的汲极n+层1104与浮体1102之间的pn接面的接面电容量cbl的总和,如以下的式(1)所示。

6、cfb = cwl + cbl + csl (1)

7、因此,写入时当字符线电压vwl变动,作为存储器单元的记忆节点(storage node)的浮体1102的电压也会受其影响。图16b显示该状况。写入时当字符线电压vwl从0v升高到vprogwl,浮体1102的电压vfb会因为与字符线的电容耦合而从字符线电压变化之前的初始状态的电压vfb1升高到vfb2。其电压变化量δvfb如以下的式(2)所示。

8、δvfb=vfb2-vfb1

9、= cwl / (cwl + cbl + csl) × vprogwl (2)

10、此处,如以下的式(3)表示β。

11、β= cwl / (cwl + cbl + csl) (3)

12、β称为耦合率。在如此的存储器单元中,cwl的贡献率很大,例如cwl:cbl:csl=8:1:1。在此情况,β=0.8。当字符线从例如写入时的5v,在写入结束后降到0v时,由于字符线与浮体1102的电容耦合,浮体1102会受到5v×β=4v的振幅杂讯。因此,很难取得够大的足以区分写入时的浮体1102的“1”电位与“0”电位的电位差裕度(margin)。

13、图17a及图17b显示读出动作,图17a显示“1”写入的状态,图17b显示“0”写入的状态。实际上,即便在写入“1”时于浮体1102写入vb,当字符线的电压在写入结束回到0v,浮体1102也会降到负偏压。在写入“0”之际,浮体1102的电位会变为负更多的负偏压,而难以在写入之际有够大的“1”与“0”的电位差裕度。因此,难以将实际上不包含电容的dram存储器单元予以制品化。

14、[现有技术文献]

15、[专利文献]

16、[专利文献1]特开平2-188966号公报

17、[专利文献2]特开平3-171768号公报

18、[专利文献3]特许第3957774号公报。

19、[非专利文献]

20、[非专利文献1]hiroshi takato,kazumasa sunouchi,naoko okabe,akihironitayama,katsuhiko hieda,fumio horiguchi,and fujio masuoka:ieee transactionon electron devices,vol.38,no.3,pp.573-578(1991)

21、[非专利文献2]h.chung,h.kim,h.kim,k.kim,s.kim,k.dong,j.kim,y.c.oh,y.hwang,h.hong,g.jin,and c.chung:“4f2 dram cell with vertical pillartransistor(vpt),”2011proceeding of the european solid-state device researchconference,(2011)

22、[非专利文献3]h.s.philip wong,s.raoux,s.kim,jiale liang,j.r.reifenberg,b.rajendran,m.asheghi and k.e.goodson:“phase change memory,”proceeding of ieee,vol.98,no 12,december,pp.2201-2227(2010)

23、[非专利文献4]t.tsunoda,k.kinoshita,h.noshiro,y.yamazaki,t.iizuka,y.ito,a.takahashi,a.okano,y.sato,t.fukano,m.aoki,and y.sugiyama:“low powerand high speed switching of ti-doped nio reram under the unipolar voltagesource of less than 3v,”iedm(2007)

24、[非专利文献5]w.kang,l.zhang,j.klein,y.zhang,d.ravelosona,and w.zhao:“reconfigurable codesign of stt-mram under process variations in deeplyscaled technology,”ieee transaction on electron devices,pp.1-9(2015)

25、[非专利文献6]m.g.ertosum,k.lim,c.park,j.oh,p.kirsch,and k.c.saraswat:“novel capacitorless single-transistor charge-trap dram(1t ct dram)utilizingelectron,”ieee electron device letter,vol.31,no.5,pp.405-407(2010)

26、[非专利文献7]j.wan,l.rojer,a.zaslavsky,and s.critoloveanu:“a compactcapacitor-less high-speed dram using field effect-controlled chargeregeneration,”electron device letters,vol.35,no.2,pp.179-181(2012)

27、[非专利文献8]t.ohsawa,k.fujita,t.higashi,y.iwata,t.kajiyama,y.asao,and k.sunouchi:“memory design using aone-transistor gain cell on soi,”ieeejssc,vol.37,no.11,pp1510-1522(2002).

28、[非专利文献9]t.shino,n.kusunoki,t.higashi,t.ohsawa,k.fujita,k.hatsuda,n.ikumi,f.matsuoka,y.kajitani,r.fukuda,y.watanabe,y.minami,a.sakamoto,j.nishimura,h.nakaj ima,m.morikado,k.inoh,t.hamamoto,a.nitayama:“floating body ram technology and its scalability to 32nm node and beyond,”ieee iedm(2006).

29、[非专利文献10]e.yoshida:“a capacitorless 1t-dram technology usinggate-induced drain-leakage(gidl)current for low-power and high-speed embeddedmemory,”ieee iedm(2006).

30、[非专利文献11]j.y.song,w.y.choi,j.h.park,j.d.lee,and b-g.park:“designoptimization of gate-all-around(gaa)mosfets,”ieee trans.electron devices,vol.5,no.3,pp.186-191,may 2006.

31、[非专利文献12]n.loubet,et al.:“stacked nanosheet gate-all-aroundtransistor to enable scaling beyond finfet,”2017ieee symposium on vlsitechnology digest of technical papers,t17-5,t230-t231,june 2017.

32、[非专利文献13]h.jiang,n.xu,b.chen,l.zeng1,y.he,g.du,x.liu andx.zhang:“experimental investigation of self heating effect(she)in multiple-fin soi finfets,”semicond.sci.technol.29(2014)115021(7pp).

33、[非专利文献14]e.yoshida,and t.tanaka:“a capacitorless1t-dramtechnology using gate-induced drain-leakage(gidl)current for low-power andhigh-speed embedded memory,”ieee transactions on electron devices,vol.53,no.4,pp.692-697,apr.2006.。

技术实现思路

1、[发明所欲解决的课题]

2、在没有电容的一个晶体管型的dram(增益单元(gain cell))的存储器装置中,字符线与浮动的sgt基体(sgt body)的电容耦合很强。在数据读出时及写入时使字符线的电位变化,该变化就会直接成为杂讯而传到sgt基体。此会引起记忆数据的误读出或误写入的问题,使得没有电容的一个晶体管型的dram(增益单元)的实用化变困难。

3、[解決课题的手段]

4、为了解决上述的课题,根据本发明的一个态样的半导体存储器装置包含:

5、半导体基材,在基板上直立于垂直方向、或沿着该基板在水平方向延伸;

6、第一杂质层及第二杂质层,配置于该半导体基材的两端;

7、第一栅极绝缘层,围绕该第一杂质层与该第二杂质层之间的该半导体基材的侧面的一部分或全部,且与该第一杂质层接触或接近;

8、第二栅极绝缘层,围绕该半导体基材的侧面的一部分或全部,且与该第一栅极绝缘层连接,与该第二杂质层接触或接近;

9、第一栅极导体层,覆盖该第一栅极绝缘层;第二栅极导体层,覆盖该第二栅极绝缘层;

10、第一绝缘层,配置于该第一栅极导体层与该第二栅极导体层之间;

11、第一配线导体层,连接到该第一杂质层;

12、第二配线导体层,连接到该第二杂质层;

13、第三配线导体层,连接到该第一栅极导体层;以及

14、第四配线导体层,连接到该第二栅极导体层,

15、其中,该半导体基材包含一通道半导体层,该通道半导体层由被该第一栅极绝缘层所覆盖的第一通道半导体层及被该第二栅极绝缘层所覆盖的第二通道半导体层所构成,该通道半导体层侧面全部由该第一栅极绝缘层及该第二栅极绝缘层或由包含该第一栅极绝缘层及该第二栅极绝缘层的绝缘材料层加以围绕,控制施加于该第一配线导体层、该第二配线导体层、该第三配线导体层及该第四配线导体层的电压,以通过进行以下动作而进行存储器写入动作:利用在该第一杂质层与该第二杂质层之间流通的电流使撞击游离化现象在该第一通道半导体层与该第二通道半导体层间的第一交界区域、或第一杂质层与第一通道半导体层间的第二交界区域、或第二杂质层与第二通道半导体层间的第三交界区域发生的动作、或产生栅极诱导汲极漏电流的动作;进行使产生的电子群及产生的空穴群之中的属于该通道半导体层中的少数载子的该电子群或该空穴群从该第一杂质层或该第二杂质层排除掉的动作;以及进行使属于该通道半导体层中的多数载子的该电子群或该空穴群的一部分或全部残留在该第一通道半导体层及该第二通道半导体层的任一方或两方的动作;以及

16、控制施加于该第一配线导体层、该第二配线导体层、该第三配线导体层及该第四配线导体层的电压,将属于该通道半导体层中的多数载子的该电子群或该空穴群的中的残留的电子群或残留的空穴群从该第一杂质层及该第二杂质层的一方或两方去除掉,而进行存储器清除动作。

17、该半导体存储器装置通过进行该存储器清除动作,而将该第一杂质层与该第一通道半导体层之间的第一pn接面、及该第二杂质层与该第二通道半导体层之间的第二pn接面保持在逆偏压状态。

18、该半导体存储器装置中该第一配线导体层为源极线,该第二配线导体层为位元线,该第三配线导体层及该第四配线导体层之中的一者为字符线,另一者为第一驱动控制线,且施加电压于该源极线、该位元线、该第一驱动控制线及该字符线来选择性地进行该存储器清除动作及该存储器写入动作。

19、该半导体存储器装置在俯视时,该第二配线导体层与该第三配线导体层及该第四配线导体层正交。

20、该半导体存储器装置中该第一栅极导体层与该第一通道半导体层之间的第一栅极电容比该第二栅极导体层与该第二通道半导体层之间的第二栅极电容大。

21、该半导体存储器装置通过使该第一栅极导体层的第一通道长度比该第二栅极导体层的第二通道长度长、使该第一栅极绝缘层比该第二栅极绝缘层薄、使该第一栅极绝缘层的相对介电常数比该第二栅极绝缘层的相对介电常数大之中的任一方式、或这些方式的任意组合,而使该第一栅极电容比该第二栅极电容大。

22、该半导体存储器装置中该第一杂质层及该第二杂质层为n型半导体层,该第一通道半导体层及该第二通道半导体层为p型半导体层或中性半导体层,在该存储器清除动作开始时,通过空穴群排除动作及接续的已排除空穴群排除停止动作而进行该存储器清除动作,该空穴群排除动作使该第二杂质层的电压变为低于该第二通道半导体层的电压,使该第二杂质层与该第二通道半导体层之间的由该第二杂质层与该第二通道半导体层所形成的pn接面变为顺偏压,且将该空穴群从该第二通道半导体层去除至该第二杂质层;该已排除空穴群排除停止动作使该第二杂质层的电压变为高于该第二通道半导体层的电压,使该第二pn接面变为逆偏压,且使该空穴群的去除停止。

23、该半导体存储器装置在该存储器写入动作开始时,使因撞击游离化现象而产生的该空穴群储存于该第一通道半导体层及该第二通道半导体层,储存的该空穴群使得该第一栅极导体层的第一mos晶体管的第一阈值电压及该第二栅极导体层的第二mos晶体管的第二阈值电压降低,且使该第一栅极导体层及该第二栅极导体层的任一者的电压随着该降低而降低。

24、该半导体存储器装置在该存储器写入动作开始时,使因撞击游离化现象而产生的该空穴群储存于该第一通道半导体层及该第二通道半导体层,储存的该空穴群使得该第一栅极导体层的第一mos晶体管的第一阈值电压及该第二栅极导体层的第二mos晶体管的第二阈值电压降低,该降低产生使从汲极电极层流到源极电极层的电流增大的效果,该效果在该存储器写入动作中使正回授发生而进行写入。

25、该半导体存储器装置在该存储器写入动作中及存储器读出动作中,在与驱动控制线连接的该第一栅极导体层或第二栅极导体层所围绕的该第一通道半导体层或该第二通道半导体层的外周部形成反转层。

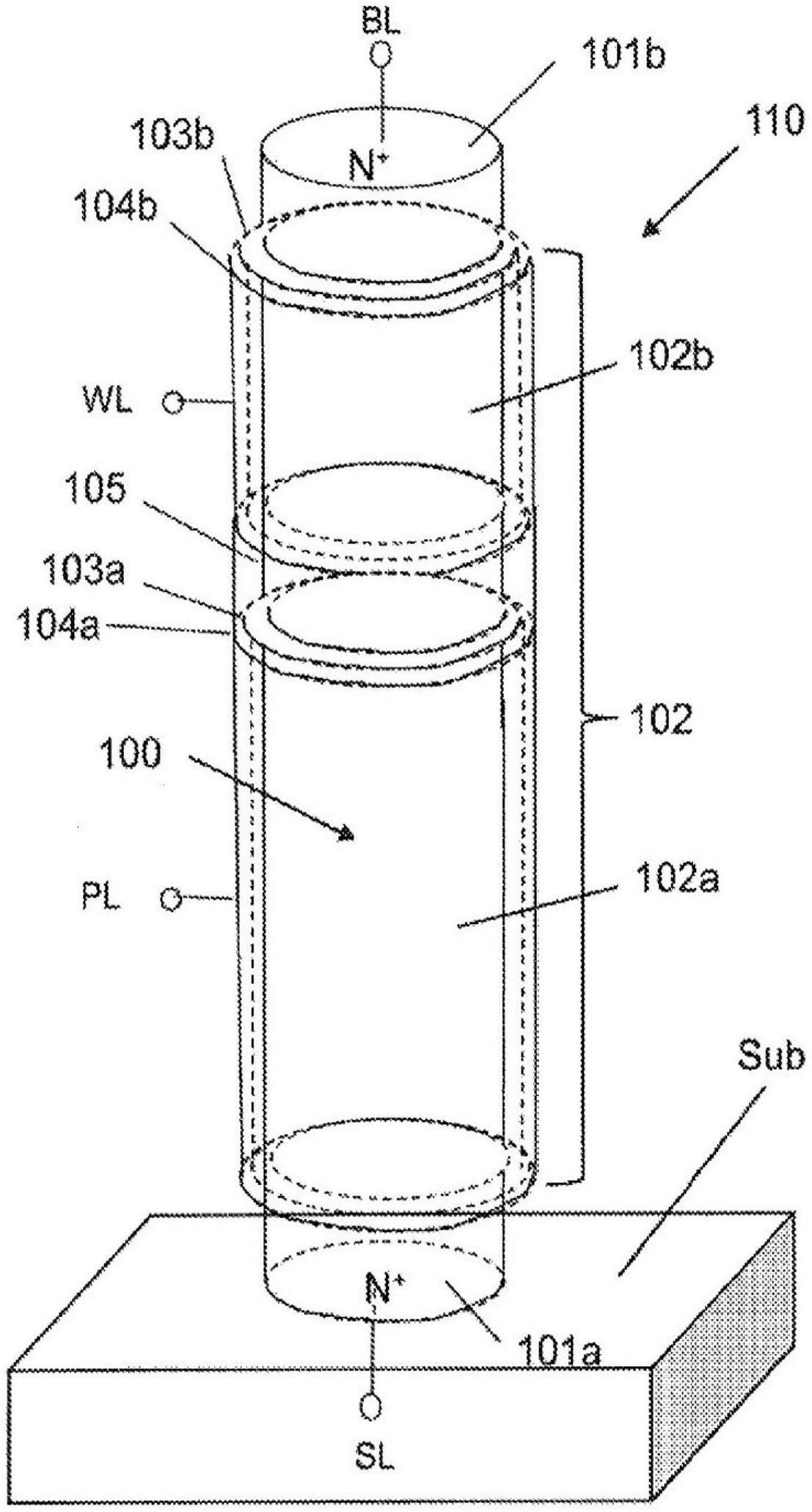

26、该半导体存储器装置中该半导体基材垂直于该基板而形成,且在垂直方向,该半导体存储器装置包含:在该基板上的该第一杂质层、在该第一杂质层上的该第一通道半导体层、在该第一通道半导体层上的该第二通道半导体层、在该第二通道半导体层上的该第二杂质层、围绕该第一通道半导体层的该第一栅极绝缘层、围绕该第二通道半导体层的该第二栅极绝缘层、围绕该第一栅极绝缘层的该第一栅极导体层、围绕该第二栅极绝缘层的该第二栅极导体层、以及在该第一栅极导体层与该第二栅极导体层之间的该第一绝缘层。

27、该半导体存储器装置中该第一栅极绝缘层与该第二栅极绝缘层由相同材料所形成。

28、该半导体存储器装置中该第一栅极绝缘层与该第二栅极绝缘层由不同的材料层所形成,该第一绝缘层与该第二栅极绝缘层由相同的材料层所形成。

29、该半导体存储器装置更包含:第一绝缘材料层,具有第一空孔或不具有该第一空孔,而且与该第一栅极导体层及该第二栅极导体层邻接配置,并相对于该基板在垂直方向延伸。

30、该半导体存储器装置中该第一绝缘材料层由低介电常数材料所形成。

31、该半导体存储器装置更包含:第二绝缘材料层,具有第二空孔或不具有该第二空孔,且与该第一配线导体层及该第二配线导体层的一方或两方邻接配置。

32、该半导体存储器装置中该第一绝缘材料层由低介电常数材料所形成。

33、该半导体存储器装置更包含:第一导体层,配置于该第一绝缘材料层的底部,而且与该第一栅极导体层连接并在水平方向延伸。

34、该半导体存储器装置更包含:形成于该基板的第一杂质井层、及形成于该第一杂质井层内的第二杂质井层,该半导体基材在该第二杂质井层的上垂直于该基板而直立或在水平方向延伸。

35、该半导体存储器装置中该基板为p型半导体,该第一杂质井层为n型半导体,该第二杂质井层为p型半导体,且在进行该存储器抹除动作时对属于p型半导体的该第二杂质井层施加负偏压。

- 还没有人留言评论。精彩留言会获得点赞!