自适应错误校正以提高系统存储器可靠性、可用性和可服务性(RAS)的制作方法

描述一般与存储器系统相关,并且更具体地,描述与系统存储器错误管理相关。

背景技术:

1、随着存储器设备的制造工艺不断微缩,存储器设备密度和操作速度不断增加,所有这些都倾向于导致存储器设备的运行时间错误的增加。即使有错误校验和校正(ecc),错误的频率也可能超过校正错误的措施。

2、解决存储器设备中的故障的一种技术是备用,其涉及在设备中包括仅在检测到故障的情况下使用的存储器资源。对仅在发生故障时使用的资源的包括要求设备制造商在存储器设备上过度配置资源,这增加了成本。然而,不包括该资源可能导致dram(动态随机存取存储器)设备的降低的可靠性、可访问性和可服务性。

3、除了在单个设备上过度配置资源外,系统级实现还包括用来减少系统错误的过度配置。众所周知,ecc的强度对系统中提供的校验位的数量具有依赖性。为了保证许多系统实现中存储器的可用性,存储器子系统包括多个额外的存储器设备来存储ecc信息。额外的存储器设备可能显著影响系统成本。

技术实现思路

技术特征:

1.一种存储器设备,包括:

2.根据权利要求1所述的存储器设备,其中,所述控制逻辑用于将所述故障存储体的内容复制到所述n个存储体中的r个最高地址用于存储体备用。

3.根据权利要求2所述的存储器设备,其中,n是32,并且其中,所述控制逻辑用于将所述故障存储体的内容复制到行地址的5个高位。

4.根据权利要求1至3中任一项所述的存储器设备,其中,所述控制逻辑用于向主机操作系统(os)指示所述可用存储空间的所述减少。

5.根据权利要求4所述的存储器设备,其中,所述控制逻辑用于向基本输入/输出系统(bios)指示所述可用存储空间的所述减少,以向所述主机os指示所述区域。

6.根据权利要求5所述的存储器设备,其中,所述主机os用于防止在所述区域中存储系统关键数据。

7.根据权利要求4所述的存储器设备,其中,所述主机os用于使所述故障存储体离线。

8.根据权利要求1至3中任一项所述的存储器设备,其中,所述控制逻辑用于响应于来自存储器控制器的命令来复制所述故障存储体的所述内容,其中,所述存储器控制器用于将对所述故障存储体的请求映射到所述区域。

9.一种存储器设备,包括:

10.根据权利要求9所述的存储器设备,其中,写入所述毒位模式包括执行所述缓存线的内容与毒掩码的异或。

11.根据权利要求10所述的存储器设备,其中,所述毒位模式包括用于512个数据位的掩码。

12.根据权利要求10所述的存储器设备,其中,所述缓存线被细分为多个子缓存线,其中,写入所述毒位模式包括向每个细分写入毒位模式。

13.根据权利要求12所述的存储器设备,其中,所述毒模式包括用于4组128个数据位的掩码。

14.根据权利要求9至13中任一项所述的存储器设备,其中,相关联的存储器控制器用于读取所述缓存线,执行所述缓存线与所述毒掩码的异或来生成异或结果,并且确定所述异或结果是否是合法码字。

15.根据权利要求14所述的存储器设备,其中,如果所述异或结果是合法码字,则所述存储器控制器将忽略所述缓存线。

16.根据权利要求14所述的存储器设备,其中,如果所述异或结果不是合法码字,则所述存储器控制器将触发对所述缓存线的错误处理。

17.根据权利要求9至16中任一项所述的存储器设备,其中,所述缓存线的所述内容与所述毒掩码的所述异或将导致可检测的、不可校正的错误(due)。

18.根据权利要求9至17中任一项所述的存储器设备,其中,用于将所述毒位模式写入所述缓存线包括将预定义的毒位模式写入所述缓存线。

19.根据权利要求9至18中任一项所述的存储器设备,其中,所述存储器设备包括双倍数据速率版本5(ddr5)同步动态随机存取存储器(sdram)设备。

20.一种存储器控制器,包括:

21.根据权利要求20所述的存储器控制器,其中,所述故障检测逻辑用于确定所述错误是永久故障的所述结果,包括将全零写入所述码字来确定是否存在不从一翻转的位,并且将全一写入所述码字来确定是否存在不从零翻转的位。

22.根据权利要求21所述的存储器控制器,其中,所述故障检测逻辑用于连续多次重复全零和全一的写入来检测所述永久故障。

23.根据权利要求20至22中任一项所述的存储器控制器,其中,所述ecc逻辑用于将不从一翻转或不从零翻转的位识别为永久故障。

24.根据权利要求20至22中任一项所述的存储器控制器,其中,所述ecc逻辑用于将ecc在所述码字上的所述应用限制到具有错误的存储器设备。

25.根据权利要求24所述的存储器控制器,其中,在将ecc在所述码字上的所述应用限制到具有错误的所述存储器设备之后,如果所述ecc逻辑继续检测到所述码字中的所述错误,则所述存储器控制器将具有永久故障的存储器设备标记为故障设备。

26.根据权利要求20至25中任一项所述的存储器控制器,其中,所述ecc逻辑用于对所述码字执行ecc来生成ecc结果,并且基于关于所述错误是永久故障的所述结果的所述确定来确定所述ecc结果是否是正确的。

27.一种存储器控制器,包括:

28.根据权利要求27所述的存储器控制器,其中,所述码字的所述部分包括所述存储器设备的一半。

29.根据权利要求28所述的存储器控制器,其中,所述一半包括所述存储器设备的右半部分。

30.根据权利要求28所述的存储器控制器,其中,所述一半包括所述存储器设备的左半部分。

31.根据权利要求27至30中任一项所述的存储器控制器,其中,所述存储器设备具有用于交换64位的x4接口,并且其中,所述逻辑用于对所述x4接口的2条信号线执行故障备用。

32.根据权利要求27所述的存储器控制器,其中,所述码字的所述部分包括所述存储器设备的四分之一。

33.根据权利要求32所述的存储器控制器,其中,所述存储器设备具有用于交换64位的x8接口,并且其中,所述逻辑用于对所述x8接口的2条信号线执行故障备用。

34.根据权利要求27至33中任一项所述的存储器控制器,其中,所述ecc逻辑用于在所述特定部分上所述故障备用之后对所述码字执行sddc(单设备数据校正)错误校正。

35.根据权利要求27至34中任一项所述的存储器控制器,其中,为了利用sddc的不可校正的错误的检测,所述ecc逻辑用于利用adddc(自适应双设备数据校正)执行错误校正。

36.根据权利要求27至34中任一项所述的存储器控制器,其中,所述ecc逻辑用于检测所述码字中的另一错误以指示整个存储器设备的故障,并且响应于所述整个存储器设备的故障,所述ecc逻辑用于利用adddc(自适应双设备数据校正)执行错误校正。

37.一种存储器控制器,包括:

38.根据权利要求37所述的存储器控制器,其中,n等于5,其中,所述多个存储器设备包括具有x8接口的4个数据设备和具有x8接口的1个ecc设备。

39.根据权利要求37至38中的任一项所述的存储器控制器,其中,所述多个存储器设备包括具有x4接口的8个数据设备和具有x4接口的1个ecc设备。

40.根据权利要求37至39中任一项所述的存储器控制器,其中,所述第1层位是全矩阵的子矩阵,其中,所述全矩阵包括第1层位加上第2层位。

41.根据权利要求37至40中任一项所述的存储器控制器,其中,对所述存储器设备的写入包括数据的写入、所述第2层位的读取和更新以及所述第2层位的写入。

42.根据权利要求37至41中任一项所述的存储器控制器,还包括:

技术总结

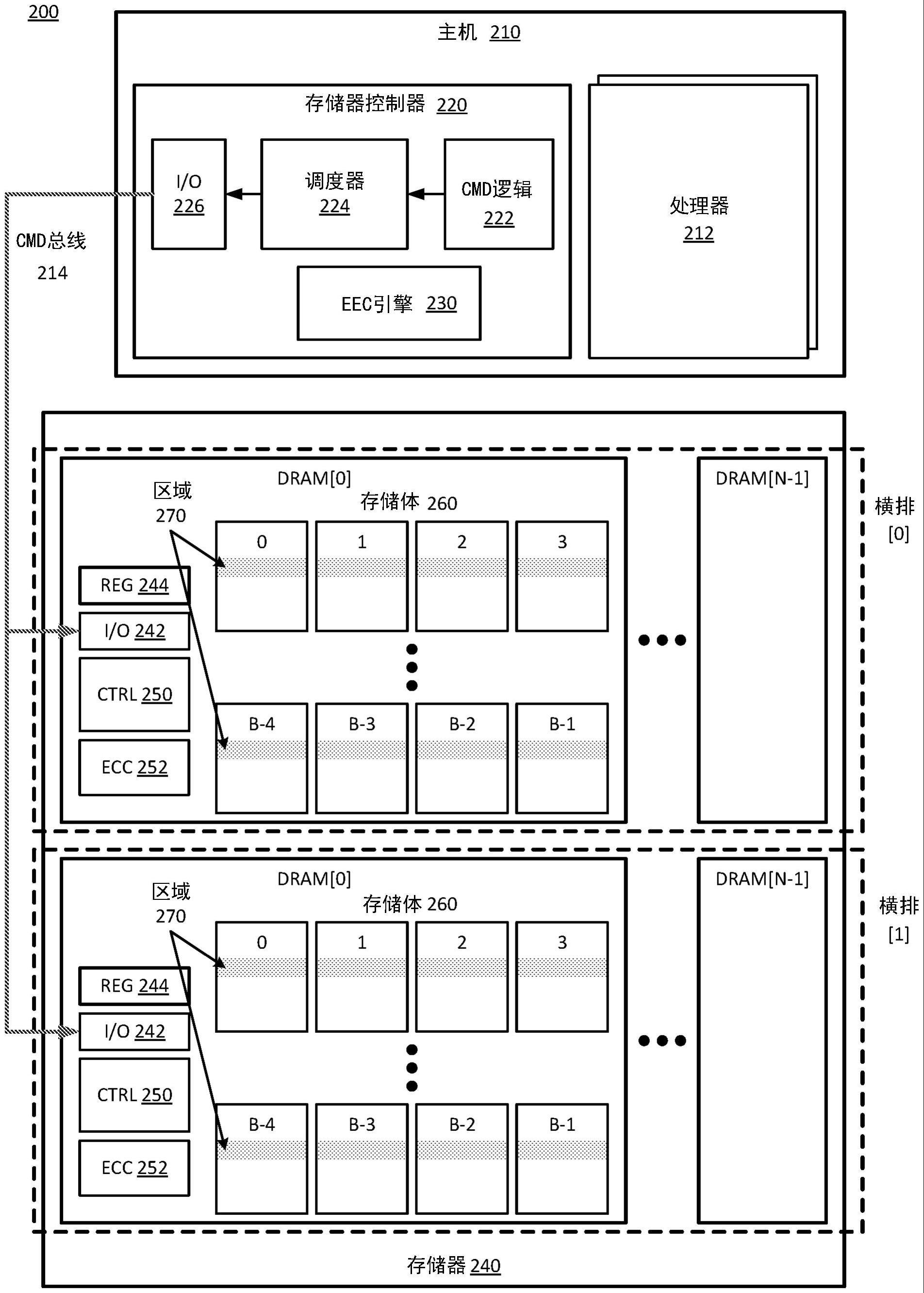

存储器子系统包括具有针对提高系统中的可靠性、可用性和可服务性(RAS)动态分配的空间的存储器设备。错误校验和纠正(ECC)逻辑检测全部或一部分的存储器设备中的错误。响应于错误检测,系统可以动态地执行以下各项中的一项或多项:分配用于备用的活动存储器设备空间来备用故障存储器段;将毒模式写入故障的缓存线以将其标记为故障;执行永久故障检测(PFD)并且基于PFD检测来调整ECC的应用;或者,仅备用设备的一部分并且使另一部分活动(包括基于所备用的部分来调整ECC)。错误检测可以是基于ECC设备的位的,而错误校正可以是基于那些位和在数据设备上存储的附加位的。

技术研发人员:R·阿加瓦尔,H-M·陈,W·P·陈,W·吴,J·凌,K·贝恩斯,K·E·克里斯,D·K·比什,T·伊格扎瓦,J·G·霍尔姆,A·M·鲁多夫,V·辛格,S·曼达瓦

受保护的技术使用者:英特尔公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!