存储系统及操作存储系统的方法与流程

1.本揭露涉及一种存储系统及操作存储系统的方法。

背景技术:

2.诸如计算机、可携式装置、智能手机、物联网(internet of thing;iot)装置等的电子装置的发展已提示对存储装置的增加的需求。一般而言,存储装置可为挥发性存储装置及非挥发性存储装置。挥发性存储装置可在功率经提供时储存数据,但是一旦功率关闭可丢失所储存数据。不同于挥发性存储装置,非挥发性记忆体装置甚在功率关闭之后可保持数据,但可比挥发性存储装置更缓慢。

技术实现要素:

3.根据本揭露的部分实施例,一种存储系统包含多个存储单元、共用字元线驱动器、第一子字元线驱动器、第二子字元线驱动器以及第三子字元线驱动器。存储单元包括第一存储单元群组、第二存储单元群组及第三存储单元群组。共用字元线驱动器用来经由沿一方向延伸的共用字元线将共用控制信号施加至存储单元。第一子字元线驱动器用来经由沿此方向延伸的第一子字元线将第一控制信号施加至第一存储单元群组,其中第一子字元线驱动器邻近于共用字元线驱动器。第二子字元线驱动器用来经由沿此方向延伸的第二子字元线将第二控制信号施加至第二存储单元群组。第三子字元线驱动器用来经由沿此方向延伸的第三子字元线将第三控制信号施加至第三存储单元群组,其中第三子字元线驱动器邻近于第二子字元线驱动器。共用字元线驱动器、第一子字元线驱动器、第一存储单元群组、第二存储单元群组、第二子字元线驱动器、第三子字元线驱动器及第三存储单元群组以彼序列沿此方向设置。

4.根据本揭露的部分实施例,一种存储系统包含多个单位储存电路以及共用字元线驱动器。单位储存电路中的每一个邻接单位储存电路中的邻近的一个。单位储存电路中的每一个包括第一存储单元群组、第二存储单元群组、第一子字元线驱动器及第二子字元线驱动器。第一子字元线驱动器用来经由沿一方向延伸的第一子字元线将第一控制信号施加至第一存储单元群组。第二子字元线驱动器用来经由沿此方向延伸的第二子字元线将第二控制信号施加至第二存储单元群组,其中第一子字元线驱动器、第一存储单元群组、第一子字元线驱动器及第二子字元线驱动器以彼序列沿此方向设置。共用字元线驱动器用来经由沿此方向延伸的共用字元线将共用控制信号施加至单位储存电路,其中共用字元线驱动器邻接单位储存电路中的一个。

5.根据本揭露的部分实施例,一种操作存储系统的方法包含以下步骤。通过共用字元线驱动器,经由共用字元线将共用控制信号施加至多个存储单元群组。通过多个子字元线驱动器,经由对应的子字元线将控制信号施加至来自存储单元群组的个别存储单元群组。通过子字元线驱动器中的第一子字元线驱动器,保护最接近于共用字元线驱动器的来自存储单元群组的第一存储单元群组,其中第一子字元线驱动器邻接第一存储单元群组。

通过子字元线驱动器中的第二子字元线驱动器,保护最远离共用字元线驱动器的来自存储单元群组的第二存储单元群组。

附图说明

6.当与随附附图一起阅读时,根据以下详细描述更好地理解本揭示案的态样。应注意,根据工业中的标准实践,各种特征未按比例描绘。实际上,出于论述的清晰性可任意地增加或减少各种特征的尺寸。

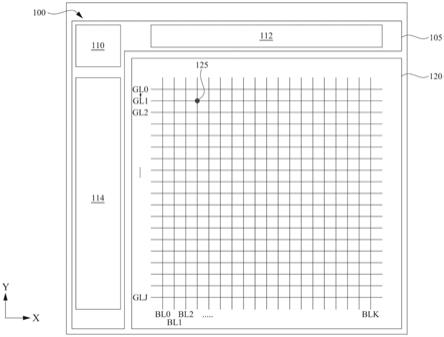

7.图1为根据一个实施例的存储系统的图表;

8.图2为根据一个实施例的包括共用字元线驱动器及多个单位储存电路的存储系统的图表;

9.图3为根据一个实施例的包括共用字元线驱动器及多个单位储存电路的存储系统的图表;

10.图4为根据一些实施例的操作或组配多个存储单元的流程图;

11.图5为根据一些实施例的计算系统的示例性方块图。

12.【符号说明】

13.bl0~blk:位元线

14.gl0~glj:栅极线

15.wl:字元线

16.swlaa,swlba,swlca:子字元线

17.swlab,swlbb,swlcb:子字元线

18.100:存储系统

19.105:存储控制器

20.110:定时控制器

21.112:位元线控制器

22.114:栅极线控制器

23.120:存储阵列

24.125:存储单元/存储单元群组

25.200:存储系统

26.210:共用字元线驱动器

27.250a,250b,250c:单位储存电路

28.252aa,252ab,252ba:子字元线驱动器

29.252bb,252ca,252cb:子字元线驱动器

30.255aa,255ba,255ca:存储阵列

31.255ab,255bb,255cb:存储阵列

32.258a,258b,258c:字元线短柱

33.265aa,265ba,265ca:接口电路

34.265ab,265bb,265cb:接口电路

35.300:存储系统

36.400:方法

37.410,420,430,440:操作

38.500:计算系统

39.505:主机装置

40.510:存储装置

41.515:输入装置

42.520:输出装置

43.525a、525b、525c:接口

44.530a~530n:中央处理单位核心/cpu核心

45.535:标准单元应用程序

46.540:存储控制器

47.545:存储阵列

具体实施方式

48.以下揭示案提供用于实行所提供主题的不同特征的许多不同实施例或实例。以下描述组件及配置的特定实例以简化本揭示案。当然,此等仅为实例且不欲为限制。例如,以下描述中的第二特征上方或第二特征上的第一特征的形成可包括其中第一特征及第二特征是直接接触地形成的实施例,且可亦包括其中额外特征可形成在第一特征与第二特征之间,使得第一特征及第二特征可不直接接触的实施例。另外,本揭示案可在各种实例中重复元件符号及/或字母。此重复是用于简单性及清晰性的目的且实质上并不规定所论述的各种实施例及/或组态之间的关系。

49.此外,为便于描述可在本文中使用诸如“在

……

下方”、“在

……

以下”、“下”、“在

……

以上”、“上”等的空间相对术语,以描述如图中所例示的一个元件或特征与另一元件(多个)或特征(多个)的关系。除附图中所描绘的定向之外,空间相对术语意欲涵盖使用或操作中的装置的不同定向。设备可以其他方式定向(旋转90度或以其他定向)且同样可据此解释本文使用的空间相对描述符。

50.本文所揭示是关于一种存储系统,该存储系统包括单位储存电路。在一个态样中,这些单位储存电路中的每一个邻接这些单位储存电路中的一邻近的一个。在一个态样中,这些单位储存电路中的每一个包括一第一存储单元群组、一第二存储单元群组、一第一子字元线驱动器,及一第二子字元线驱动器。该第一子字元线驱动器可经由沿一方向延伸的一第一子字元线将一第一控制信号施加至该第一存储单元群组。该第二子字元线驱动器可经由沿该方向延伸的一第二子字元线将一第二控制信号施加至该第二存储单元群组。每个子字元线驱动器可包括用来保护一对应存储单元群组的一保护电路。在一个态样中,该存储系统包括一共用字元线驱动器,该共用字元线驱动器邻接这些单位储存电路中的一个且用以经由沿该方向延伸的一共用字元线将一共用控制信号施加至这些单位储存电路。

51.有利地,存储系统可达成若干利益。在一个态样中,所揭示存储系统实行单位的储存电路,该储存电路包括一对子字元线驱动器及介于该对子字元线驱动器之间的一对存储单元群组。因此,最接近于共用字元线驱动器的第一存储单元群组可通过第一子字元线驱动器保护,使得可省略额外保护电路。此外,最远离共用字元线驱动器的最后存储单元群组可通过最后子字元线驱动器保护,使得可省略额外保护电路。通过省略用来保护第一存储

单元群组及最后存储单元群组的额外保护电路,可达成面积效率。此外,共用字元线的长度可经减少,使得共用字元线处的rc负载可经减少以改良多个存储单元的操作速度。

52.图1为根据一个实施例的存储系统100的图表。在一些实施例中,存储系统100包括存储控制器105及存储阵列120。存储阵列120可包括配置于二维或三维阵列中的多个储存电路或存储单元125。每个存储单元125可连接至对应的栅极线gl(或字元线wl)及对应的位元线bl。存储控制器105可根据穿过栅极线gl及位元线bl的电气信号将数据写入至存储阵列120或自该存储阵列读取数据。在其他实施例中,存储系统100包括相较于图1所示的更多、更少,或不同组件。

53.存储阵列120为储存数据的硬件组件。在一个态样中,存储阵列120体现为半导体存储装置。存储阵列120包括多个存储单元125。存储阵列120包括各自在第一方向(例如,x

‑

方向)上延伸的栅极线gl0、gl1

…

glj,及各自在第二方向(例如,y

‑

方向)上延伸的位元线bl0、bl1

…

blk。每个栅极线包括字元线及一或多个控制线。栅极线gl及位元线bl可为导电金属或导电轨。在一个态样中,每个存储单元125连接至对应的栅极线gl及对应的位元线bl,且可根据穿过对应的栅极线gl及对应的位元线bl的电压或电流操作。在一个态样中,每个存储单元125可为铁电场效晶体管(ferroelectric field

‑

effect transistor;fefet)、电阻性存储单元、非挥发性存储单元,或挥发性存储单元。在一些实施例中,存储阵列120包括额外线(例如,选择线、参考线、参考控制线、功率轨等)。以下关于图2至图4提供存储系统100的组态及操作的详细描述。

54.存储控制器105为控制存储阵列120的操作的硬件组件。在一些实施例中,存储控制器105包括位元线控制器112、栅极线控制器114,及定时控制器110。在一个组态中,栅极线控制器114为提供穿过存储阵列120的一或多个栅极线gl的电压或电流的电路,且位元线控制器112为提供或感测穿过存储阵列120的一或多个位元线bl及/或选择线sl的电压或电流的电路。在一个组态中,定时控制器110为提供控制信号或时钟信号以同步化位元线控制器112及栅极线控制器114的操作的电路。位元线控制器112可连接至存储阵列120的位元线bl及/或选择线sl,且栅极线控制器114可连接至存储阵列120的栅极线gl。在一个实例中,为将数据写入至存储单元125,栅极线控制器114经由连接至存储单元125的栅极线gl将电压或电流提供至存储单元125,且位元线控制器112经由连接至存储单元125的位元线bl及/或选择线sl将偏压施加至存储单元125。在一个实例中,为自存储单元125读取数据,栅极线控制器114经由连接至存储单元125的栅极线gl将电压或电流提供至存储单元125,且位元线控制器112经由连接至存储单元125的位元线bl及/或选择线sl感测对应于通过存储单元125储存的数据的电压或电流。在一些实施例中,存储控制器105包括相较于图1中所示的更多、更少,或不同组件。

55.图2为根据一个实施例的包括共用字元线驱动器210及多个单位储存电路250a、250b、250c的存储系统200的图表。在一些实施例中,存储系统200为图1的存储系统100的部分。多个单位储存电路250a、250b、250c中的每一个包括一对子字元线驱动器252及一对存储阵列255。在一个态样中,共用字元线驱动器210及子字元线驱动器252aa、252ab、252ba、252bb、252ca、252cb一起操作,作为图1的栅极线控制器114以组配或操作存储阵列255。在一些实施例中,存储系统200包括相较于图2中所示的更多、更少,或不同组件。

56.在一个组态中,共用字元线驱动器210及单位储存电路250a、250b、250c以彼序列

沿x

‑

方向设置。在一个态样中,共用字元线驱动器210邻接单位储存电路250a的第一侧,且单位储存电路250a的第二侧邻接单位储存电路250b的第一侧。在一个态样中,单位储存电路250b的第二侧邻接单位储存电路250c的第一侧。在一个组态中,共用字元线wl可沿x

‑

方向延伸跨越单位储存电路250a、250b、250c。

57.在一些实施例中,共用字元线驱动器210为可将共用控制信号提供至存储阵列255aa、255ab、255ba、255bb、255ca、255cb的电路或硬件组件。共用控制信号可为用来组配或操作存储阵列255aa、255ab、255ba、255bb、255ca、255cb的字元线电压或字元线脉冲。在一个组态中,共用字元线驱动器210通过共用字元线wl电气地耦接至存储阵列255aa、255ab、255ba、255bb、255ca、255cb。通过经由共用字元线wl将字元线电压或字元线脉冲施加至存储阵列255aa、255ab、255ba、255bb、255ca、255cb,存储阵列255aa、255ab、255ba、255bb、255ca、255cb可储存数据或输出所储存数据。

58.在一些实施例中,每个单位储存电路250x包括一对存储阵列255xa、255xb,及一对子字元线驱动器252xa、252xb。在一个组态中,子字元线驱动器252xa设置在单位储存电路250x的第一侧处且子字元线驱动器252xb设置在单位储存电路250x的第二侧处。存储阵列255xa、255xb可子字元线驱动器252xa、252xb之间,其中存储阵列255xa可邻接子字元线驱动器252xa且存储阵列255xb可邻接子字元线驱动器252xb。每个存储阵列255可包括存储单元群组125。在一个态样中,子字元线驱动器252xa可经由沿x方向延伸跨越第一存储单元群组125的子字元线swlxa电气地耦接至存储阵列255xa中的第一存储单元群组125。在一个态样中,子字元线驱动器252xb可经由沿x方向延伸跨越第二存储单元群组125的子字元线swlxb电气地耦接至存储阵列255xb中的第二存储单元群组125。在一个态样中,每个子字元线swl比共用字元线wl更短。单位储存电路250x可包括介于存储阵列255xa、255xb之间的字元线短柱258x,以电气地去耦或分离子字元线swlxa、swlxb。通过子字元线swlxa、swlxb,子字元线驱动器252xa、252xb可分别组配或操作存储阵列255xa、255xb。

59.在一个态样中,每个子字元线驱动器252xa包括邻接存储阵列255xa的接口电路265xa。接口电路265xa可包括逻辑转换电路,该逻辑转换电路可通过子字元线swlxa接收数字信号且将对应于数字信号的模拟控制信号施加至存储单元群组125。接口电路265xa亦可包括邻接存储阵列255xa的侧的保护电路。保护电路可保护存储阵列255xa中的存储单元群组125。

60.有利地,存储系统200可达成若干利益。在一个态样中,存储系统200包括n数个存储阵列255、n数个子字元线驱动器252,及n/2数个字元线条带258。在一个态样中,最接近于共用字元线驱动器210的第一存储阵列255aa可通过第一子字元线驱动器252aa保护,使得可省略用来保护第一存储阵列255aa的额外保护电路。此外,最远离共用字元线驱动器210的最后存储阵列255cb可通过最后子字元线驱动器252cb保护,使得可省略用来保护最后存储阵列255cb的额外保护电路。通过省略额外保护电路,可达成面积效率。此外,共用字元线wl的长度可经减少,使得共用字元线wl处的rc负载可经减少以改良多个存储单元125的操作速度。

61.图3为根据一个实施例的包括共用字元线驱动器210及多个单位储存电路250a、250b、250c的存储系统300的图表。在一些实施例中,存储系统300体现为图2的存储系统200。

62.在一个态样中,共用字元线驱动器210包括栅极字元线驱动器(gwldv)、局部控制电路(lctrl),及主控制器(mctrl)。栅极字元线驱动器gwldv、逻辑控制电路lctrl,及主控制器mctrl可沿横贯x

‑

方向的y

‑

方向设置。在一个态样中,主控制器mctrl产生全域控制信号以组配多个存储单元125。在一个态样中,逻辑控制电路lctrl产生局部控制信号以分别单独地控制存储单元125的不同部分。在一个态样中,每个栅极字元线驱动器gwldv经由个别共用字元线wl电气地耦接至存储单元125的对应列。栅极字元线驱动器gwldv可产生字元线脉冲且经由共用字元线wl将字元线脉冲施加至存储单元125的对应列。

63.在一个态样中,每个存储阵列255包括存储单元群组125、局部输入/输出接口电路(local input/output interface circuits;lio),及全域输入/输出接口电路(global input/output interface circuit;gio)。存储单元、局部输入/输出接口电路(lio)及全域输入/输出接口电路(gio)可沿y

‑

方向设置。局部输入/输出接口电路(lio)可自局部控制电路lctrl接收局部控制信号,且根据局部控制信号组配或操作存储阵列255中的存储单元群组125的个别部分。全域输入/输出接口电路(gio)可自主控制电路mctrl接收全域控制信号且根据全域控制信号组配或操作存储阵列255中的存储单元群组125。

64.在一个态样中,存储系统300可达成面积效率。例如,最接近于共用字元线驱动器210的第一存储阵列255aa中的存储单元群组125可通过第一子字元线驱动器252aa保护,使得可省略用来保护第一存储阵列255aa中的存储单元群组125的额外保护电路。此外,最远离共用字元线驱动器210的最后存储阵列255cb中的存储单元群组125可通过最后子字元线驱动器252cb保护,使得可省略用来保护最后存储阵列255cb中的存储单元群组125的额外保护电路。通过省略额外保护电路,可达成面积效率。

65.图4为根据一些实施例的组配或操作多个存储单元群组125的方法400的流程图。在一些实施例中,方法400通过共用字元线驱动器210及子字元线驱动器252执行。在一些实施例中,方法400通过其他实体执行。在一些实施例中,方法400包括相较于图4中所示的更多、更少,或不同操作。

66.在操作410中,共用字元线驱动器210通过共用字元线wl将共用控制信号施加至多个存储单元群组125。多个存储阵列群组255可包括个别存储单元群组125。来自多个群组存储单元125的第一存储阵列255aa中的第一存储单元群组125可设置成最接近于共用字元线驱动器210,且来自多个群组存储单元125的第二存储阵列255cb中的第二存储单元群组125可设置成最远离共用字元线驱动器210。共用字元线wl可在一方向(例如,x

‑

方向)上延伸跨越多个存储单元群组125。

67.在操作420中,多个子字元线驱动器252中的每一个通过对应的子字元线swl将控制信号施加至个别存储单元群组125。每个子字元线swl可比共用字元线wl更短。多个子字元线驱动器252可将控制信号施加至个别存储单元群组125,而共用字元线驱动器210将共用控制信号施加至多个存储单元群组125。

68.在一个实例中,第一子字元线驱动器252aa将第一控制信号施加至第一存储阵列255aa中的第一存储单元群组125。第一子字元线驱动器252aa可包括邻接共用字元线驱动器210的第一侧及邻接第一存储阵列255aa中的第一存储单元群组125的第二侧。第一子字元线驱动器252aa可通过延伸跨越第一存储阵列255aa中的第一存储单元群组125的第一子字元线swlaa将第一控制信号施加至第一存储单元群组125。

69.在一个实例中,第二子字元线驱动器252cb将第二控制信号施加至第二存储阵列255cb中的第二存储单元群组125。第二子字元线驱动器252cb可包括邻接第二存储阵列255cb的第一侧。第二子字元线驱动器252cb可设置成相较于第二存储阵列255cb更远离共用字元线驱动器210。第二子字元线驱动器252cb可通过延伸跨越第二存储阵列255cb中的第二存储单元群组125的第二子字元线swlcb将第二控制信号施加至第二存储单元群组125。

70.在操作430中,子字元线驱动器252aa保护第一存储阵列255aa中的第一存储单元群组125。子字元线驱动器252aa可包括邻接第一存储阵列255aa的保护电路。子字元线驱动器252aa的保护电路可保护第一存储阵列255aa中的第一存储单元群组125以免例如由于施加至第一存储单元群组125的过量电压或电流而损坏。

71.在操作440中,子字元线驱动器252cb保护第二存储阵列255cb中的第二存储单元群组125。子字元线驱动器252cb可包括邻接第二存储阵列255cb的保护电路。子字元线驱动器252cb的保护电路可保护第二存储阵列255cb中的第二存储单元群组125以免例如由于施加至第二存储单元群组125的过量电压或电流而损坏。

72.有利地,存储系统200可以面积有效方式加以实行。在一个态样中,每个子字元线驱动器252可包括用来保护对应存储单元群组的保护电路。因此,最接近于共用字元线驱动器210的第一存储阵列255aa中的第一存储单元群组125可通过第一子字元线驱动器252aa保护,使得可省略额外保护电路。此外,最远离共用字元线驱动器210的第二存储阵列255cb中的第二存储单元群组125可通过第二子字元线驱动器252cb保护,使得可省略额外保护电路。通过省略用来保护第一存储单元群组125及第二存储单元群组125的额外保护电路,可达成面积效率。此外,共用字元线wl的长度可经减少,使得共用字元线wl处的rc负载可经减少以改良多个存储单元125的操作速度。

73.现参考图5,示出根据本揭示案的一些实施例的计算系统500的示例性方块图。计算系统500可由电路或布局设计者使用于集成电路设计。如本文所使用的“电路”为诸如电阻器、晶体管、交换机、电池、感应器,或经组配用于实行所要的功能的其他类型的半导体装置的电气组件的互连。计算系统500包括与存储装置510相关联的主机装置505。主机装置505可用以接收来自一或多个输入装置515的输入且将输出提供至一或多个输出装置520。主机装置505可用以分别通过适当的接口525a、525b,及525c与存储装置510、输入装置515,及输出装置520通讯。计算系统500可实行于诸如计算机(例如,桌上型计算机、膝上型计算机、服务器、数据中心等)、平板计算机、个人数字助理、移动装置、其他手持式或可携式装置,或适合于使用主机装置505执行构想设计及/或布局设计的任何其他计算单位的各种计算装置中。

74.输入装置515可包括各种输入技术中的任何输入技术,诸如键盘、尖笔、触控屏幕、鼠标、轨迹球、小键盘、麦克风、语音辨识、运动辨识、远端控制器、输入端口、一或多个按钮、拨号盘、摇杆,及任何其他输入周边设备,该任何其他输入周边设备与主机装置505相关联且该任何其他输入周边设备允许诸如使用者(例如,电路或布局设计者)的外部源将信息(例如,数据)输入主机装置中且将指令发送至主机装置。类似地,输出装置520可包括各种输出技术,诸如外部存储器、列印机、扬声器、显示器、麦克风、发光二极管、头戴式耳机、视频装置,及任何其他输出周边设备,这些任何其他输出周边设备用以接收来自主机装置505

的信息(例如,数据)。输入主机装置505中及/或自主机装置输出的“数据”可包括各种文本数据、电路数据、信号数据、半导体装置数据、图形数据、其组合,或适合于使用计算系统500处理的其他类型的模拟及/或数字数据中的任何者。

75.主机装置505包括一或多个处理单位/处理器,或与一或多个处理单位/处理器相关联,该一或多个处理单位/处理器诸如中央处理单位(central processing unit;cpu)核心530a

‑

530n。cpu核心530a

‑

530n可实行为特定应用集成电路(application specific integrated circuit;asic)、现场可规划门阵列(field programmable gate array;fpga),或任何其他类型的处理单位。cpu核心530a

‑

530n中的每一个可用以执行用于运行主机装置505的一或多个应用程序的指令。在一些实施例中,用来运行一或多个应用程序的指令及数据可储存在存储装置510内。主机装置505亦可用以将运行一或多个应用程序的结果储存在存储装置510内。因而,主机装置505可用以请求存储装置510执行各种操作。例如,主机装置505可请求存储装置510读取数据、写入数据,更新或删除数据,且/或执行管理或其他操作。主机装置505可用以运行的一个此应用程序可为标准单元应用程序535。标准单元应用程序535可为可由主机装置505的使用者使用来使用、创建,或修改电路的标准单元的计算机辅助设计或电子设计自动化软件套的部分。在一些实施例中,用来执行或运行标准单元应用程序535的指令可储存在存储装置510内。标准单元应用程序535可通过cpu核心530a

‑

530n中的一或多个使用来自存储装置510的与标准单元应用程序相关联的指令执行。在一个实例中,标准单元应用程序535允许使用者利用存储系统100或存储系统100的一部分的预产生构想设计及/或布局设计来辅助集成电路设计。在集成电路的布局设计完成之后,可通过制造设计根据布局设计制造多个集成电路,例如,包括存储系统100或存储系统100的一部分。

76.仍参考图5,存储装置510包括存储控制器940,该存储控制器用以自存储阵列545读取数据或将数据写入至该存储阵列。存储阵列545可包括各种挥发性及/或非挥发性存储器。例如,在一些实施例中,存储阵列545可包括nand快闪存储核心。在其他实施例中,存储阵列545可包括nor快闪存储核心、sram核心、动态随机存取存储器(dynamic random access memory;dram)核心、磁阻随机存取存储器(magnetoresistive random access memory;mram)核心、相变存储器(phase change memory;pcm)核心、电阻性随机存取存储器(resistive random access memory;reram)核心、3d xpoint存储核心、铁电随机存取存储器(ferroelectric random

‑

access memory;feram)核心,及适合于在存储阵列内使用的其他类型的存储核心。存储阵列545内的存储器可通过存储控制器540单独地且独立地控制。换言之,存储控制器540可用以与存储阵列545内的每个存储器单独地且独立地通讯。通过与存储阵列545通讯,存储控制器540可用以回应于自主机装置505接收的指令而自存储阵列读取数据或将数据写入至存储阵列。尽管展示为存储装置510的部分,但在一些实施例中,存储控制器540可为主机装置505的部分或计算系统500的另一组件的部分且与存储装置相关联。存储控制器540可经实行为软件、硬件、固件,或其组合中的逻辑电路以执行本文所描述的功能。例如,在一些实施例中,存储控制器540可用以在接收来自主机装置505的请求时,撷取与标准单元应用程序535相关联的指令,这些指令储存在存储装置510的存储阵列545中。

77.将理解,图5中仅示出且描述计算系统500的一些组件。然而,计算系统500可包括

诸如各种电池及功率源、网络接口、路由器、交换机、外部存储系统、控制器等的其他组件。一般而言,计算系统500可包括在执行本文所描述的功能中需要或视为合意的各种硬件、软件,及/或固件组件中的任何者。类似地,主机装置505、输入装置515、输出装置520,及包括存储控制器540及存储阵列545的存储装置510可包括在执行本文所描述的功能中视为必要或合意的其他硬件、软件,及/或固件组件。

78.本描述的一个态样涉及存储系统。在一些实施例中,存储系统包括多个存储单元,该多个存储单元包括第一存储单元群组、第二存储单元群组,及第三存储单元群组。在一些实施例中,存储系统包括用来经由沿一方向延伸的共用字元线将共用控制信号施加至该多个存储单元的共用字元线驱动器。在一些实施例中,存储系统包括用来经由沿该方向延伸的第一子字元线将第一控制信号施加至第一存储单元群组的第一子字元线驱动器。在一些实施例中,第一子字元线驱动器邻近于共用字元线驱动器。在一些实施例中,存储系统包括用来经由沿该方向延伸的第二子字元线将第二控制信号施加至第二存储单元群组的第二子字元线驱动器。在一些实施例中,存储系统包括用来经由沿该方向延伸的第三子字元线将第三控制信号施加至第三存储单元群组的第三子字元线驱动器。在一些实施例中,第三子字元线驱动器邻近于第二子字元线驱动器。在一些实施例中,共用字元线驱动器、第一子字元线驱动器、第一存储单元群组、第二存储单元群组、第二子字元线驱动器、第三子字元线驱动器,及第三存储单元群组以彼序列沿该方向设置。

79.在一些实施例中,第一子字元线驱动器包括第一接口电路,第一接口电路邻接第一存储单元群组,其中第一接口电路保护第一存储单元群组。在一些实施例中,第二子字元线驱动器包括第二接口电路,第二接口电路邻接第二存储单元群组,其中第二接口电路保护第二存储单元群组。在一些实施例中,第三子字元线驱动器包括第三接口电路,第三接口电路邻接第三存储单元群组,其中第三接口电路保护第三存储单元群组。在一些实施例中,存储系统进一步包含字元线条带,其设置在第一存储单元群组与第二存储单元群组之间。在一些实施例中,存储单元包括第四存储单元群组,且存储系统包括第四子字元线驱动器,第四子字元线驱动器用来经由沿此方向延伸的第四子字元线将第四控制信号施加至第四存储单元群组,其中第三存储单元群组、第四存储单元群组及第四子字元线驱动器以彼序列沿此方向设置。在一些实施例中,存储系统进一步包含第一字元线条带和第二字元线条带。第一字元线条带设置在第一存储单元群组与第二存储单元群组之间,而第二字元线条带设置在第三存储单元群组与第四存储单元群组之间。在一些实施例中,第一子字元线、第二子字元线、第三子字元线中的每一个比共用字元线更短。

80.本描述的一个态样涉及存储系统。在一些实施例中,存储系统包括多个单位储存电路,其中该多个单位储存电路中的每一个邻接该多个单位储存电路中的邻近的一个。在一些实施例中,该多个单位储存电路中的每一个包括第一存储单元群组、第二存储单元群组、第一子字元线驱动器,及第二子字元线驱动器。在一些实施例中,第一子字元线驱动器用以经由沿一方向延伸的第一子字元线将第一控制信号施加至第一存储单元群组。在一些实施例中,第二子字元线驱动器用以经由沿该方向延伸的第二子字元线将第二控制信号施加至第二存储单元群组。在一些实施例中,第一子字元线驱动器、第一存储单元群组、第一子字元线驱动器,及第二子字元线驱动器以彼序列沿该方向设置。在一等些实施例中,存储系统包括用来经由沿该方向延伸的共用字元线将共用控制信号施加至该多个单位储存电

路的共用字元线驱动器。在一些实施例中,共用字元线驱动器邻接该多个单位储存电路中的一个。

81.在一些实施例中,第一子字元线驱动器包括第一接口电路,第一接口电路邻接第一存储单元群组,其中第一接口电路保护第一存储单元群组。在一些实施例中,第二子字元线驱动器包括第二接口电路,第二接口电路邻接第二存储单元群组,其中第二接口电路保护第二存储单元群组。在一些实施例中,单位储存电路中的一个的第一子字元线驱动器邻接共用字元线驱动器,且单位储存电路中的一个的第二子字元线驱动器邻接单位储存电路中的另一个的第一子字元线驱动器。在一些实施例中,单位储存电路中的另一个的第二子字元线驱动器邻接单位储存电路中的额外一个的第一子字元线驱动器。在一些实施例中,单位储存电路中的每一个进一步包括字元线条带,字元线条带设置在第一存储单元群组与第二存储单元群组之间。在一些实施例中,第一子字元线及第二子字元线中的每一个比共用字元线更短。

82.本描述的一个态样涉及操作存储系统的方法。在一些实施例中,方法包括通过共用字元线驱动器,经由共用字元线将共用控制信号施加至多个存储单元群组。在一些实施例中,方法包括通过多个子字元线驱动器,经由对应子字元线将控制信号施加至来自该多个存储单元群组的个别存储单元群组。在一些实施例中,方法包括通过该多个子字元线驱动器中的第一子字元线驱动器保护最接近于共用字元线驱动器的来自该多个存储单元群组的第一存储单元群组。在一些实施例中,第一子字元线驱动器邻接第一存储单元群组。在一些实施例中,方法包括通过该多个子字元线驱动器中的第二子字元线驱动器,保护最远离共用字元线驱动器的来自该多个存储单元群组的第二存储单元群组。

83.在一些实施例中,共用字元线沿一方向延伸跨越些存储单元群组。在一些实施例中,子字元线中的每一个沿此方向延伸跨越来自存储单元群组的一个别群组,其中子字元线中的每一个比共用字元线更短。在一些实施例中,操作存储系统的方法进一步包含以下步骤。通过设置在来自存储单元群组的第一存储单元群组与来自存储单元群组的第二存储单元群组之间的字元线条带,将延伸跨越第一存储单元群组的第一子字元线及延伸跨越第二存储单元群组的第二子字元线分离。在一些实施例中,子字元线中的每一个比共用字元线更短。

84.先前内容概括若干实施例的特征,使得熟悉此项技术者可更好地理解本揭示案的态样。熟悉此项技术者应了解,这些熟悉此项技术者可容易地使用本揭示案作为基础,以用于设计或修改用于执行相同目的及/或达成本文引入的实施例的相同优点的其他制程及结构。熟悉此项技术者亦应意识到此等等效构造不脱离本揭示案的精神及范畴,且这些熟悉此项技术者可在不脱离本揭示案的精神及范畴的情况下在本文中做出各种变化、置换,及变更。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1