多次编程非挥发性存储器的存储单元阵列的制作方法

1.本发明涉及一种非挥发性存储器(non

‑

volatile memory)的存储单元阵列(memory cell array),且特别是涉及一种多次编程(multi

‑

time programmable,简称mtp)非挥发性存储器的存储单元阵列。

背景技术:

2.众所周知,非挥发性存储器在断电之后仍旧可以保存其数据内容。一般来说,当非挥发性存储器制造完成并出厂后,使用者即可以编程(program)非挥发性存储器,进而将数据记录在非挥发性存储器中。

3.一般来说,由浮动栅晶体管(floating gate transistor)所组成的存储单元可作为多次编程存储单元(mtp memory cell)。再者,多个多次编程存储单元可组成多次编程非挥发性存储器的存储单元阵列。

4.请参照图1,其所绘示为现有多次编程非挥发性存储器的存储单元阵列示意图。存储单元阵列100包括m

×

n个存储单元c11~cmn,且存储单元阵列100连接至m条字符线wl1~wlm、n条位线bl1~bln以及m条控制线cl1~clm。再者,每个存储单元c11~cmn都包括一浮动栅晶体管。浮动栅晶体管为双栅极浮动栅晶体管(dual gate floating gate transistor),包括一浮动栅极(floating gate)、一控制栅极端(control gate terminal)、一第一漏/源端(source/drain terminal)、一第二漏/源端与一体极端(body terminal)。

5.第一列的n个存储单元c11~c1n中,浮动栅晶体管的控制栅极端连接至字符线wl1,浮动栅晶体管的第一漏/源端连接至控制线cl1,浮动栅晶体管的体极端连接至p型阱区pw1,浮动栅晶体管的第二漏/源端连接至对应的n条位线bl1~bln。第二列的n个存储单元c21~c2n中,浮动栅晶体管的控制栅极端连接至字符线wl2,浮动栅晶体管的第一漏/源端连接至控制线cl2,浮动栅晶体管的体极端连接至p型阱区pw2,浮动栅晶体管的第二漏/源端连接至对应的n条位线bl1~bln。依此类推,第m列的n个存储单元cm1~cmn中,浮动栅晶体管的控制栅极端连接至字符线wlm,浮动栅晶体管的第一漏/源端连接至控制线clm,浮动栅晶体管的体极端连接至p型阱区pwm,浮动栅晶体管的第二漏/源端连接至对应的n条位线bl1~bln。

6.基本上,提供字符线wl1~wlm、位线bl1~bln、控制线cl1~clm以及p型阱区pw1~pwm适当的偏压,可以对存储单元阵列100中的存储单元c11~cmn进行编程动作、抹除动作或读取动作。举例来说,提供动作电压(activated voltage)至字符线wl1,提供不动作电压(inactivated voltage)至其他字符线wl2~wlm,则连接于字符线wl1的第一列即为选定列,并可对选定列的n个存储单元c11~c1n进行编程动作、抹除动作或读取动作。

7.再者,图1中的存储单元阵列100是以n型双栅极浮动栅晶体管为例来做说明。实际上,利用其他类型的浮动栅晶体管也可以组成存储单元,并形成多次编程非挥发性存储器的存储单元阵列。举例来说,利用p型双栅极浮动栅晶体管,或者单栅极浮动栅晶体管

(single gate floating gate transistor)来形成存储单元,并组合成多次编程非挥发性存储器的存储单元阵列。

8.一般来说,存储单元阵列100中一条字符线所连接的n个存储单元可视为一页(page),例如n=128。对存储单元阵列100进行抹除动作时,会以页为单位来进行抹除动作。也就是说,进行抹除动作时,选定列(亦即选定页)的128个存储单元的存储数据都会被抹除。

9.为了能够一次抹除选定列的n存储单元,在设计存储单元阵列100时,会将每个列n个存储单元内的浮动栅晶体管设计在相同的阱区(well region)中。以图1为例,第一列的n个存储单元c11~c1n的浮动栅晶体管设计在p型阱区pw1中。第二列的n个存储单元c21~c2n的浮动栅晶体管设计在p型阱区pw2中。依此类推,第m列的n个存储单元cm1~cmn的浮动栅晶体管设计在p型阱区pwm中。换句话说,每个p型阱区pw1~pwm都为独立的隔离区域(independent isolation regions),不同的p型阱区之间不会互相接触。

10.因此,当存储单元阵列100对第一列的n个存储单元c11~c1n进行抹除动作时,则提供适当的偏压至选定列的p型阱区pw1,即可将选定列n个存储单元c11~c1n的存储数据抹除。另外,由于存储单元阵列100中,其他的p型阱区pw2~pwm未接触于p型阱区pw1,所以存储单元阵列100中其他列的存储单元c21~cmn的存储数据并不会被抹除。

11.基本上,利用半导体制作工艺中的隔离制作工艺(isolation process)可以在半导体基板(substrate)上设计独立的隔离区域。然而,进行隔离制作工艺必须要遵循制作工艺规则(rule),以防止隔离区域之间相互接触。由于存储单元阵列100中的隔离区域数目太多,将造成芯片的尺寸(chip size)变大。

技术实现要素:

12.本发明的主要目的在于提出一种多次编程非挥发性存储器的存储单元阵列。在存储单元阵列中,将不同列存储单元的浮动栅晶体管设计在相同的阱区中,用以降低隔离区域的数目并进而降低芯片尺寸。再者,设计适当的偏压运用于存储单元阵列,将使得存储单元阵列能够正常地进行编程动作、抹除动作或读取动作。

13.本发明为一种多次编程非挥发性存储器的存储单元阵列,该存储单元阵列连接至一第一耦合线、一第二耦合线、一第一抹除线、一第一源极线、一第二源极线、一第一位线与一第二位线,该存储单元阵列包括:包括:一第一存储单元,该第一存储单元连接至该第一耦合线、该第一抹除线、该第一源极线与该第一位线;一第二存储单元,该第二存储单元连接至该第一耦合线、该第一抹除线、该第二源极线与该第二位线;一第三存储单元,该第三存储单元连接至该第二耦合线、该第一抹除线、该第一源极线与该第一位线;以及,一第四存储单元,该第四存储单元连接至该第二耦合线、该第一抹除线、该第二源极线与该第二位线。

14.为了对本发明的上述及其他方面有更佳的了解,下文特举优选实施例,并配合所附的附图,作详细说明如下:

附图说明

15.图1为现有多次编程非挥发性存储器的存储单元阵列示意图;

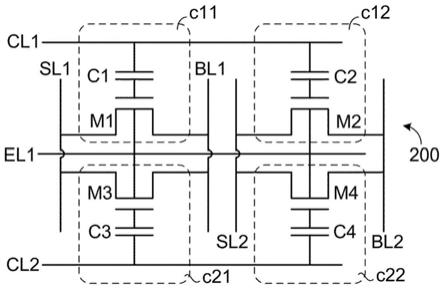

16.图2a至图2d为本发明第一实施例的多次编程非挥发性存储器的存储单元阵列的制作流程图与等效电路图;

17.图3a至图3c为本发明第一实施例存储单元阵列进行各种动作的偏压示意图;

18.图4a至图4b为本发明第二实施例的多次编程非挥发性存储器的存储单元阵列的制作流程图与等效电路图;

19.图5a至图5c为本发明第二实施例存储单元阵列进行各种动作的偏压示意图;

20.图6a至图6b为本发明第三实施例的多次编程非挥发性存储器的存储单元阵列的制作流程图与等效电路图;以及

21.图7a至图7c为本发明第三实施例存储单元阵列进行各种动作的偏压示意图。

22.符号说明

23.100,200,400,600:存储单元阵列

24.205,405,605:深n型阱区

25.211,214,215,218,222,232,411,413,414,415,417,418:n型掺杂区

26.240,250,260,270,440,442,450,452,460,462,470,472:栅极层

27.422,427,432,437,611,612,613,614,615,616,617,618:n型掺杂区

28.640,642,644,650,652,654,660,662,664,670,672,674:栅极层

29.622,627,629,632,637,639:n型掺杂区

具体实施方式

30.本发明设计的存储单元中至少包括一单栅极浮动栅晶体管(single gate floating gate transistor)以及一电容器(capacitor)。也就是说,存储单元可以为一浮动栅晶体管与一电容器的存储单元,可视为1t1c存储单元(1t1c cell)。另外,在本发明的其他实施例中,存储单元可以为一浮动栅晶体管、一选择晶体管(select transistor)与一电容器的存储单元,可视为2t1c存储单元。或者,存储单元可以为一浮动栅晶体管、一选择晶体管、一开关晶体管(switch transistor)与一电容器的存储单元,可视为3t1c存储单元。其中,上述的t代表晶体管,c代表电容器。再者,在存储单元阵列的设计中,将不同列存储单元的浮动栅晶体管设计在相同的阱区中,用以降低隔离区域的数目并进而降低芯片尺寸。再者,设计存储单元阵列的偏压,使得存储单元阵列能够正常地进行编程动作、抹除动作或读取动作。

31.请参照图2a至图2d,其所绘示为本发明第一实施例的多次编程非挥发性存储器的存储单元阵列的制作流程图与等效电路。再者,以下是以2

×

2个存储单元所组成的存储单元阵列200来做说明。当然,本发明并不限定于此,在此领域的技术人员可以根据本发明的内容组成m

×

n个存储单元的存储单元阵列。

32.如图2a所示,在半导体基板(substrate,未绘示)上形成一深n型阱区(deep n well,简称dnw)205。接着,在深n型阱区(dnw)205中形成三个隔离的p型阱区pw1、pw2、pw3,亦即形成三个独立的隔离区域。当然,上述的深n型阱区(dnw)205也可以利用n型埋入层(n

‑

type buried layer,简称nbl)来取代。换句话说,由于深n型阱区(dnw)或者n型埋入层(nbl)都与p型阱区为不同型态(type)的半导体特性,所以利用深n型阱区(dnw)205或者n型埋入层(nbl)可以隔离三个p型阱区pw1、pw2、pw3。

33.如图2b所示,形成多个多晶硅(poly silicon)栅极层240、250、260、270。其中,栅极层240、250由p型阱区pw1延伸至p型阱区pw2,栅极层260、270由p型阱区pw1延伸至p型阱区pw3。基本上,多个多晶硅(poly silicon)栅极层240、250、260、270会作为浮动栅晶体管的浮动栅极(fg)。

34.如图2c所示,以多晶硅(poly silicon)栅极层240、250、260、270作为掩模(mask)进行离子注入制作工艺,形成多个n型掺杂区222、211、214、215、218、232。其中,n型掺杂区211、214、215、218位于p型阱区pw1中,n型掺杂区222位于p型阱区pw2中,n型掺杂区232位于p型阱区pw3中。

35.另外,利用多个金属层连接至n型掺杂区222、211、214、215、218、232以及p型阱区pw1。亦即,源极线sl1连接至n型掺杂区211、位线bl1连接至n型掺杂区214、源极线sl2连接至n型掺杂区215、位线bl2连接至n型掺杂区218、耦合线(coupling line)cl1连接至n型掺杂区222、耦合线cl2连接至n型掺杂区232、抹除线(erase line)el1连接至p型阱区pw1。

36.根据本发明的第一实施例,图2c的存储单元阵列200中包括四个存储单元c11~c22,每个存储单元都包括一浮动栅晶体管与一电容器,且浮动栅晶体管为单栅极浮动栅晶体管(single gate floating gate transistor)。换句话说,第一实施例存储单元阵列200中的存储单元c11~c22为单一晶体管与单一电容器的1t1c存储单元(1t1c cell)。

37.如图2c与图2d所示,在存储单元c11中,n型掺杂区211与214位于栅极层240的两侧,使得栅极层240、n型掺杂区211、n型掺杂区214与p型阱区pw1形成一浮动栅晶体管m1,且栅极层240与n型掺杂区222形成一电容器c1。在存储单元c12中,n型掺杂区215与218位于栅极层250的两侧,使得栅极层250、n型掺杂区215、n型掺杂区218与p型阱区pw1形成一浮动栅晶体管m2,且栅极层250与n型掺杂区222形成一电容器c2。在存储单元c21中,n型掺杂区211与214位于栅极层260的两侧,使得栅极层260、n型掺杂区211、n型掺杂区214与p型阱区pw1形成一浮动栅晶体管m3,且栅极层260与n型掺杂区232形成一电容器c3。在存储单元c22中,n型掺杂区215与218位于栅极层270的两侧,使得栅极层270、n型掺杂区215、n型掺杂区218与p型阱区pw1形成一浮动栅晶体管m4,且栅极层270与n型掺杂区232形成一电容器c4。

38.根据本发明的第一实施例,存储单元阵列200中,不同列的四个存储单元c11~c22的浮动栅晶体管m1~m4都形成于p型阱区pw1中,且p型阱区pw1连接至抹除线el1。换句话说,四个浮动栅晶体管m1~m4的体极端(body terminal)都连接至抹除线el1。

39.如图2d所示,存储单元阵列200包括2

×

2个存储单元c11~c22,且存储单元阵列200连接至耦合线cl1、cl2,源极线sl1、sl2,位线bl1、bl2,抹除线el1。其中,第一列包括两个存储单元c11、c12;第二列包括两个存储单元c21、c22。再者,存储单元阵列200中连接至相同列的多个存储单元可视为一页(page)。

40.在存储单元c11中,浮动栅晶体管m1的第一漏/源端连接至源极线sl1,浮动栅晶体管m1的第二漏/源端连接至位线bl1,浮动栅晶体管m1的体极端连接至抹除线el1,电容器c1的第一端连接至浮动栅晶体管m1的浮动栅极,电容器c1的第二端连接至耦合线cl1。在存储单元c12中,浮动栅晶体管m2的第一漏/源端连接至源极线sl2,浮动栅晶体管m2的第二漏/源端连接至位线bl2,浮动栅晶体管m2的体极端连接至抹除线el1,电容器c2的第一端连接至浮动栅晶体管m2的浮动栅极,电容器c2的第二端连接至耦合线cl1。在存储单元c21中,浮动栅晶体管m3的第一漏/源端连接至源极线sl1,浮动栅晶体管m3的第二漏/源端连接至位

线bl1,浮动栅晶体管m3的体极端连接至抹除线el1,电容器c3的第一端连接至浮动栅晶体管m3的浮动栅极,电容器c3的第二端连接至耦合线cl2。在存储单元c22中,浮动栅晶体管m4的第一漏/源端连接至源极线sl2,浮动栅晶体管m4的第二漏/源端连接至位线bl2,浮动栅晶体管m4的体极端连接至抹除线el1,电容器c4的第一端连接至浮动栅晶体管m4的浮动栅极,电容器c4的第二端连接至耦合线cl2。

41.基本上,提供耦合线cl1、cl2,源极线sl1、sl2,位线bl1、bl2,抹除线el1,p型阱区pw2、pw3,深n型阱区(dnw)205适当的偏压,可以对存储单元阵列200中的存储单元c11~c22进行编程动作、抹除动作或读取动作。以下说明之。

42.请参照图3a至图3c,其所绘示为本发明第一实施例存储单元阵列进行各种动作的偏压示意图。其中,在存储单元阵列200运作时,仅会有一列的存储单元作为一选定列(selected row),其他列则为非选定列(unselected row)。

43.如图3a所示,在编程动作时,耦合线cl1接收编程电压(vpp),耦合线cl2接收最低电压(vss),源极线sl1与位线bl1接收第一供应电压(vd1),源极线sl2与位线bl2接收第二供应电压(vd2),抹除线el1接收最低电压(vss)。除此之外,p型阱区pw2接收的电压相同于耦合线cl1,亦即编程电压(vpp)。p型阱区pw3接收的电压相同于耦合线cl2,亦即最低电压(vss)。深n型阱区(dnw)接收编程电压(vpp)。其中,编程电压(vpp)大于第二供应电压(vd2),第二供应电压(vd2)大于第一供应电压(vd1),第一供应电压(vd1)大于等于最低电压(vss),且最低电压(vss)小于等于0v。举例来说,编程电压(vpp)为8v,第二供应电压(vd2)为5v,第一供应电压(vd1)为1v,最低电压(vss)为0v。当然,第一供应电压(vd1)也可以相同于最低电压(vss)。

44.在编程动作时,由于耦合线cl1接收编程电压(vpp)且耦合线cl2接收最低电压(vss),所以存储单元阵列200中连接于耦合线cl1的第一列为选定列,连接于耦合线cl2的第二列为非选定列。非选定列中的存储单元c21、c22无法被编程。

45.再者,在选定列中,源极线sl1与位线bl1接收第一供应电压(vd1),所以热载流子(例如电子)经由fn隧道(fowler

‑

nordheim tunneling)效应注入存储单元c11中浮动栅晶体管m1的浮动栅极,使得存储单元c11被编程为第一存储状态。另外,源极线sl2与位线bl2接收第二供应电压(vd2),所以热载流子(例如电子)不会注入存储单元c12中浮动栅晶体管m2的浮动栅极,使得存储单元c12被编程为第二存储状态。换言之,经由适当地控制源极线sl1、sl2以及位线bl1、bl2的电压,可以将选定列上的存储单元c11、c12编程为第一存储状态或者第二存储状态。

46.如图3b所示,在抹除动作时,耦合线cl1接收最低电压(vss),耦合线cl2接收抹除电压(vee),源极线sl1、sl2与位线bl1、bl2接收抹除电压(vee),抹除线el1接收抹除电压(vee)。除此之外,p型阱区pw2接收的电压相同于耦合线cl1,亦即最低电压(vss)。p型阱区pw3接收的电压相同于耦合线cl2,亦即抹除电压(vee)。深n型阱区(dnw)接收抹除电压(vee)。其中,抹除电压(vee)大于最低电压(vss),且最低电压(vss)小于等于0v。举例来说,抹除电压(vee)为12v,最低电压(vss)为0v。

47.在抹除动作时,由于耦合线cl1接收最低电压(vss)且耦合线cl2接收抹除电压(vee),所以存储单元阵列200中连接于耦合线cl1的第一列为选定列,连接于耦合线cl2的第二列为非选定列。非选定列中的存储单元c21、c22无法被抹除。

48.再者,在选定列中,抹除线el1、源极线sl1、sl2与位线bl1、bl2接收抹除电压(vee),所以热载流子(例如电子)经由fn隧道(fowler

‑

nordheim tunneling)效应退出存储单元c11、c12中浮动栅晶体管m1、m2的浮动栅极,使得存储单元c11、c12被抹除为第二存储状态。换言之,在抹除动作时,选定列的所有存储单元(亦即选定页的存储单元)会被抹除为第二存储状态。

49.如图3c所示,在读取动作时,耦合线cl1接收第一供应电压(vd1),耦合线cl2接收最低电压(vss),源极线sl1接收第一供应电压(vd1),位线bl1接收第二供应电压(vd2),源极线sl2与位线bl2接收第一供应电压(vd1),抹除线el1接收第一供应电压(vd1)。除此之外,p型阱区pw2接收的电压相同于耦合线cl1,亦即第一供应电压(vd1)。p型阱区pw3接收的电压相同于耦合线cl2,亦即最低电压(vss)。深n型阱区(dnw)接收第二供应电压(vd2)。其中,第二供应电压(vd2)大于第一供应电压(vd1),第一供应电压(vd1)大于等于最低电压(vss),且最低电压(vss)小于等于0v。举例来说,第二供应电压(vd2)为5v,第一供应电压(vd1)为1v,最低电压(vss)为0v。

50.在读取动作时,由于耦合线cl1接收第一供应电压(vd1)且耦合线cl2接收最低电压(vss),所以存储单元阵列200中连接于耦合线cl1的第一列为选定列,连接于耦合线cl2的第二列为非选定列。非选定列中的存储单元c21、c22无法被读取。

51.再者,在选定列中,源极线sl1接收第一供应电压(vd1),位线bl1接收第二供应电压(vd2),所以存储单元c11会产生一读取电流(read current),由位线bl1流经浮动栅晶体管m1至源极线sl1。再者,读取电流的大小是根据存储单元c11的存储状态来决定,例如第一存储状态的读取电流小于第二存储状态的读取电流。换句话说,在读取动作时,根据存储单元c11所产生的读取电流即可判断存储单元c11的存储状态。

52.另外,由于源极线sl2与位线bl2接收第一供应电压(vd1),所以存储单元c12不会产生读取电流(read current)。也就是说,经由适当地偏压,可以控制选定列上的任一存储单元产生读取电流或者不产生读取电流,并判断该存储单元的存储状态。

53.由以上的说明可知,在第一实施例的存储单元阵列200的设计中,不同列存储单元的浮动栅晶体管设计于相同的p型阱区pw1,因此可以大幅减少芯片的尺寸。再者,虽然不同列存储单元的浮动栅晶体管设计在相同的p型阱区pw1,在进行读取动作时,仅有选定列(选定页)存储单元的存储数据可以被读取,非选定列(非选定页)存储单元的数据并不会被读取。

54.请参照图4a与图4b,其所绘示为本发明第二实施例的多次编程非挥发性存储器的存储单元阵列与等效电路。再者,以下是以2

×

2个存储单元所组成的存储单元阵列400来做说明。当然,本发明并不限定于此,在此领域的技术人员可以根据本发明的内容组成m

×

n个存储单元的存储单元阵列。另外,第二实施例与第一实施例的制作流程类似,以下仅简单介绍之。

55.如图4a所示,在半导体基板(substrate,未绘示)上形成一深n型阱区(dnw)405。接着,在深n型阱区(dnw)405中形成三个隔离的p型阱区pw1、pw2、pw3,亦即三个独立的隔离区域。相同地,上述的深n型阱区(dnw)405也可以利用n型埋入层(nbl)来取代。

56.根据本发明的第二实施例,形成多个多晶硅(poly silicon)栅极层440、442、450、452、460、462、470、472。其中,栅极层440、450由p型阱区pw1延伸至p型阱区pw2,栅极层460、

470由p型阱区pw1延伸至p型阱区pw3。基本上,多晶硅(poly silicon)栅极层440、450、460、470会作为浮动栅晶体管的浮动栅极(fg)。再者,栅极层442位于p型阱区pw1中,栅极层440的一侧;栅极层452位于p型阱区pw1中,栅极层450的一侧;栅极层462位于p型阱区pw1中,栅极层460的一侧;栅极层472位于p型阱区pw1中,栅极层470的一侧。

57.接着,以多晶硅(poly silicon)栅极层440、442、450、452、460、462、470、472作为掩模(mask)进行离子注入制作工艺,形成多个n型掺杂区422、411、413、414、415、417、418、432、437、427。其中,n型掺杂区411、413、414、415、417、418、437、427位于p型阱区pw1中,n型掺杂区422位于p型阱区pw2中,n型掺杂区432位于p型阱区pw3中。

58.另外,利用多个金属层连接至n型掺杂区422、411、414、415、418、432以及p型阱区pw1。亦即,源极线sl1连接至n型掺杂区411、位线bl1连接至n型掺杂区414、源极线sl2连接至n型掺杂区415、位线bl2连接至n型掺杂区418、耦合线(coupling line)cl1连接至n型掺杂区422、耦合线cl2连接至n型掺杂区432、抹除线(erase line)el1连接至p型阱区pw1。再者,利用多个金属层连接至栅极层442、452、462、472。亦即,字符线wl1连接至栅极层442与452,字符线wl2连接至栅极层462与472。

59.根据本发明的第二实施例,图4a的存储单元阵列400中包括四个存储单元c11~c22,每个存储单元都包括一浮动栅晶体管、一选择晶体管(select transistor)与一电容器,且浮动栅晶体管为单栅极浮动栅晶体管(single gate floating gate transistor)。换句话说,第二实施例存储单元阵列400中的存储单元c11~c22为二晶体管与单一电容器的2t1c存储单元(2t1c cell)。

60.如图4a与图4b所示,在存储单元c11中,n型掺杂区411与413位于栅极层440的两侧,n型掺杂区413与414位于栅极层442的两侧。因此,栅极层440、n型掺杂区411、n型掺杂区413与p型阱区pw1形成一浮动栅晶体管m1;栅极层442、n型掺杂区413、n型掺杂区414与p型阱区pw1形成一选择晶体管ma;且栅极层440与n型掺杂区422形成一电容器c1。在存储单元c12中,n型掺杂区415与417位于栅极层450的两侧,n型掺杂区417与418位于栅极层452的两侧。因此,栅极层450、n型掺杂区415、n型掺杂区417与p型阱区pw1形成一浮动栅晶体管m2;栅极层452、n型掺杂区417、n型掺杂区418与p型阱区pw1形成一选择晶体管mb;且栅极层450与n型掺杂区422形成一电容器c2。在存储单元c21中,n型掺杂区411与437位于栅极层460的两侧,n型掺杂区437与414位于栅极层462的两侧。因此,栅极层460、n型掺杂区411、n型掺杂区437与p型阱区pw1形成一浮动栅晶体管m3;栅极层462、n型掺杂区437、n型掺杂区414与p型阱区pw1形成一选择晶体管mc;且栅极层460与n型掺杂区432形成一电容器c3。在存储单元c22中,n型掺杂区415与427位于栅极层470的两侧,n型掺杂区427与418位于栅极层472的两侧。因此,栅极层470、n型掺杂区415、n型掺杂区427与p型阱区pw1形成一浮动栅晶体管m4;栅极层472、n型掺杂区427、n型掺杂区418与p型阱区pw1形成一选择晶体管md;且栅极层470与n型掺杂区432形成一电容器c4。

61.根据本发明的第二实施例,存储单元阵列400中,不同列的四个存储单元c11~c22的浮动栅晶体管m1~m4与选择晶体管ma~md都形成于p型阱区pw1中,且p型阱区pw1连接至抹除线el1。换句话说,四个浮动栅晶体管m1~m4与四个选择晶体管ma~md的体极端(body terminal)都连接至抹除线el1。

62.如图4b所示,存储单元阵列400包括2

×

2个存储单元c11~c22,且存储单元阵列

400连接至字符线wl1、wl2,耦合线cl1、cl2,源极线sl1、sl2,位线bl1、bl2,抹除线el1。其中,第一列包括两个存储单元c11、c12;第二列包括两个存储单元c21、c22。再者,存储单元阵列400中连接至相同列的多个存储单元可视为一页(page)。

63.在存储单元c11中,浮动栅晶体管m1的第一漏/源端连接至源极线sl1,浮动栅晶体管m1的第二漏/源端连接至选择晶体管ma的第一漏/源端,选择晶体管ma的第二漏/源端连接至位线bl1,选择晶体管ma的栅极端连接至字符线wl1,浮动栅晶体管m1与选择晶体管ma的体极端连接至抹除线el1,电容器c1的第一端连接至浮动栅晶体管m1的浮动栅极,电容器c1的第二端连接至耦合线cl1。在存储单元c12中,浮动栅晶体管m2的第一漏/源端连接至源极线sl2,浮动栅晶体管m2的第二漏/源端连接至选择晶体管mb的第一漏/源端,选择晶体管mb的第二漏/源端连接至位线bl2,选择晶体管mb的栅极端连接至字符线wl1,浮动栅晶体管m2与选择晶体管mb的体极端连接至抹除线el1,电容器c2的第一端连接至浮动栅晶体管m2的浮动栅极,电容器c2的第二端连接至耦合线cl1。在存储单元c21中,浮动栅晶体管m3的第一漏/源端连接至源极线sl1,浮动栅晶体管m3的第二漏/源端连接至选择晶体管mc的第一漏/源端,选择晶体管mc的第二漏/源端连接至位线bl1,选择晶体管mc的栅极端连接至字符线wl2,浮动栅晶体管m3与选择晶体管mc的体极端连接至抹除线el1,电容器c3的第一端连接至浮动栅晶体管m3的浮动栅极,电容器c3的第二端连接至耦合线cl2。在存储单元c22中,浮动栅晶体管m4的第一漏/源端连接至源极线sl2,浮动栅晶体管m4的第二漏/源端连接至选择晶体管md的第一漏/源端,选择晶体管md的第二漏/源端连接至位线bl2,选择晶体管md的栅极端连接至字符线wl2,浮动栅晶体管m4与选择晶体管md的体极端连接至抹除线el1,电容器c4的第一端连接至浮动栅晶体管m4的浮动栅极,电容器c4的第二端连接至耦合线cl2。

64.基本上,提供字符线wl1、wl2,耦合线cl1、cl2,源极线sl1、sl2,位线bl1、bl2,抹除线el1,p型阱区pw2、pw3,深n型阱区(dnw)405适当的偏压,可以对存储单元阵列400中的存储单元c11~c22进行编程动作、抹除动作或读取动作。以下说明之。

65.请参照图5a至图5c,其所绘示为本发明第二实施例存储单元阵列进行各种动作的偏压示意图。其中,在存储单元阵列400运作时,仅会有一列的存储单元作为一选定列(selected row),其他列则为非选定列(unselected row)。

66.如图5a所示,在编程动作时,耦合线cl1接收编程电压(vpp),耦合线cl2接收最低电压(vss),字符线wl1接收第二供应电压(vd2),字符线wl2接收最低电压(vss),源极线sl1与位线bl1接收第一供应电压(vd1),源极线sl2与位线bl2接收第二供应电压(vd2),抹除线el1接收最低电压(vss)。除此之外,p型阱区pw2接收的电压相同于耦合线cl1,亦即编程电压(vpp)。p型阱区pw3接收的电压相同于耦合线cl2,亦即最低电压(vss)。深n型阱区(dnw)接收编程电压(vpp)。其中,编程电压(vpp)大于第二供应电压(vd2),第二供应电压(vd2)大于第一供应电压(vd1),第一供应电压(vd1)大于等于最低电压(vss),且最低电压(vss)小于等于0v。举例来说,编程电压(vpp)为8v,第二供应电压(vd2)为5v,第一供应电压(vd1)为1v。

67.在编程动作时,由于耦合线cl1接收编程电压(vpp)且字符线wl1接收第二供应电压(vd2),所以存储单元阵列400中连接于耦合线cl1与字符线wl1的第一列为选定列。再者,由于耦合线cl2接收最低电压(vss)且字符线wl2接收最低电压(vss),所以连接于耦合线

cl2与字符线wl2的第二列为非选定列,且非选定列中的存储单元c21、c22无法被编程。

68.再者,在选定列中,源极线sl1与位线bl1接收第一供应电压(vd1)且字符线wl1接收第二供应电压(vd2),所以选择晶体管ma开启(turn on),热载流子(例如电子)经由fn隧道(fowler

‑

nordheim tunneling)效应注入存储单元c11中浮动栅晶体管m1的浮动栅极,使得存储单元c11被编程为第一存储状态。另外,源极线sl2与位线bl2接收第二供应电压(vd2)且字符线wl1接收第二供应电压(vd2),所以选择晶体管mb关闭(turn off),热载流子(例如电子)不会注入存储单元c12中浮动栅晶体管m2的浮动栅极,使得存储单元c12被编程为第二存储状态。换言之,经由适当地控制源极线sl1、sl2以及位线bl1、bl2的电压,可以将选定列上的存储单元c11、c12编程为第一存储状态或者第二存储状态。

69.如图5b所示,在抹除动作时,耦合线cl1接收最低电压(vss),耦合线cl2接收抹除电压(vee),字符线wl1与字符线wl2接收第一供应电压(vd1),源极线sl1、sl2与位线bl1、bl2接收抹除电压(vee),抹除线el1接收抹除电压(vee)。除此之外,p型阱区pw2接收的电压相同于耦合线cl1,亦即最低电压(vss)。p型阱区pw3接收的电压相同于耦合线cl2,亦即抹除电压(vee)。深n型阱区(dnw)接收抹除电压(vee)。其中,抹除电压(vee)大于最低电压(vss),且最低电压(vss)小于等于0v。举例来说,抹除电压(vee)为12v,最低电压(vss)为0v。

70.在抹除动作时,由于耦合线cl1接收最低电压(vss)且耦合线cl2接收抹除电压(vee),所以存储单元阵列400中连接于耦合线cl1的第一列为选定列,连接于耦合线cl2的第二列为非选定列。非选定列中的存储单元c21、c22无法被抹除。

71.再者,在选定列中,抹除线el1、源极线sl1、sl2与位线bl1、bl2接收抹除电压(vee),所以热载流子(例如电子)经由fn隧道(fowler

‑

nordheim tunneling)效应退出存储单元c11、c12中浮动栅晶体管m1、m2的浮动栅极,使得存储单元c11、c12被抹除为第二存储状态。换言之,在抹除动作时,选定列的所有存储单元(亦即选定页的存储单元)会被抹除为第二存储状态。

72.如图5c所示,在读取动作时,耦合线cl1接收第一供应电压(vd1),耦合线cl2接收第一供应电压(vd1),字符线wl1接收第二供应电压(vd2),字符线wl2接收最低电压(vss),源极线sl1接收第一供应电压(vd1),位线bl1接收第二供应电压(vd2),源极线sl2与位线bl2接收第一供应电压(vd1),抹除线el1接收第一供应电压(vd1)。除此之外,p型阱区pw2接收的电压相同于耦合线cl1,亦即第一供应电压(vd1)。p型阱区pw3接收的电压相同于耦合线cl2,亦即第一供应电压(vd1)。深n型阱区(dnw)接收第二供应电压(vd2)。其中,第二供应电压(vd2)大于第一供应电压(vd1),第一供应电压(vd1)大于等于最低电压(vss),且最低电压(vss)小于等于0v。举例来说,第二供应电压(vd2)为5v,第一供应电压(vd1)为1v,最低电压(vss)为0v。

73.在读取动作时,由于耦合线cl1接收第一供应电压(vd1)且字符线wl1接收第二供应电压(vd2),所以存储单元阵列400中连接于耦合线cl1的第一列为选定列。再者,由于耦合线cl2接收第一供应电压(vd1)且字符线wl2接收最低电压(vss),所以存储单元阵列400中连接于耦合线cl2的第二列为非选定列,且非选定列中的存储单元c21、c22无法被读取。

74.再者,在选定列中,字符线wl1接收第二供应电压(vd2),源极线sl1接收第一供应电压(vd1),位线bl1接收第二供应电压(vd2),所以选择晶体管ma开启,存储单元c11会产生

一读取电流(read current),由位线bl1流经浮动栅极m1至源极线sl1。再者,读取电流的大小是根据存储单元c11的存储状态来决定,例如第一存储状态的读取电流小于第二存储状态的读取电流。换句话说,在读取动作时,根据存储单元c11所产生的读取电流即可判断存储单元c11的存储状态。

75.另外,由于字符线wl1接收第二供应电压(vd2),源极线sl2与位线bl2接收第一供应电压(vd1),选择晶体管mb关闭,存储单元c12不会产生读取电流(read current)。也就是说,经由适当地偏压,可以控制选定列上的任一存储单元产生读取电流或者不产生读取电流,并判断该存储单元的存储状态。

76.由以上的说明可知,在第二实施例的存储单元阵列400的设计中,不同列存储单元的浮动栅晶体管与选择晶体管都设计于相同的p型阱区pw1,因此可以大幅减少芯片的尺寸。再者,虽然不同列存储单元的浮动栅晶体管设计在相同的p型阱区pw1,在进行读取动作时,仅有选定列(选定页)存储单元的存储数据可以被读取,非选定列(非选定页)存储单元的数据并不会被读取。

77.请参照图6a与图6b,其所绘示为本发明第三实施例的多次编程非挥发性存储器的存储单元阵列与等效电路。再者,以下是以2

×

2个存储单元所组成的存储单元阵列600来做说明。当然,本发明并不限定于此,在此领域的技术人员可以根据本发明的内容组成m

×

n个存储单元的存储单元阵列。另外,第三实施例与第一实施例的制作流程类似,以下仅简单介绍之。

78.如图6a所示,在半导体基板(substrate,未绘示)上形成一深n型阱区(dnw)605。接着,在深n型阱区(dnw)605中形成三个隔离的p型阱区pw1、pw2、pw3,亦即三个独立的隔离区域。相同地,上述的深n型阱区(dnw)605也可以利用n型埋入层(nbl)来取代。

79.根据本发明的第三实施例,形成多个多晶硅(poly silicon)栅极层640、642、644、650、652、654、660、662、664、670、672、674。其中,栅极层640、650由p型阱区pw1延伸至p型阱区pw2,栅极层660、670由p型阱区pw1延伸至p型阱区pw3。基本上,多晶硅(poly silicon)栅极层640、650、660、670会作为浮动栅晶体管的浮动栅极(fg)。再者,栅极层642与644位于p型阱区pw1中,栅极层640的两侧;栅极层652、654位于p型阱区pw1中,栅极层650的两侧;栅极层662、664位于p型阱区pw1中,栅极层660的两侧;栅极层672、674位于p型阱区pw1中,栅极层670的两侧。

80.接着,以多晶硅(poly silicon)栅极层640、642、644、650、652、654、660、662、664、670、672、674作为掩模(mask)进行离子注入制作工艺,形成多个n型掺杂区622、611~618、627、629、637、639、632。其中,n型掺杂区611~618、627、629、637、639位于p型阱区pw1中,n型掺杂区622位于p型阱区pw2中,n型掺杂区632位于p型阱区pw3中。

81.另外,利用多个金属层连接至n型掺杂区622、611、614、615、618、632以及p型阱区pw1。亦即,源极线sl1连接至n型掺杂区611、位线bl1连接至n型掺杂区614、源极线sl2连接至n型掺杂区615、位线bl2连接至n型掺杂区618、耦合线(coupling line)cl1连接至n型掺杂区622、耦合线cl2连接至n型掺杂区632、抹除线(erase line)el1连接至p型阱区pw1。再者,利用多个金属层连接至栅极层642、644、652、654、662、664、672、674。亦即,字符线wl1连接至栅极层642、644、652与654,字符线wl2连接至栅极层662、664、672与674。

82.根据本发明的第三实施例,图6a的存储单元阵列600中包括四个存储单元c11~

c22,每个存储单元都包括一浮动栅晶体管、一开关晶体管、一选择晶体管与一电容器,且浮动栅晶体管为单栅极浮动栅晶体管(single gate floating gate transistor)。换句话说,第三实施例存储单元阵列600中的存储单元c11~c22为三晶体管与单一电容器的3t1c存储单元(3t1c cell)。

83.如图6a与图6b所示,在存储单元c11中,n型掺杂区611与612位于栅极层644的两侧,n型掺杂区612与613位于栅极层640的两侧,n型掺杂区613与614位于栅极层642的两侧。因此,栅极层644、n型掺杂区611、n型掺杂区612与p型阱区pw1形成一开关晶体管me,栅极层640、n型掺杂区612、n型掺杂区613与p型阱区pw1形成一浮动栅晶体管m1;栅极层642、n型掺杂区613、n型掺杂区614与p型阱区pw1形成一选择晶体管ma;且栅极层640与n型掺杂区622形成一电容器c1。另外,存储单元c12、c21、c22的结构与存储单元c11类似,此处不再赘述。

84.根据本发明的第三实施例,存储单元阵列600中,不同列的四个存储单元c11~c22的浮动栅晶体管m1~m4、开关晶体管me~mh与选择晶体管ma~md都形成于p型阱区pw1中,且p型阱区pw1连接至抹除线el1。换句话说,四个浮动栅晶体管m1~m4、四个开关晶体管me~mh与四个选择晶体管ma~md的体极端(body terminal)都连接至抹除线el1。

85.如图6b所示,存储单元阵列600包括2

×

2个存储单元c11~c22,且存储单元阵列600连接至字符线wl1、wl2,耦合线cl1、cl2,源极线sl1、sl2,位线bl1、bl2,抹除线el1。其中,第一列包括两个存储单元c11、c12;第二列包括两个存储单元c21、c22。再者,存储单元阵列600中连接至相同列的多个存储单元可视为一页(page)。

86.在存储单元c11中,开关晶体管me的第一漏/源端连接至源极线sl1,开关晶体管me的栅极端连接至字符线wl1,浮动栅晶体管m1的第一漏/源端连接至开关晶体管me的第二漏/源端,浮动栅晶体管m1的第二漏/源端连接至选择晶体管ma的第一漏/源端,选择晶体管ma的第二漏/源端连接至位线bl1,选择晶体管ma的栅极端连接至字符线wl1,开关晶体管me、浮动栅晶体管m1与选择晶体管ma的体极端连接至抹除线el1,电容器c1的第一端连接至浮动栅晶体管m1的浮动栅极,电容器c1的第二端连接至耦合线cl1。另外,存储单元c12、c21、c22的连接关系类似于存储单元c11类似,此处不再赘述。

87.基本上,提供字符线wl1、wl2,耦合线cl1、cl2,源极线sl1、sl2,位线bl1、bl2,抹除线el1,p型阱区pw2、pw3,深n型阱区(dnw)605适当的偏压,可以对存储单元阵列600中的存储单元c11~c22进行编程动作、抹除动作或读取动作。以下说明之。

88.请参照图7a至图7c,其所绘示为本发明第三实施例存储单元阵列600进行各种动作的偏压示意图。其中,在存储单元阵列600运作时,仅会有一列的存储单元作为一选定列(selected row),其他列则为非选定列(unselected row)。

89.如图7a所示,在编程动作时,耦合线cl1接收编程电压(vpp),耦合线cl2接收最低电压(vss),字符线wl1接收第二供应电压(vd2),字符线wl2接收最低电压(vss),源极线sl1与位线bl1接收第一供应电压(vd1),源极线sl2与位线bl2接收第二供应电压(vd2),抹除线el1接收最低电压(vss)。除此之外,p型阱区pw2接收的电压相同于耦合线cl1,亦即编程电压(vpp)。p型阱区pw3接收的电压相同于耦合线cl2,亦即最低电压(vss)。深n型阱区(dnw)接收编程电压(vpp)。其中,编程电压(vpp)大于第二供应电压(vd2),第二供应电压(vd2)大于第一供应电压(vd1),第一供应电压(vd1)大于等于最低电压(vss),且最低电压(vss)小于等于0v。举例来说,编程电压(vpp)为8v,第二供应电压(vd2)为5v,第一供应电压(vd1)为

1v,最低电压(vss)为0v。

90.在编程动作时,由于耦合线cl1接收编程电压(vpp)且字符线wl1接收第二供应电压(vd2),所以存储单元阵列600中连接于耦合线cl1与字符线wl1的第一列为选定列。再者,由于耦合线cl2接收最低电压(vss)且字符线wl2接收最低电压(vss),所以连接于耦合线cl2与字符线wl2的第二列为非选定列,且非选定列中的存储单元c21、c22无法被编程。

91.再者,在选定列中,源极线sl1与位线bl1接收第一供应电压(vd1)且字符线wl1接收第二供应电压(vd2),所以开关晶体管me与选择晶体管ma开启(turn on),热载流子(例如电子)经由fn隧道(fowler

‑

nordheim tunneling)效应注入存储单元c11中浮动栅晶体管m1的浮动栅极,使得存储单元c11被编程为第一存储状态。另外,源极线sl2与位线bl2接收第二供应电压(vd2)且字符线wl1接收第二供应电压(vd2),所以开关晶体管mf与选择晶体管mb关闭(turn off),热载流子(例如电子)不会注入存储单元c12中浮动栅晶体管m2的浮动栅极,使得存储单元c12被编程为第二存储状态。换言之,经由适当地控制源极线sl1、sl2以及位线bl1、bl2的电压,可以将选定列上的存储单元c11、c12编程为第一存储状态或者第二存储状态。

92.如图7b所示,在抹除动作时,耦合线cl1接收最低电压(vss),耦合线cl2接收抹除电压(vee),字符线wl1与字符线wl2接收第一供应电压(vd1),源极线sl1、sl2与位线bl1、bl2接收抹除电压(vee),抹除线el1接收抹除电压(vee)。除此之外,p型阱区pw2接收的电压相同于耦合线cl1,亦即最低电压(vss)。p型阱区pw3接收的电压相同于耦合线cl2,亦即抹除电压(vee)。深n型阱区(dnw)接收抹除电压(vee)。其中,抹除电压(vee)大于最低电压(vss),且最低电压(vss)小于等于0v。举例来说,抹除电压(vee)为12v,最低电压(vss)为0v。

93.在抹除动作时,由于耦合线cl1接收最低电压(vss)且耦合线cl2接收抹除电压(vee),所以存储单元阵列600中连接于耦合线cl1的第一列为选定列,连接于耦合线cl2的第二列为非选定列。非选定列中的存储单元c21、c22无法被抹除。

94.再者,在选定列中,抹除线el1、源极线sl1、sl2与位线bl1、bl2接收抹除电压(vee),所以热载流子(例如电子)经由fn隧道(fowler

‑

nordheim tunneling)效应退出存储单元c11、c12中浮动栅晶体管m1、m2的浮动栅极,使得存储单元c11、c12被抹除为第二存储状态。换言之,在抹除动作时,选定列的所有存储单元(亦即选定页的存储单元)会被抹除为第二存储状态。

95.如图7c所示,在读取动作时,耦合线cl1接收第一供应电压(vd1),耦合线cl2接收第一供应电压(vd1),字符线wl1接收第二供应电压(vd2),字符线wl2接收最低电压(vss),源极线sl1接收第一供应电压(vd1),位线bl1接收第二供应电压(vd2),源极线sl2与位线bl2接收第一供应电压(vd1),抹除线el1接收第一供应电压(vd1)。除此之外,p型阱区pw2接收的电压相同于耦合线cl1,亦即第一供应电压(vd1)。p型阱区pw3接收的电压相同于耦合线cl2,亦即第一供应电压(vd1)。深n型阱区(dnw)接收第二供应电压(vd2)。其中,第二供应电压(vd2)大于第一供应电压(vd1),第一供应电压(vd1)大于等于最低电压(vss),且最低电压(vss)小于等于0v。举例来说,第二供应电压(vd2)为5v,第一供应电压(vd1)为1v,最低电压(vss)为0v。

96.在读取动作时,由于耦合线cl1接收第一供应电压(vd1)且字符线wl1接收第二供

应电压(vd2),所以存储单元阵列600中连接于耦合线cl1的第一列为选定列。再者,由于耦合线cl2接收第一供应电压(vd1)且字符线wl2接收最低电压(vss),所以存储单元阵列600中连接于耦合线cl2的第二列为非选定列,且非选定列中的存储单元c21、c22无法被读取。

97.再者,在选定列中,字符线wl1接收第二供应电压(vd2),源极线sl1接收第一供应电压(vd1),位线bl1接收第二供应电压(vd2),所以开关晶体管me与选择晶体管ma开启,存储单元c11会产生一读取电流(read current),由位线bl1流经浮动栅极m1至源极线sl1。再者,读取电流的大小是根据存储单元c11的存储状态来决定,例如第一存储状态的读取电流小于第二存储状态的读取电流。换句话说,在读取动作时,根据存储单元c11所产生的读取电流即可判断存储单元c11的存储状态。

98.另外,由于字符线wl1接收第二供应电压(vd2),源极线sl2与位线bl2接收第一供应电压(vd1),开关晶体管mf与选择晶体管mb关闭,存储单元c12不会产生读取电流(read current)。也就是说,经由适当地偏压,可以控制选定列上的任一存储单元产生读取电流或者不产生读取电流,并判断该存储单元的存储状态。

99.由以上的说明可知,在第三实施例的存储单元阵列600的设计中,不同列存储单元的浮动栅晶体管、开关晶体管与选择晶体管都设计于相同的p型阱区pw1,因此可以大幅减少芯片的尺寸。再者,虽然不同列存储单元的浮动栅晶体管设计在相同的p型阱区pw1,在进行读取动作时,仅有选定列(选定页)存储单元的存储数据可以被读取,非选定列(非选定页)存储单元的数据并不会被读取。

100.根据以上的说明,本发明提出一种多次编程非挥发性存储器的存储单元阵列。存储单元阵列中的存储单元可为单一浮动栅晶体管与单一电容器的1t1c存储单元(1t1c cell);一浮动栅晶体管、一选择晶体管与一电容器的2t1c存储单元(2t1c cell);或者,一浮动栅晶体管、一开关晶体管、一选择晶体管与一电容器的3t1c存储单元(3t1c cell)。另外,在存储单元阵列的设计中,将不同列存储单元的浮动栅晶体管设计在相同的阱区中,用以降低芯片尺寸。再者,设计存储单元阵列的偏压,使得存储单元阵列能够正常地进行编程动作、抹除动作或读取动作。

101.由以上的各种实施例的说明可知,存储单元阵列中的存储单元使用浮动栅晶体管来作为存储元件(storage device)。在其他实施例中,浮动栅晶体管也可以由其他具有电荷存储层(charge storage layer)的存储晶体管(memory transistor)来取代。举例来说,存储晶体管可为具ono栅介电层(ono gate dielectric)的晶体管。其中,ono栅介电层为氧化物层/氮化物层/氧化物层的薄膜,而氮化物层可作为电荷存储层。相同地,在存储单元阵列中,不同列的存储单元中的存储晶体管也会制作在相同的阱区。亦即,不同列的存储单元中的存储晶体管,其体极端会连接至相同的抹除线,其结构与运作关系类似于上述三个实施例,此处不再赘述。

102.再者,在本发明的实施例中是以n型晶体管为例来做说明。当然,本发明并不限定于此,在此领域的技术人员也可以利用p型晶体管与电容器来组成存储单元,且将不同列的p型晶体管设计在相同的n型阱区中。举例来说,根据上述的制造流程,在此领域的技术人员可在p型基板中形成互相隔离的三个n型阱区,并在n型阱区上形成栅极层,接着形成多个p型掺杂区,用以形成存储单元阵列。另外,搭配适当地偏压,即可对存储单元阵列进行编程动作、抹除动作或者读取动作。

103.综上所述,虽然结合以上优选实施例已公开了本发明,然而其并非用以限定本发明。本发明所属技术领域中具有通常知识者,在不脱离本发明的精神和范围内,可作各种的更动与润饰。因此,本发明的保护范围应当以附上的权利要求所界定的为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1