数据排序控制电路以及包括其的存储器件的制作方法

数据排序控制电路以及包括其的存储器件

1.相关申请的交叉引用

2.本技术要求2020年4月24日提交的申请号为10

‑

2020

‑

0050046的韩国专利申请的优先权,其全部内容通过引用合并于此。

技术领域

3.本公开涉及确定读取数据的次序、以确定的次序对数据进行排序(sort)以及输出该数据的存储器件。

背景技术:

4.近来,随着存储系统的操作速度的提高,导致在存储系统中包括的存储器件中需要更高的数据传输速率。为了满足串行输入至存储器件和从存储器件输出的数据的高速率或高带宽传输,存储器件通过预取对数据进行排序。预取是指对串行输入的数据锁存和并行化。为了使数据并行化,使用对时钟进行分频。系统时钟信号被分频成具有不同相位的多相时钟信号,并且利用多相时钟信号对数据进行并行化和串行化。

5.存储器件通过有限数量的引脚或焊盘与外部设备交换数据。输入/输出数据的量逐渐增加。为了提高数据输入/输出速度,在存储器件中设置了各种电路。在规格中限定了用于存储器件的内部操作的各种参数,以确保更稳定的操作。

6.例如,存储器件可以响应于单个读取命令而输出多个数据比特位。可以通过模式寄存器组的突发长度或突发类型来设置要同时输出的数据的比特位数或次序。此外,存储器件可以按照根据与读取命令一起输入的种子地址确定的突发次序而对数据进行排序,并输出该数据。存储器件可以包括用于根据种子地址来控制突发次序的电路。

技术实现要素:

7.根据本公开,提供了一种存储器件,该存储器件可以基于用于确定读取数据的次序的条件来生成排序控制信号,从而减少读取操作的电流消耗。

8.根据本发明的一个实施例,一种数据排序控制电路可以包括:相位检测器,其适用于响应于读取命令来检测第一时钟信号、第二时钟信号、第三时钟信号和第四时钟信号中的每个的相位;次序确定器,其适用于基于种子地址和检测出的每个时钟信号的相位来将数据次序确定为第一次序或第二次序;以及排序控制信号生成器,其适用于基于所述第一时钟信号至所述第四时钟信号来将所述读取命令移位,以生成第一排序控制信号、第二排序控制信号、第三排序控制信号和第四排序控制信号,并且根据所述第一次序或所述第二次序来输出所述第一排序控制信号至所述第四排序控制信号。

9.根据本发明的另一个实施例,一种存储器件可以包括:存储单元阵列,其包括多个存储单元;数据排序控制电路,其适用于基于读取命令、时钟信号和种子地址来确定数据次序,并且根据所确定的数据次序来生成选择控制信号和多个排序控制信号;以及数据排序电路,其适用于响应于所述选择控制信号和所述多个排序控制信号而对从所述存储单元阵

列读取的多个数据进行排序,以输出串行数据。

10.根据本发明的另一个实施例,一种存储器件可以包括:存储单元阵列;数据排序控制电路,其适用于检测在时钟信号的哪个边沿输入了读取命令,基于种子地址和检测出的边沿的组合来确定数据次序,以及基于所述数据次序来生成排序控制信号和选择控制信号;以及数据排序电路,其适用于从所述存储单元阵列并行地接收多个数据项,基于所述排序控制信号和所述选择控制信号来对所述多个数据项进行排序,以及串行地输出经排序的数据项。

附图说明

11.图1是示出根据本公开的一个实施例的存储器件的框图;

12.图2是示出诸如图1中所示的数据排序控制电路的框图;

13.图3是示出诸如图2中所示的次序确定部件的电路图;

14.图4是示出诸如图1中所示的数据排序组件的电路图;以及

15.图5是示出根据本公开的实施例的存储器件的操作的信号波形图。

具体实施方式

16.下面参照所附的附图来详细地描述本公开的实施例,以使本领域技术人员能够容易地实践本发明。然而,如本领域技术人员将从本公开中理解的,可以以各种其它方式来配置、布置和/或实施本发明。因此,本发明不限于本文中所公开的实施例。实施例仅是示例。本发明仅由所附权利要求来限定。此外,下面的描述主要集中于实施例的特征和方面,省略了不必要的描述以阐明本公开的主题。在整个说明书中,对“一个实施例”、“另一实施例”等的引用不一定仅是一个实施例,并且对任何这样的短语的不同引用不一定是同一实施例。当在本文中使用时,术语“实施例”未必指所有实施例。

17.图1是示出根据本公开的实施例的存储器件100的框图。举例来说,图1示出了用于对存储器件100中的读取数据进行排序的配置。存储器件100可以包括:存储单元阵列110、数据输入和输出(输入/输出)控制电路120、数据排序控制电路130和数据排序电路140。

18.存储单元阵列110可以包括多个存储单元。在读取操作期间,可以从存储单元阵列110的多个存储单元并行地读取数据。读取数据可以经由全局输入/输出线发送至数据排序电路140。举例来说,可以在每个操作周期将第一数据至第八数据(gio<0:7>)发送至数据排序电路140。被发送的数据项的数量不限于八个。可以发送任何适当数量的数据项。

19.数据输入/输出控制电路120可以基于时钟信号clk、读取命令rd和读取等待时间latency来生成输入控制信号pin/输出控制信号pout。当读取命令rd被输入至存储器件100时,可以根据读取操作来生成输出使能信号以控制数据路径上的电路。与读取命令rd相对应的信号可以被延迟与读取等待时间latency一样长的时间,并且被延迟的信号可以被移位,从而可以生成与几个定时(timing)相对应的多个输出使能信号。

20.数据输入/输出控制电路120可以基于读取命令rd和读取等待时间latency来生成与多个输出使能信号中的任意一个相对应的输入控制信号pin和输出控制信号pout。输入控制信号pin和输出控制信号pout可以各自与时钟信号clk同步地生成,并且可以用于控制包括在数据排序电路140中的管道锁存器的输入和输出。

21.数据排序控制电路130可以基于时钟信号clk、读取命令rd和种子地址(a<0:2>)来确定数据次序。此外,数据排序控制电路130可以根据确定的次序来生成选择控制信号sel和第一排序控制信号至第八排序控制信号(order<0:7>)。换言之,数据排序控制电路130可以根据种子地址(a<0:2>)来确定从存储单元阵列110读取的第一数据至第八数据(gio<0:7>)的突发次序。种子地址(a<0:2>)对应于在读取操作期间与读取命令rd一起施加到存储器件100的列地址。下面参照表1更详细地描述种子地址(a<0:2>)。

22.数据排序电路140可以包括:数据锁存器142、数据排序组件144和数据输出组件146。数据排序电路140可以响应于控制信号(pin、pout、sel和order<0:7>)而对第一数据至第八数据(gio<0:7>)进行排序,并输出最终数据data。

23.数据锁存器142可以响应于输入控制信号pin而储存第一数据至第八数据(gio<0:7>)。数据锁存器142可以锁存第一数据至第八数据(gio<0:7>),并将被锁存的数据作为第一锁存数据ld0至第八锁存数据ld7输出。

24.数据排序组件144可以响应于选择控制信号sel和第一排序控制信号至第八排序控制信号(order<0:7>)来对第一锁存数据ld0至第八锁存数据ld7进行排序,并输出经排序的数据作为串行数据do。数据排序组件144可以响应于选择控制信号sel而选择第一锁存数据ld0至第八锁存数据ld7,根据由数据排序控制电路130确定的数据次序(即,第一排序控制信号至第八排序控制信号(order<0:7>))来对选中的数据进行排序,并输出串行数据do。在下面更详细地描述数据排序组件144。

25.数据输出组件146可以使串行数据do与输出控制信号pout同步,并输出最终数据data。当读取命令rd被输入至存储器件100时,数据输出组件146可以将应用读取等待时间的最终数据data输出至存储器件100的外部。

26.种子地址(a<0:2>)可以包括在读取操作期间与读取命令rd一起应用于存储器件100的列地址的多个比特位之中的三个最低有效位。存储器件100可以按照根据种子地址(a<0:2>)确定的突发次序来输出数据。参见表1,可以根据种子地址(a<0:2>)来识别从存储器件100输出的数据的突发次序。

27.[表1]

[0028][0029]

在这种情况下,经由全局输入/输出线从存储单元阵列110读取的数据(gio<0:7>)可以分别对应于根据突发次序的数据(bl<0:7>)。换言之,当种子地址(a<0:2>)是(0,0,0)时,经由全局输入/输出线从存储单元阵列110读取的数据(gio<0:7>)可以被顺序地从存储器件100输出到例如另一个器件。每当种子地址(a<0:2>)改变时,读取数据(gio<0:7>)可以基于种子地址而以不同的次序从存储器件100输出。表1的条件可以基于存储器件100的规格来预先确定。

[0030]

随着操作速度的增大,存储器件100可以基于通过对系统时钟信号进行分频而生成的多相时钟信号来输出数据。例如,存储器件100可以使用4相时钟信号,其中相邻的时钟信号具有90度的相位差。在这种情况下,当输入读取命令rd时,可以根据时钟信号的相位来改变通过时钟信号对读取数据进行排序的次序(gio<0:7>)。因此,如果存储器件100根据时钟信号的相位和种子地址(a<0:2>)而使读取数据(gio<0:7>)的突发次序的变化最小化,则可以在存储器件100的读取操作中减少电流消耗并增加定时增益。

[0031]

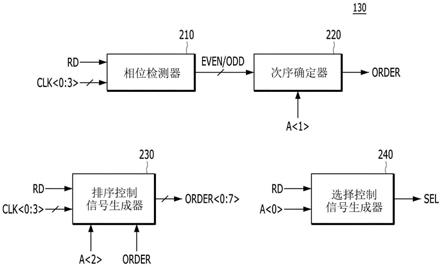

图2是示出如图1中所示的数据排序控制电路130的框图。数据排序控制电路130可以包括:相位检测器210、次序确定器220、排序控制信号生成器230和选择控制信号生成器240。

[0032]

根据一个实施例,第一时钟信号至第四时钟信号(clk<0:3>)可以被用作图1的时钟信号clk。第一时钟信号至第四时钟信号(clk<0:3>)可以包括分频信号,其中相邻的信号具有90度相位差,该分频信号是通过对输入至存储器件100的系统时钟信号进行分频来获得。

[0033]

相位检测器210可以响应于读取命令rd而检测第一时钟信号至第四时钟信号(clk<0:3>)的相位。相位检测器210可以在输入读取命令rd的时刻处检测第一时钟信号和第三时钟信号(clk<0>和clk<2>)的相位,从而可以生成偶数信号even和奇数信号odd。

[0034]

相位检测器210可以基于读取命令rd来检测时钟信号的正向相位(forward phase)或反向相位(reverse phase)。当与第一时钟信号clk<0>同步地(即,clk<0>的上升

沿)输入读取命令rd时,相位检测器210可以将其检测为具有正向相位并激活偶数信号even。相反地,当与第三时钟信号clk<2>同步地输入读取命令rd时(即,clk<2>的上升沿或clk<0>的下降沿),相位检测器210可以将其检测为具有反向相位并激活奇数信号odd。根据本公开的实施例,用于激活偶数信号even和奇数信号odd的条件可以颠倒或改变。

[0035]

次序确定器220可以基于种子地址(a<0:2>)的第二地址(a<1>)和由相位检测器210检测出的相位来确定数据次序。次序确定器220可以确定要按照第一次序或第二次序来对数据进行排序,并且可以相应地激活或去激活次序控制信号order。下面参照图3更详细地描述次序确定器220的配置和操作。

[0036]

排序控制信号生成器230可以通过基于第一时钟信号至第四时钟信号(clk<0:3>)而移位读取命令rd来生成第一排序控制信号至第八排序控制信号(order<0:7>)。排序控制信号生成器230可以按照根据种子地址(a<0:2>)的第三地址(a<2>)和排序控制信号order的次序输出第一排序控制信号至第八排序控制信号(order<0:7>)。排序控制信号生成器230可以包括多个移位器(未示出)。

[0037]

排序控制信号生成器230可以通过将从读取命令rd生成的输出使能信号移位与第一时钟信号至第四时钟信号(clk<0:3>)之中的相邻的时钟信号之间的相位差一样大的相位来生成第一排序控制信号至第四排序控制信号(order<0:3>)。同样,排序控制信号生成器230可以通过将输出使能信号移位与第一时钟信号至第四时钟信号(clk<0:3>)之中的相邻的时钟信号的相位差一样大的相位来生成第五排序控制信号至第八排序控制信号(order<4:7>)。第一排序控制信号至第四排序控制信号(order<0:3>)和第五排序控制信号至第八排序控制信号(order<4:7>)可以对应于第一至第四数据(gio<0:3>)和第五数据至第八个数据(gio<4:7>)。

[0038]

在这种情况下,排序控制信号生成器230可以根据由次序确定器220确定的第一次序或第二次序来输出第一排序信号至第四排序控制信号(order<0:3>)和第五排序控制信号至第八排序控制信号(order<4:7>)。例如,当次序确定器220确定数据次序是第一次序并且激活次序控制信号order时,排序控制信号生成器230可以按升序(即,按照第一排序控制信号(order<0>)、第二排序控制信号(order<1>)、第三排序控制信号(order<2>)和第四排序控制信号(order<3>)的次序)输出第一排序控制信号至第四排序控制信号(order<0:3>)。同样地,排序控制信号生成器230可以按升序(即,按照第五排序控制信号(order<4>、第六排序控制信号(order<5>)、第七排序控制信号(order<6>)和第八排序控制信号(order<7>)的次序)输出第五排序控制信号至第八排序控制信号(order<4:7>)。

[0039]

当次序确定器220确定数据次序是第二次序并去激活次序控制信号order时,排序控制信号生成器230可以按照第三排序控制信号(order<2>)、第四排序控制信号(order<3>)、第一排序控制信号(order<0>)和第二排序控制信号(order<1>)的次序输出第一排序控制信号至第四排序控制信号(order<0:3>)。同样地,排序控制信号生成器230可以按照第七排序控制信号(order<6>)、第八排序控制信号(order<7)、第五排序控制信号(order<4>)和第六排序控制信号(order<5>)的次序输出第五排序控制信号至第八排序控制信号(order<4:7>)。

[0040]

此外,排序控制信号生成器230可以根据种子地址(a<0:2>)的第三个地址(a<2>)来确定第一排序控制信号至第四排序控制信号(order<0:3>)和第五排序控制信号至第八

排序控制信号(order<4:7>)(其为第一输出)的次序。当种子地址(a<0:2>)的第三地址(a<2>)处于逻辑低电平(“0”)时,排序控制信号生成器230可以输出第一排序控制信号至第四排序控制信号(order<0:3>),然后输出第五排序控制信号至第八排序控制信号(order<4:7>)。当种子地址(a<0:2>)的第三地址(a<2>)处于逻辑高电平(“1”)时,排序控制信号生成器230可以输出第五排序控制信号至第八排序控制信号(order<4:7>),然后输出第一排序控制信号至第四排序控制信号(order<0:3>)。

[0041]

选择控制信号生成器240可以基于种子地址(a<0:2>)的第一地址(a<0>)来生成选择控制信号sel。当读取命令rd被输入时,选择控制信号生成器240可以锁存种子地址(a<0:2>)的第一地址(a<0>)并且激活或去激活选择控制信号sel。

[0042]

图3是示出如图2中所示的次序确定器220的电路图。次序确定器220可以包括第一与非门nand1、第二与非门nand2和异或非(xnor)门xnor。

[0043]

第一与非门nand1可以接收偶数信号even、复位信号rstb和第二与非门nand2的输出信号,并对接收到的信号执行与非运算。在这种情况下,复位信号rstb可以包括在由次序确定器220进行的复位操作期间被激活为逻辑低电平(“0”)的信号。

[0044]

第二与非门nand2可以接收第一与非门nand1的输出信号和奇数信号odd,并对接收到的信号执行与非运算。异或非门xnor可以接收第一与非门nand1的输出信号和种子地址(a<0:2>)的第二地址(a<1>),对接收到的信号执行异或非操作,并输出次序控制信号order。

[0045]

当检测出以相对于时钟信号的正向相位输入读取命令rd时,例如,当与第一时钟信号clk<0>的上升沿同步地输入读取命令rd时,相位检测器210可以激活偶数信号even并去激活奇数信号odd。因此,第二与非门nand2可以输出处于逻辑高电平(“1”)的输出信号,并且第一与非门nand1可以输出处于逻辑低电平(“0”)的输出信号。

[0046]

当种子地址(a<0:2>)的第二地址(a<1>)处于逻辑低电平(“0”)时,异或非门xnor可以激活次序控制信号order,并且次序确定器220可以确定出数据次序是第一次序。当种子地址(a<1:2>)的第二地址(a<1>)处于逻辑高电平(“1”)时,异或非门xnor可以去激活次序控制信号order,并且次序确定器220可以确定数据次序是第二次序。

[0047]

相反地,当检测出以时钟信号的反向相位输入读取命令rd时,例如,当在第一时钟信号clk<0>的下降沿或第三时钟信号clk<2>的上升沿输入读取命令rd时,相位检测器210可以去激活偶数信号even,而激活奇数信号odd。因此,第一与非门nand1可以输出处于逻辑高电平(“1”)的输出信号,并且第二与非门nand2可以输出处于逻辑低电平(“0”)的输出信号。

[0048]

当种子地址(a<0:2>)的第二地址(a<1>)处于逻辑低电平(“0”)时,异或非门xnor可以去激活次序控制信号order,并且次序确定器220可以确定数据次序是第二次序。当种子地址(a<1:2>)的第二地址(a<1>)处于逻辑高电平(“1”)时,异或非门xnor可以激活次序控制信号order,并且次序确定器220可以确定数据次序是第一次序。

[0049]

图4是示出如图1中所示的数据排序组件144的电路图。数据排序组件144可以包括数据选择器410和数据发送器420。

[0050]

数据选择器410可以响应于选择控制信号sel来选择第一锁存数据ld0至第八锁存数据ld7,并将被选择的锁存数据作为第一选择数据sd0至第八选择数据sd7输出。数据选择

器410可以包括第一选择组件mux1至第八选择组件mux8。

[0051]

第一选择组件mux1至第四选择组件mux4中的每一个可以接收第一锁存数据ld0至第四锁存数据ld3之中的两个数据项。第一选择组件mux1至第四选择组件mux4中的每一个可以选择响应于选择控制信号sel而输入的两个数据项中的一个,并将选中的数据项作为选择数据(即,分别用于mux1至mux4的第一选择数据sd0至第四选择数据sd3)输出。

[0052]

类似地,第五选择组件mux5至第八选择组件mux8中的每一个可以接收第五锁存数据ld4至第八锁存数据ld7之中的两个数据项。第五选择组件mux5至第八选择组件mux8中的每一个可以选择响应于选择控制信号sel而输入的两个数据项中的一个,并将选中的数据项作为选择数据(即,分别用于mux5至mux8的第五选择数据sd4至第八选择数据sd7)输出。

[0053]

参考表1,可以识别出随着种子地址(a<0:2>)的第一地址(a<0>)从逻辑低电平(“0”)切换到逻辑高电平(“1”),将对第一数据至第四数据(bl<0:3>)和第五数据至第八数据(bl<4:7>)的次序做出改变。第一数据至第八数据(bl<0:7>)可以分别对应于第一锁存数据ld0至第八锁存数据ld7。

[0054]

换言之,当种子地址(a<0:2>)的第一地址(a<0>)处于逻辑低电平(“0”)时,选择控制信号sel可以被去激活。第一选择组件mux1至第八选择组件mux8可以分别选择第一锁存数据ld0至第八锁存数据ld7,并且输出选中的数据作为第一选择数据sd0至第八选择数据sd7。相反地,随着种子地址(a<0:2>)的第一地址(a<0>)从逻辑低电平(“0”)切换到逻辑高电平(“1”),选择控制信号sel可以被激活。当选择控制信号sel被激活时,第一选择组件mux1至第四选择组件mux4可以将第二锁存数据ld1、第三锁存数据ld2、第四锁存数据ld3和第一锁存数据ld0分别作为第一选择数据sd0至第四选择数据sd3输出。第五选择组件mux5至第八选择组件mux8可以将第六锁存数据ld5、第七锁存数据ld6、第八锁存数据ld7和第五锁存数据ld4分别作为第五选择数据sd4至第八选择数据sd7输出。

[0055]

数据发送器420可以响应于第一排序控制信号至第八排序控制信号(order<0:7>)而对第一选择数据sd0至第八选择数据sd7进行排序,并将它们输出为串行数据do。数据发送器420可以包括第一传输组件421至第八传输组件428。

[0056]

第一传输组件421至第八传输组件428中的每一个分别可以包括反相器inv和三相反相器3

‑

iv。当在第一排序控制信号至第八排序控制信号(order<0:7>)之中的相应的排序控制信号被激活时,第一传输组件421至第八传输组件428可以将它们的在第一选择数据sd0至第八选择数据sd7之中的相应数据作为串行数据do输出。

[0057]

换言之,第一排序控制信号至第八排序控制信号(order<0:7>)可以分别对应于第一选择数据sd0至第八选择数据sd7。数据发送器420可以输出第一选择数据sd至第八选择数据sd7作为串行数据do,其对应于输入第一排序控制信号至第八排序控制信号(order<0:7>)的次序。

[0058]

图5是示出根据本公开的实施例的存储器件100的操作的信号波形图。

[0059]

通过示例,图5示出了读取命令rd以反向相位被输入,并且种子地址(a<0:2>)的第二地址(a<1>)处于逻辑高电平。参考图5,由于其他地址(a<0>和a<2>)具有逻辑低电平,因此可以不考虑由此导致的突发次序的变化。

[0060]

随着与第三时钟信号(clk<2>)同步地输入读取命令rd,相位检测器210可以检测反向相位,并且激活奇数信号odd,同时去激活偶数信号even。此时,由于种子地址(a<0:2>)

的第二地址(a<1>)处于逻辑高电平,因此次序确定器220可以激活次序控制信号order。

[0061]

如上所述,由于种子地址(a<0:2>)的第一地址(a<0>)具有逻辑低电平,因此选择控制信号生成器240可以去激活选择控制信号sel。数据选择器410可以分别输出第一锁存数据ld0至第八锁存数据ld7(即,第一数据至第八数据(gio<0:7>))作为第一选择数据sd0至第八选择数据sd7。

[0062]

由于种子地址(a<0:2>)的第三地址(a<2>)具有逻辑低电平,因此排序控制信号生成器230可以输出第一排序控制信号至第四排序控制信号(order<0:3>),然后输出第四排序控制信号至第八排序控制信号(order<4:7>)。由于次序控制信号order已经被激活,因此排序控制信号生成器230可以顺序地生成第一排序控制信号至第八排序控制信号(order<0:7>),如图5所示。数据发送器420可以响应于顺序地输入的第一排序控制信号至第八排序控制信号(order<0:7>)来对第一选择数据sd0至第八选择数据sd7进行顺序地排序,并且数据发送器420可以将它们作为串行数据do输出。

[0063]

结果,当基于多相时钟信号来对数据进行排序时,根据检测出的相位来改变数据次序的方案与根据种子地址(a<0:2>)的第二地址(a<1>)来确定数据的突发次序的方案相同。因此,通过反映种子地址(a<0:2>)的次序来确定突发次序并根据检测出的相位对数据进行排序,可能会花费很长时间并且导致不必要的重复操作。

[0064]

根据本公开的实施例,可以基于第二地址(a<1>)的逻辑电平和检测出的多相时钟信号的相位的组合,同时生成用于对数据进行排序的信号。在图5的图示示例中,尽管已经检测到反向相位,但是因为第二地址(a<1>)具有逻辑高电平,所以可以按次序输出读取数据(gio<0:7>)。在这种情况下,可以通过省略与条件相对应的重复步骤并组合条件来同时生成第一排序控制信号至第八排序控制信号(order<0:7>)。

[0065]

在基于多相时钟信号来读取数据和排序数据时,存储器件可以根据种子地址而将数据突发次序的变化最小化。通过根据多相时钟信号的相位和种子地址来组合几种条件,可以立即生成用于对数据进行排序的排序控制信号。这允许跳过与条件相对应的重复步骤,从而增大了定时增益并减少了在存储器件的读取操作中的电流消耗。

[0066]

尽管已经参照特定实施例描述了本发明,但这仅出于描述的目的,并非旨在限制本发明。对于本领域技术人员将显而易见的是,在不脱离本发明的精神和范围的情况下,可以进行各种改变和修改。因此,本发明包括落入权利要求及其等同方案内的所有变型。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1