具有多个读取位线的位单元的制作方法

具有多个读取位线的位单元

背景技术:

1.本节旨在提供与理解本文所述的各种技术相关的信息。如本节的标题所暗示的,这是对相关技术的讨论,绝不应当暗示其是现有技术。一般来讲,相关技术可被认为是或可不被认为是现有技术。因此,应当理解,本节中的任何陈述均应按此意义来理解,并且不作为对现有技术的任何认可。

2.在常规计算架构中,一些乘法器通常被设计来处理应用程序需要处理的大量计算,这可能在处理交叉模式计算(诸如矩阵)中的大量数字时引起复杂乘法器处理的大延迟。这些复杂的乘法器计算用于机器学习应用程序,并且一些类型的常规乘法器设计通常实现被构建来处理大量数字的多比特逻辑。另外,一些其他乘法器设计也可使用被构建来处理大量数字的各种其他多比特符号逻辑。然而,由于复杂且低效的存储器设计,这些类型的复杂乘法器通常表现出故障和延迟问题。因此,需要改进一些乘法器电路的物理设计具体实施,以便提供更有效的二进制乘法运算。

附图说明

3.本文参考附图描述了各种技术的具体实施。然而,应当理解,附图仅示出了本文所述的各种具体实施,并且不旨在限制本文所述的各种技术的实施方案。

4.图1示出了根据本文所述的各种具体实施的与位单元相关联的存储器电路的图。

5.图2示出了根据本文所述的各种具体实施的位单元结构的图。

6.图3示出了根据本文所述的具体实施的具有布置成1

×

8阵列的位单元的存储器阵列电路的图。

7.图4示出了根据本文所述的具体实施的具有布置成16

×

8阵列的位单元的存储器阵列电路的图。

8.图5示出了根据本文所述的具体实施的具有布置成32

×

16阵列的位单元的存储器阵列电路的图。

9.图6示出了根据本文所述的具体实施的具有布置成多个32

×

16阵列块的位单元的存储器阵列电路的图。

10.图7示出了根据本文所述的具体实施的具有布置成多个128

×

16阵列组的位单元的存储器阵列电路的图。

11.图8示出了根据本文所述的具体实施的具有布置成交织的64

×

16阵列块的位单元的存储器阵列电路的图。

12.图9示出了根据本文所述的具体实施的具有布置成交织的32

×

16阵列块的位单元的存储器阵列电路的图。

13.图10a至图10b示出了根据本文所述的具体实施的具有呈多个128

×

16 阵列组的位单元的存储器阵列电路的图。

具体实施方式

14.本文所述的各种具体实施是指具有带有多个读取位线的位单元电路的存储器架构。例如,本文所述的各种方案和技术可提供可用作核心内矩阵加速器的定制存储器的超快高密度存储器架构。本文所述的各种方案和技术的一些方面提供十六(16)个条目,每个条目具有64字节,并且每个周期具有一(1)个读取或一(1)个写入。另外,本文所述的各种方案和技术可提供可被配置成在单个周期中更新条目的所有64字节的写入操作。另外,本文所述的各种方案和技术还可为读取操作提供多种模式,诸如例如单条目读取和块读取。例如,单条目读取可指在单个周期中读取条目的所有64个字节(即,读取512位),并且块读取可指在单个周期中为所有16 个条目读取相同的4个字节(即,读取512位)。

15.在一些具体实施中,本文所述的各种方案和技术可提供写入操作,该写入操作例如通过经由激活单个写入字线(wwl)将数据写入四(4)个 128

×

16位单元组来在单个周期中更新条目的所有64个字节,其中该技术用于在单个周期中写入512位。另外,在一些具体实施中,本文所述的各种方案和技术可提供条目读取操作,该条目读取操作例如通过经由激活单个读取字线(rwl)从四(4)个128

×

16位单元组读取数据来在单个周期中读取条目的所有64个字节,其中该技术用于在单个周期中读取512位。此外,在一些具体实施中,本文所述的各种方案和技术可提供块读取操作,该块读取操作例如通过在单个周期中从512位块读取数据来在单个周期中块读取32

×

16位单元阵列。

16.本文将参考图1至图9和图10a至图10b更详细地描述高密度存储器架构的各种具体实施。

17.图1示出了根据本文所述的各种具体实施的与位单元相关联的存储器电路102的图100。

18.在各种具体实施中,存储器电路102可被实现为具有各种集成电路 (ic)部件的系统或设备,这些ic部件被布置和耦接在一起作为提供物理电路设计和相关结构的部分的组装或组合。在一些情况下,一种将存储器电路102设计、提供和构建为集成系统或设备的方法可涉及使用本文所述的各种ic电路部件,以便实现与其相关联的各种存储器阵列架构。存储器电路102可与单个芯片上的计算电路和相关部件集成,并且存储器电路102 可在用于电子、移动和物联网(iot)应用(包括传感器节点)的嵌入式系统中实现。

19.如图1所示,存储器电路102可与被实现为位单元或存储器单元的存储器架构相关联。在一些情况下,位单元104可指具有单个位单元的设备或结构,该单个位单元被配置成存储可经由多个字线和多个位线访问的数据位。位单元104可利用耦接到位单元的多个字线,包括写入字线 (wwl)、读取字线(rwl)和全局读取字线(grwl)。位单元104可利用耦接到位单元的多个水平位线(wbl,nwbl,rbl_h0,rbl_h1, rbl_h2,rbl_h3)。位单元104可利用耦接到位单元的多个竖直位线 (rbl_v0,rbl_v1,rbl_v2,rbl_v3,rbl_v4,rbl_v5,rbl_v6, rbl_v7,rbl_v8)。本文更详细地描述了与存储器电路102的与位单元 104相关联的存储器阵列架构的各种布局设计相关联的各个方面和结构特征,以及与其相关的各种方案和技术。

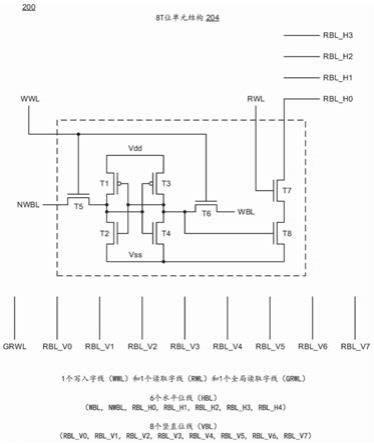

20.图2示出了根据本文所述的各种具体实施的位单元结构204的图200。在一些具体实施中,图2的位单元结构204与图1的位单元104相关联。

21.在各种具体实施中,位单元结构204可被实现为具有各种ic部件的存储器设备,这

些ic部件被布置和耦接在一起作为允许物理布局设计和相关结构的部分的组装或组合。在一些情况下,一种将位单元结构204设计、提供和制造为集成设备的方法可涉及使用本文所述的各种ic电路部件,以便实现与其相关联的各种存储器阵列架构。位单元结构204可与单个芯片上的计算电路和相关部件集成,并且另外,位单元结构204可在用于电子、移动和物联网(iot)应用的嵌入式系统中使用。

22.如图2所示,位单元结构204可指具有单个位单元的设备,该单个位单元具有多个晶体管,该多个晶体管被布置和配置成存储可经由多个字线和多个位线访问的数据位。在一些具体实施中,位单元结构204可包括八个晶体管,该八个晶体管被布置和配置成提供单个8晶体管(8t)位单元。例如,位单元结构204可包括布置为第一反相器的晶体管(t1,t2)、布置为第二反相器的晶体管(t3,t4)、写入访问晶体管(t5,t6)和读取晶体管(t7,t8)。另外,位单元结构204可包括多个字线,包括写入字线 (wwl)、读取字线(rwl)和全局读取字线(grwl)。写入字线 (wwl)可耦接到晶体管(t5,t6)的栅极,并且读取字线(rwl)可耦接到晶体管(t7)的栅极。另外,第一写入位线(wbl)可耦接到晶体管 (t6),并且第二写入位线(nwbl)可耦接到晶体管(t5)。

23.在一些具体实施中,位单元结构204可具有耦接到位单元的多个水平位线(wbl,nwbl,rbl_h0,rbl_h1,rbl_h2,rbl_h3)。多个水平位线可包括相对于位单元沿水平方向设置的第一读取位线(rbl_h0, rbl_h1,rbl_h2,rbl_h3),并且多个水平位线还可包括第一写入位线 (wbl)和作为第一写入位线(wbl)的补充的第二写入位线 (nwbl)。因此,水平位线可包括相对于位单元沿水平方向设置的六个水平位线,该六个水平位线包括四(4)个水平读取位线(rbl_h0, rbl_h1,rbl_h2,rbl_h3)以及两个水平写入位线(wbl,nwbl)。

24.在一些具体实施中,位单元结构204可具有耦接到位单元的多个竖直位线(rbl_v0,rbl_v1,rbl_v2,rbl_v3,rbl_v4,rbl_v5,rbl_v6, rbl_v7,rbl_v8)。多个竖直位线可指相对于位单元沿竖直方向设置的多个第二读取位线(rbl),并且另外,第二读取位线可包括相对于位单元沿竖直方向设置的八(8)个竖直读取位线。

25.图3示出了根据本文所述的具体实施的具有布置成1

×

8阵列的位单元 204的存储器阵列电路302的图300。

26.如图3所示,存储器阵列电路302可包括位单元204的1

×

8阵列,这些位单元被布置成单行8个位单元204。位单元204的1

×

8阵列可布置成单行位单元204,并且可包括第一位单元bc[0]、第二位单元bc[1]、第三位单元bc[2]、第四位单元bc[3]、第五位单元bc[4]、第六位单元bc[5]、第七位单元bc[6]和第八位单元bc[7],这些位单元耦接到对应的写入字线 (wwl)和读取字线(rwl)。在一些情况下,第一写入字线wwl[0]和第一读取字线rwl[0]可耦接到第一位单元bc[0],第二写入字线wwl[1] 和第二读取字线rwl[1]可耦接到第二位单元bc[1],依此类推,直到第八写入字线wwl[7]和第八读取字线rwl[8]耦接到第八位单元bc[7]。另外,在一些情况下,每个位单元204可具有八个晶体管,该八个晶体管被布置和配置成在8个位单元204的行中提供8晶体管(8t) 位单元。

[0027]

在一些具体实施中,水平位线(rbl_h0,rbl_h1,rbl_h2, rbl_h3)可耦接到1

×

8阵列中的位单元204,并且水平位线(rbl_h0, rbl_h1,rbl_h2,rbl_h3)可包括相对于位单元阵列沿水平方向设置的第一读取位线。第一读取位线(rbl_h0,rbl_h1,rbl_h2,rbl_h3)包括相对于位单元204沿水平方向设置的四(4)个水平读取位线。在一些情况下,第一读取位

线(rbl_h0)可耦接到第四位单元bc[3]和第八位单元 bc[7],并且第二读取位线(rbl_h1)可耦接到第三位单元bc[2]和第七位单元bc[6]。另外,第三读取位线(rbl_h2)可耦接到第二位单元 bc[1]和第六位单元bc[5],并且第四读取位线(rbl_h3)可耦接到第一位单元bc[0]和第五位单元bc[4]。

[0028]

在一些具体实施中,水平位线还可包括第一写入位线(wbl)以及作为第一写入位线(wbl)的补充的第二写入位线(nwbl)。如图3所示,写入位线(wbl,nwbl)耦接到1

×

8位单元阵列中的位单元204中的每个位单元。因此,如图所示,位单元204的1

×

8阵列可包括被布置成单行八(8)列的八(8)个位单元,并且可在单个周期中,诸如例如在读取操作期间的读取周期(“读取”)中读取1

×

8阵列中的至少四(4)个位单元204。另外,在一些情况下,1

×

8位单元阵列可被配置成允许在单个周期中,诸如例如在读取操作期间的读取周期(“读取”)中激活和读取至少四(4)个字线。

[0029]

另外,在一些具体实施中,参考图2公开的多个竖直位线(rbl_v0, rbl_v1,rbl_v2,rbl_v3,rbl_v4,rbl_v5,rbl_v6,rbl_v7, rbl_v8)可耦接到图3的1

×

8阵列中的位单元204,并且竖直位线可指相对于位单元294的1

×

8阵列沿竖直方向设置的第二读取位线。此外,在一些情况下,第二读取位线可包括相对于1

×

8阵列中的位单元204沿竖直方向设置的八(8)个竖直读取位线(rbl_v0,rbl_v1,rbl_v2,rbl_v3, rbl_v4,rbl_v5,rbl_v6,rbl_v7,rbl_v8)。

[0030]

此外,在一些具体实施中,如图3所示的位单元204的1

×

8阵列可被修改为在较大阵列中包括位单元204的附加行。例如,1

×

8阵列可被修改为例如通过将1

×

8位单元阵列扩展为包括8行位单元204而包括1

×

8位单元阵列的8个副本,从而提供位单元204的8

×

8阵列。在这种情况下,图3 所示的存储器电路302可被适配成提供位单元204的8

×

8阵列,该阵列可包括被布置成八(8)行与八(8)列的六十四(64)个位单元,并且另外,可在单个周期中,诸如例如在读取操作期间的读取周期(“读取”) 中读取8

×

8阵列中的位单元204的三十二(32)个位单元。另外,在一些情况下,8

×

8位单元阵列可被配置成允许在单个周期中,诸如例如在读取操作期间的读取周期(“读取”)中激活和读取至少四(4)个字线。

[0031]

图4示出了根据本文所述的具体实施的具有布置成16

×

8阵列的位单元 204的存储器阵列电路402的图400。

[0032]

如图4所示,存储器阵列电路402可包括位单元204的多个8

×

8阵列,该多个阵列布置成8

×

8位单元阵列412a、412b的多个块或组。存储器阵列电路402还可包括耦接到多个8

×

8位单元阵列412a、412b的多个逻辑阵列418a、418b,其中多个逻辑阵列418a、418b被配置成访问存储在多个8

×

8位单元阵列412a、412b的位单元204中的数据。例如,第一逻辑阵列418a可经由多个逻辑门(lg0a,lg1a,...,lg7a)耦接到第一8

×

8 位单元阵列412a,并且存储在第一8

×

8位单元阵列412a的位单元204中的数据可利用多个读取字线(rwl[0],rwl[1],...,rwl[7])和多个全局读取字线(gwrl[0],grwl[1],...,gwrl[7])进行访问。

[0033]

在一些情况下,参考第一逻辑阵列418a,可经由全局读取字线 (gwrl[0],grwl[1],grwl[2],gwrl[3])将第一写入字线信号 (wla_en[0])与全局读取使能信号一起提供给第一逻辑门(lg0a, lg1a,lg2a,lg3a),以用于选择第一8

×

8位单元阵列412a中的一个或多个对应的读取字线(rwl[0],rwl[1],rwl[2],rwl[3])。另外,可经由全局读取字线(gwrl[4],grwl[5],grwl[6],gwrl[7])将第二写入字线信号(wlb_en[0])与全局读取使能信号一

起提供给第二逻辑门 (lg4a,lg5a,lg6a,lg7a),以用于选择第一8

×

8位单元阵列412a中的一个或多个对应的读取字线(rwl[4],rwl[5],rwl[6],rwl[7])。另外,在一些情况下,第一逻辑阵列418a可耦接到8

×

8位单元阵列412a的第一块中的六十四(64)个位单元以访问存储在第一块中的数据。

[0034]

在一些情况下,参考第二逻辑阵列418b,可经由全局读取字线 (gwrl[0],grwl[1],grwl[2],gwrl[3])将第一写入字线信号 (wla_en[1])与全局读取使能信号一起提供给第二逻辑门(lg0b,lg1b, lg2b,lg3b),以用于选择第二8

×

8位单元阵列412b中的一个或多个对应的读取字线(rwl[0],rwl[1],rwl[2],rwl[3])。另外,可经由全局读取字线(gwrl[4],grwl[5],grwl[6],gwrl[7])将第二写入字线信号(wlb_en[1])与全局读取使能信号一起提供给第二逻辑门(lg4b, lg5b,lg6b,lg7b),以用于选择第二8

×

8位单元阵列412b中的一个或多个对应的读取字线(rwl[4],rwl[5],rwl[6],rwl[7])。此外,第二逻辑阵列418b可耦接到8

×

8位单元阵列412b的第二块中的六十四(64) 个位单元以访问存储在第二块中的数据。

[0035]

此外,在一些具体实施中,如图3所示的1

×

8位单元阵列可被扩展或修改为包括多个8

×

8阵列412a、412b。例如,1

×

8阵列可被修改为每个 8

×

8位单元阵列412a、412b包括1

×

8位单元阵列的8个副本,从而提供位单元204的多个8

×

8阵列。在这种情况下,图4所示的存储器电路402可被适配成提供位单元204的16

×

8存储器阵列,该阵列可包括具有8

×

8存储器阵列的2个副本,该副本具有被布置成八(8)行与八(8)列的两(2) 个块的一百二十八(128)个位单元。另外,可在第一单个周期中,诸如例如在读取操作期间的第一读取周期(“读取”)中读取8

×

8阵列412a的第一块中的六十四(64)个位单元。另外,可在第二单个周期中,诸如例如在读取操作期间的第二读取周期(“读取”)中读取8

×

8阵列412a的第二块中的六十四(64)个位单元。因此,可使用双脉冲读取操作在2个周期中读取128位,其中在第一读取周期中读取64个位单元,并且在第二读取周期中读取64个其他位单元。另外,8

×

8位单元阵列412a、412b的多个块可被配置成允许在读取操作期间在双脉冲读取周期(“读取”)的每个读取周期中激活和读取至少四(4)个字线。

[0036]

图5示出了根据本文所述的具体实施的具有布置成32

×

16阵列的位单元204的存储器阵列电路502的图500。

[0037]

如图5所示,存储器阵列电路502可包括具有多个16

×

8阵列(514a, 514b,514c,514d)块的32

×

16阵列,该块包括多个8

×

8阵列(512a, 512b,...,512h)。例如,32

×

16阵列502可包括具有多个8

×

8阵列512a、 512b的第一16

×

8阵列514a,并且另外,32

×

16阵列502可包括具有多个 8

×

8阵列512c、512d的第二16

×

8阵列514b。此外,32

×

16阵列502可包括具有多个8

×

8阵列512e、512f的第三16

×

8阵列514c,并且另外, 32

×

16阵列502可包括具有多个8

×

8阵列512g、512h的第四16

×

8阵列 514d。另外,在一些情况下,每个8

×

8阵列(512a,512b,...,512h)可具有以如图4所述的方式起作用和操作的对应的逻辑阵列(518a,518b,..., 518h)。

[0038]

在一些情况下,存储器阵列电路502可包括用于每个位单元阵列块或组的控制电路,诸如例如上组或顶组(514a,514c)和下组或底组(514b, 514d)。例如,可提供第一读出放大器和驱动器逻辑(sa+驱动器)530a 以及第一多路复用器和输入

‑

输出逻辑(mux+io)540a作为具有第一16

×

8 阵列514a和第三16

×

8阵列514c的上组的共享控制电路。另外,可

提供第二读出放大器和驱动器逻辑(sa+驱动器)530b以及第二多路复用器和输入

‑

输出逻辑(mux+io)540b作为具有第二16

×

8阵列514b和第四16

×

8 阵列514d的下组的共享控制电路。在一些情况下,存储器阵列电路502可包括其他共享控制电路,诸如例如用于第一16

×

8阵列514a和第二16

×

8阵列514b的第一字线驱动器电路(wdx)520a以及用于第三16

×

8阵列 514c和第四16

×

8阵列514d的第二字线驱动器电路(wdx)520b。另外,在一些情况下,存储器阵列电路502可包括在四个16

×

8阵列(514a,514b,514c,514d)之间共享的时钟电路(clk)524和输入

‑

输出时钟电路 (io clk)528。

[0039]

此外,在一些具体实施中,如图3所示的1

×

8位单元阵列可被扩展或修改为包括具有多个16

×

8阵列514a、514b、514c、514d的32

×

16存储器阵列502。例如,1

×

8阵列可被修改为每个16

×

8位单元阵列514a、514b、 514c、514d包括8

×

8位单元阵列的8个副本,从而提供位单元204的 32

×

16存储器阵列502。在这种情况下,图5所示的32

×

16存储器电路502 可被适配成提供位单元204的32

×

16存储器阵列,该存储器阵列可包括 16

×

8存储器阵列的4个副本,该副本具有被布置成十六(16)行与八(8) 列的四(4)个块的五百一十二(512)个位单元。另外,可在第一单个周期中,诸如例如在读取操作期间的第一读取周期(“读取”)中读取16

×

8 阵列512a、512b的第一块和第二块中的二百五十六(256)个位单元。另外,可在第二单个周期中,诸如例如在读取操作期间的第二读取周期 (“读取”)中读取16

×

8阵列512c、512d的第三块和第四块中的二百五十六(256)个位单元。因此,可使用双脉冲读取操作在2个周期中块读取 512位,其中在第一读取周期中读取256个位单元,并且另外,在第二读取周期中读取256个其他位单元。此外,多个16

×

8位单元阵列514a、 514b、514c、514d块可被配置成允许在读取操作期间在双脉冲读取周期 (“读取”)的每个读取周期中激活和读取至少八(8)个字线。

[0040]

图6示出了根据本文所述的各种具体实施的具有布置成多个交织的 32

×

16位单元阵列块的位单元的存储器阵列电路602的图600。在一些具体实施中,可将多个32

×

16位单元阵列块交织以在写入操作期间分配引脚,其中可对来自所有16个条目的相同4个字节执行块读取。

[0041]

如图6所示,存储器阵列电路602包括多个32

×

16阵列块,其中每个 32

×

16阵列块具有多个16

×

8阵列块,每个16

×

8阵列块具有多个8

×

8阵列。例如,多个32

×

16阵列块可包括具有八(8)个8

×

8阵列的第一32

×

16块[0] 阵列,并且另外,多个32

×

16阵列块可包括具有八(8)个8

×

8阵列的第二 32

×

16块[1]阵列。此外,多个32

×

16阵列块可包括具有八(8)个8

×

8阵列的第三32

×

16块[2]阵列,并且另外,多个32

×

16阵列块可包括具有八(8) 个8

×

8阵列的第四32

×

16块[3]阵列。另外,在一些情况下,每个32

×

16阵列(块[0],块[1],块[2],块[3])可以如图5所述的方式起作用和操作。

[0042]

此外,在一些具体实施中,如图3所示的1

×

8位单元阵列可被扩展或修改为包括四(4)个32

×

16存储器块阵列(块[0],块[1],块[2],块 [3]),其中每个存储器块阵列具有八(8)个8

×

8阵列。例如,1

×

8阵列可被修改为每个32

×

16位单元块阵列(块[0],块[1],块[2],块[3])包括8

×

8 位单元阵列的8个副本,从而提供位单元204的32

×

16存储器阵列602的4 个块。在这种情况下,如图5所示的32

×

16存储器电路502可被适配成提供4个32

×

16存储器位单元阵列块,该块可包括32

×

16存储器阵列的4个副本,该副本具有被布置成并且也交织成三十二(32)行与十六(16)列的四(4)个块的五百一十二(512)个位单元。另外,可在

第一单个周期中,诸如例如在读取操作期间的第一读取周期(“读取”)中读取32

×

16 阵列的第一块和第二块(块[0],块[1])中的五百一十二(512)个位单元。另外,可在第二单个周期中,诸如例如在读取操作期间的第二读取周期(“读取”)中读取32

×

16阵列的第三块和第四块(块[2],块[3])中的五百一十二(512)个位单元。因此,可使用双脉冲读取操作在2个周期中块读取1024位,其中在第一读取周期中读取512个位单元,并且另外,在第二读取周期中读取512个其他位单元。此外,多个32

×

16位单元块阵列块(块[0],块[1],块[2],块[3])可被适配和配置成允许在读取操作期间在双脉冲读取周期(“读取”)的每个读取周期中激活和读取至少八(8)个字线(例如,8个竖直字线)。

[0043]

图7示出了根据本文所述的各种具体实施的具有布置成多个128

×

16阵列组的位单元的存储器阵列电路702的图700。在一些具体实施中,多个 128

×

16位单元阵列块可包括四(4)个128

×

16存储器阵列组(组_0,组 _1,组_2,组_3),其中可参考16个条目来执行条目读取,其中每个条目具有64个字节,64个字节是指512位。另外,可参考16个32

×

16阵列块来执行块读取,其中在块读取操作期间,可利用单个32

×

16块读取来在两个周期中读取512个位单元。

[0044]

如图7所示,存储器阵列电路702包括多个128

×

16阵列组(组_0,组 _1,组_2,组_3),其中每个组具有多个32

×

16阵列块(块[0],块[1],块 [2],...],块[15]),这些块基于多个8

×

8阵列。例如,多个128

×

16阵列组包括具有四(4)个32

×

16阵列块(块[0],块[1],块[2],块[3])的第一 128

×

16组[0]阵列,并且另外,多个128

×

16阵列组可包括具有四(4)个32

×

16阵列块(块[4],块[5],块[6],块[7])的第二128

×

16组[1]阵列。此外,多个128

×

16阵列组可包括具有四(4)个32

×

16阵列块(块[8],块 [9],块[10],块[11])的第三128

×

16组[2]阵列,并且另外,多个128

×

16阵列组可包括具有四(4)个32

×

16阵列块(块[12],块[13],块[14],块 [15])的第四128

×

16组[3]阵列。另外,在一些情况下,每个128

×

16组阵列(组[0],组[1],组[2],组[3])可以如参考图6所述的方式起作用和操作。

[0045]

此外,在一些具体实施中,如图3所示的1

×

8位单元阵列可被扩展或修改为包括四(4)个128

×

16存储器组阵列(组[0],组[1],组[2],组 [3]),其中每个存储器组阵列具有四(4)个32

×

16阵列。例如,1

×

8阵列可被修改为每个128

×

16位单元组阵列(组[0],组[1],组[2],组[3])包括 8

×

8位单元阵列的32个副本,从而提供位单元204的128

×

16存储器阵列 702的4个组。在这种情况下,如图6所示的128

×

16存储器电路602可被适配成提供4个128

×

16存储器位单元阵列组,该组可包括128

×

16存储器阵列的4个副本,其中每个副本具有被布置成三十二(32)行与十六 (16)列的四(4)个块的五百一十二(512)个位单元。另外,可在第一单个周期中,诸如例如在读取操作期间的第一读取周期(“读取”)中读取每个组中的32

×

16阵列的第一块和第二块中的五百一十二(512)个位单元。另外,可在第二单个周期中,诸如例如在读取操作期间的第二读取周期(“读取”)中读取每个组中的32

×

16阵列的第三块和第四块中的五百一十二(512)个位单元。

[0046]

因此,可使用双脉冲读取操作在2个周期中块读取2048位,其中在第一读取周期中读取1024个位单元,并且另外,在第二读取周期中读取1024 个其他位单元。此外,多个128

×

16位单元组阵列组(组[0],组[1],组 [2],组[3])可被适配和配置成允许在读取操作期间在双脉冲读取周期 (“读取”)的每个读取周期中激活和读取至少八(8)个字线(例如,8 个竖直字线)。

[0047]

图8示出了根据本文所述的各种具体实施的具有布置成64

×

16位单元阵列中的多个交织块的位单元的存储器阵列电路802的图800。在一些具体实施中,可将64

×

16位单元阵列中的多个块与八(8)个16

×

8副本块交织,并且可在单个周期中对512个位单元执行块读取。当写入时,可基于每个块或每个组中的多个块的对应的行地址(ra)来将列地址(ca)交织。此外,可在写入操作期间,例如通过基于每个块或每个组的多个块的行地址(ra)将列地址(ca)交织来将每个组的多个块中的每个块交织。

[0048]

如图8所示,存储器阵列电路802包括具有多个交织的16

×

8块的 64

×

16位单元阵列,其中每个块具有多个4

×

8阵列。例如,多个16

×

8阵列块可包括具有十六(16)个8

×

8阵列的第一4

×

8块阵列(块[0]),并且多个16

×

8阵列块可包括具有十六(16)个8

×

8阵列的第二4

×

8块阵列(块 [1])。此外,可在写入操作期间将每个4

×

8阵列(块[0],块[1])交织。此外,在一些具体实施中,可在单个周期中,诸如例如在读取操作期间的第一读取周期(“读取”)中读取五百一十二(512)个位单元。另外,多个 4

×

8位单元阵列块(块[0],块[1])可被适配和配置成允许在读取操作期间在单脉冲读取周期(“读取”)的每个读取周期中激活和读取至少八(8) 个字线(例如,8个竖直字线)。

[0049]

图9示出了根据本文所述的各种具体实施的具有布置成多个交织的 32

×

16位单元阵列块的位单元的存储器阵列电路902的图900。在一些具体实施中,可将多个16

×

8位单元阵列块交织以在写入操作期间分配引脚,其中可对来自所有16个条目的相同4个字节执行块读取。

[0050]

如图9所示,存储器阵列电路602包括多个32

×

16阵列块,其中每个 32

×

16阵列块具有多个交织的16

×

8阵列块,每个16

×

8阵列块具有两个8

×

8 阵列。例如,多个32

×

16阵列块可包括具有八(8)个交织的8

×

8阵列的第一32

×

16块[0]阵列,并且另外,多个32

×

16阵列块可包括具有八(8)个交织的8

×

8阵列的第二32

×

16块[1]阵列。此外,多个32

×

16阵列块可包括具有八(8)个交织的8

×

8阵列的第三32

×

16块[2]阵列,并且另外,多个 32

×

16阵列块可包括具有八(8)个交织的8

×

8阵列的第四32

×

16块[3]阵列。另外,在一些情况下,每个交织的32

×

16阵列(块[0],块[1],块[2],块[3])可以如图5至图6所述的方式起作用和操作。

[0051]

此外,在一些具体实施中,可在读取操作期间在第一单个读取周期 (“读取”)中读取32

×

16阵列的第一块和第二块(块[0],块[1])中的五百一十二个(512)位单元。另外,可在读取操作期间在第二单个读取周期 (“读取”)中读取32

×

16阵列的第三块和第四块(块[2],块[3])中的五百一十二(512)个位单元。因此,可使用双脉冲读取操作在2个周期中块读取1024位,其中在第一读取周期中读取512个位单元,并且在第二读取周期中读取512个其他位单元。另外,多个32

×

16位单元块阵列块(块 [0],块[1],块[2],块[3])可被适配和配置成允许在双脉冲读取周期的每个读取周期中激活和读取至少八(8)个字线(例如,8个竖直字线)。

[0052]

图10a至图10b示出了根据本文所述的具体实施的具有呈多个128

×

16 阵列组的位单元的存储器阵列电路1002a、1002b的多个图1000a、 1000b。在一些具体实施中,多个128

×

16阵列组中的每个128

×

16组被布置成多个交织的32

×

16位单元阵列块,并且可将多个16

×

8位单元阵列块交织以在写入操作期间分配引脚,其中可对来自所有16个条目的相同4个字节执行块读取。另外,在一些具体实施中,存储器阵列电路1002a、1002b 可包括四

(4)个128

×

16存储器阵列组,其中可在条目读取操作期间读取 16个条目,其中每个条目具有64个字节(512位)。另外,参考块读取操作,可在两个周期中读取16个32

×

16位单元块,其中可在两个周期中读取单个32

×

16(512位)块。

[0053]

如图10a至图10b所示,多组存储器阵列电路1000a、1000b包括多个128

×

16阵列组(组[0],组[1],组[2],组[3]),其中每个组具有多个交织的32

×

16阵列块(块[0],块[1],块[2],...,块[15]),该多个块基于多个交织的16

×

8阵列。例如,多个128

×

16阵列组包括具有四(4)个交织的 32

×

16阵列块(块[0],块[1],块[2],块[3])的第一128

×

16组[0]阵列,并且另外,多个128

×

16阵列组可包括具有四(4)个交织的32

×

16阵列块 (块[4],块[5],块[6],块[7])的第二128

×

16组[1]阵列。此外,多个 128

×

16阵列组可包括具有四(4)个交织的32

×

16阵列块(块[8],块[9],块[10],块[11])的第三128

×

16组[2]阵列,并且另外,多个128

×

16阵列组可包括具有四(4)个交织的32

×

16阵列块(块[12],块[13],块[14],块 [15])的第四128

×

16组[3]阵列。此外,在各种情况下,每个128

×

16组阵列(组[0],组[1],组[2],组[3])可以如参考图6至图9所述的方式起作用和操作和/或表现。

[0054]

此外,在一些具体实施中,如图3所示的1

×

8位单元阵列可被扩展或修改为包括四(4)个128

×

16存储器组阵列(组[0],组[1],组[2],组 [3]),其中每个存储器组阵列具有四(4)个交织的32

×

16位单元阵列。例如,1

×

8阵列可被修改为每个128

×

16位单元组阵列(组[0],组[1],组[2],组[3])包括交织的8

×

8位单元阵列的32个副本,从而提供位单元204的 128

×

16存储器阵列702的4个组。在这种情况下,如图10a至图10b所示的128

×

16存储器电路1002a、1002b可被适配成提供4个128

×

16存储器位单元阵列组,该组可包括128

×

16存储器阵列的4个副本,其中每个副本具有被布置成三十二(32)行与十六(16)列的四(4)个交织块的五百一十二(512)个位单元。另外,可在读取操作期间在第一单个读取周期中读取每个组中的32

×

16阵列的第一块和第二块中的五百一十二(512)个位单元。此外,可在读取操作期间在第二单个读取周期中读取每个组中的32

×

16 阵列的第三块和第四块中的五百一十二(512)个位单元。

[0055]

因此,可使用双脉冲读取操作在2个周期中块读取1024位,其中在第一读取周期中读取512个位单元,并且另外,在第二读取周期中读取512 个其他位单元。此外,多个128

×

16位单元组阵列组(组[0],组[1],组 [2],组[3])可被适配和配置成允许在读取操作期间在双脉冲读取周期 (“读取”)的每个读取周期中激活和读取至少八(8)个字线(例如,8 个竖直字线)。

[0056]

应当预期的是,权利要求的主题不限于本文提供的具体实施和图示,而是包括根据权利要求的那些具体实施的修改形式,包括具体实施的部分和不同具体实施的元件的组合。应当理解,在任何此类具体实施的开发中,如在任何工程或设计项目中,应作出许多具体实施特定的决策以实现开发者的特定目标,诸如符合系统相关和业务相关的约束,这些约束可能在不同具体实施之间变化。此外,应当理解,此类开发工作可能是复杂且耗时的,但是尽管如此,对于受益于本公开的普通技术人员而言,这仍然是设计、制造和生产的常规任务。

[0057]

本文描述了一种设备的各种具体实施。该设备可包括位单元。该设备可包括耦接到位单元的水平位线,并且水平位线可包括相对于位单元沿水平方向设置的多个第一读取位线。该设备可包括耦接到位单元的竖直位线,并且竖直位线可包括相对于位单元沿竖直

方向设置的多个第二读取位线。

[0058]

本文描述了一种设备的各种具体实施。该设备可包括位单元阵列。该设备可包括耦接到阵列中的位单元的水平位线,并且水平位线可包括相对于位单元阵列沿水平方向设置的第一读取位线。该设备可包括耦接到阵列中的位单元的竖直位线,并且竖直位线可包括相对于位单元阵列沿竖直方向设置的第二读取位线。

[0059]

本文描述了一种设备的各种具体实施。该设备可包括布置成多个组的位单元阵列,其中多个组中的每个组具有多个块。该设备可包括耦接到阵列中的位单元的水平位线,并且水平位线可包括相对于位单元阵列沿水平方向设置的第一读取位线。该设备可包括耦接到阵列中的位单元的竖直位线,并且竖直位线可包括相对于位单元阵列沿竖直方向设置的第二读取位线。

[0060]

已经详细地参考了各种具体实施,其示例在附图和图示中示出。在以下具体描述中,阐述了许多具体细节以提供对本文提供的公开内容的透彻理解。然而,可以在没有这些具体细节的情况下实践本文提供的公开内容。在一些其他情况下,没有详细描述熟知的方法、规程、部件、电路和网络,以便不会不必要地模糊实施方案的细节。

[0061]

还应当理解,虽然术语“第一”、“第二”等在本文中可用于描述各种元件,但这些元件不应受这些术语的限制。这些术语仅用于将一个元件与另一个元件区分开。例如,第一元件可被称为第二元件,并且类似地,第二元件可被称为第一元件。第一元件和第二元件分别均为元件,但它们不被认为是相同的元件。

[0062]

在本文提供的本公开的描述中使用的术语是为了描述特定具体实施的目的,并且不旨在限制本文提供的公开内容。如本文中提供的公开内容和所附权利要求的描述中使用的,单数形式“一个”、“一种”和“该”旨在也包括复数形式,除非上下文另有明确指示。如本文所用,术语“和/ 或”是指并涵盖相关联的列出项目中的一者或多者的任何和所有可能组合。当在本说明书中使用时,术语“包括”、“包含”和/或“含有”指定所述特征、整数、步骤、操作、元件和/或部件的存在,但不排除一个或多个其他特征、整数、步骤、操作、元件、部件和/或它们的组的存在或添加。

[0063]

如本文所用,根据上下文,术语“如果”可被解释为意指“当...时”或“在...时”或“响应于确定”或“响应于检测到”。类似地,根据上下文,短语“如果确定...”或“如果检测到[所述条件或事件]”可被解释为意指“在确定...时”或“响应于确定...”或“在检测到[所述条件或事件] 时”或“响应于检测到[所述条件或事件]”。术语“上”和“下”;“上部”和“下部”;“向上”和“向下”;“在...下方”和“在...上方”;以及指示给定点或元件上方或下方的相对位置的其他类似术语可与本文所述的各种技术的一些具体实施结合使用。

[0064]

虽然前述内容涉及本文所述的各种技术的具体实施,但是可以根据本文的公开内容想出其他和另外的具体实施,本文的公开内容可以由所附权利要求确定。

[0065]

虽然以特定于结构特征和/或方法动作的语言描述了本主题,但应当理解,所附权利要求中限定的主题不一定限于上述特定特征或动作。相反,上述的具体特征和动作被公开为实现权利要求的示例性形式。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1