存储器装置的制作方法

1.本公开涉及一种半导体装置,特别涉及一种包括一个非栅极全环(non

‑

gaa)晶体管与一或多个栅极全环(gate

‑

all

‑

around,gaa)晶体管的存储器装置。

背景技术:

2.集成电路(integrated circuit,ic)有时会包括一次性可编程(one

‑

time

‑

programmable,otp)存储器以提供非易失性存储器(non

‑

volatile memory,nvm),非易失性存储器中的数据并不会因为ic的电源中断而遗失。otp装置的其中一种类型包括抗熔丝(anti

‑

fuse)存储器。抗熔丝存储器包括一定数量的抗熔丝存储器单元(cell,或位元单元(bit cell)),它们的端子(terminal)在编程之前是未连接的,且在编程之后是短路的(例如:连接的)。抗熔丝存储器可以是基于金属氧化物半导体(metal

‑

oxide

‑

semiconductor,mos)技术。举例来说,抗熔丝存储器单元可包括编程mos晶体管(或是mos电容)及至少一个读取mos晶体管。编程mos晶体管的栅极介电质可被崩溃(break down),以使编程mos晶体管的栅极与源极或漏极区域互连(interconnect)。根据编程mos晶体管的栅极介电质是否崩溃,经由读取流经编程mos晶体管与读取mos晶体管的合成电流(resultant current),抗熔丝存储器单元可表示不同的数据位元。抗熔丝存储器单元具有逆向工程防护(reverse

‑

engineering proofing)的有利特征,因为无法经由逆向工程判断抗熔丝单元的编程状态。

技术实现要素:

3.本公开实施例提供一种存储器装置。上述存储器装置包括形成于一基板的第一区域中的第一晶体管。第一晶体管包括自上述基板突出的突出结构,以及耦接至突出结构的第一端的第一源极/漏极(s/d)结构。上述存储器装置包括形成于上述基板的第二区域中的第二晶体管。第二晶体管包括垂直地彼此间隔的多个第一半导体层、耦接至多个第一半导体层的第一端的第二源极/漏极结构、以及耦接至多个第一半导体层的第二端的第三源极/漏极结构。第一区域与第二区域通过隔离结构彼此横向地分隔。

4.本公开实施例提供一种一次性可编程(otp)存储器装置。上述一次性可编程存储器装置包括形成于一基板的第一区域中的编程晶体管。上述一次性可编程存储器装置包括串联地电性连接至编程晶体管且形成于上述基板的第二区域中的第一读取晶体管。第一区域通过隔离结构与第二区域横向分隔。编程晶体管包括第一栅极结构,第一栅极结构跨坐于突出自上述基板的突出结构,而第一读取晶体管包括第二栅极结构,第二栅极结构包裹环绕多个第一纳米结构的每一者,其中多个第一纳米结构彼此间垂直地分隔。

5.本公开实施例提供一种存储器装置的制造方法。上述存储器装置的制造方法包括在一基板上定义第一主动区与第二主动区。第一主动区与第二主动区通过隔离结构彼此横向地分隔。上述存储器装置的制造方法包括在第一主动区中形成第一晶体管。第一晶体管包括自上述基板突出的突出结构所形成的第一通道、跨坐于第一通道上方的第一主动栅极结构、以及至少包括耦接至第一通道的一端的第一源极/漏极结构。上述存储器装置的制造

方法包括在第二主动区中形成第二晶体管。第二晶体管包括设置于上述基板上方的一或多个半导体层所共同形成的第二通道、包裹围绕第二通道的第二主动栅极结构、耦接至第二通道的一端的第二源极/漏极结构、以及耦接至第二通道的另一端的第三源极/漏极结构。

附图说明

6.本公开的态样自后续实施方式及附图可更佳理解。须强调的是,依据产业的标准作法,各种特征并未按比例绘制。事实上,各种特征的尺寸可能任意增加或减少以清楚论述。

7.图1是根据一些实施例所示,存储器单元的范例性电路示意图。

8.图2是根据一些实施例所示,另一个存储器单元的范例性电路示意图。

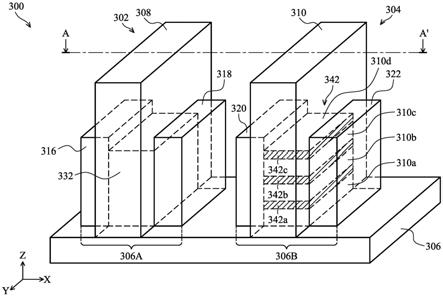

9.图3是根据一些实施例所示,包含图1所示的存储器单元的存储器装置的透视图。

10.图4是根据一些实施例所示,包含图2所示的存储器单元的存储器装置的透视图。

11.图5是根据一些实施例所示,用于形成存储器装置的各种范例性布局。

12.图6是根据一些实施例所示,用于形成存储器装置的各种范例性布局。

13.图7是根据一些实施例所示,用于形成存储器装置的各种范例性布局。

14.图8是根据一些实施例所示,用于形成存储器装置的各种范例性布局。

15.图9是根据一些实施例所示,用于形成存储器装置的各种范例性布局。

16.图10是根据一些实施例所示,用于形成存储器装置的各种范例性布局。

17.图11是根据一些实施例所示,定义存储器装置的第一主动区与第二主动区的范例性方法的流程图。

18.图12是根据一些实施例所示,由图11的方法所制造的存储器装置在各个制造阶段的截面图。

19.图13是根据一些实施例所示,由图11的方法所制造的存储器装置在各个制造阶段的截面图。

20.图14是根据一些实施例所示,由图11的方法所制造的存储器装置在各个制造阶段的截面图。

21.图15是根据一些实施例所示,由图11的方法所制造的存储器装置在各个制造阶段的截面图。

22.图16是根据一些实施例所示,由图11的方法所制造的存储器装置在各个制造阶段的截面图。

23.图17是根据一些实施例所示,定义存储器装置的第一主动区与第二主动区的另一种范例性方法的流程图。

24.图18是根据一些实施例所示,遵循图11或图17的方法以制造存储器装置的范例性方法的流程图。

25.图19a至图19c是根据一些实施例所示,由图18的方法所制造的存储器装置在各个制造阶段的截面图。

26.图20至图26是根据一些实施例所示,由图18的方法所制造的存储器装置在各个制造阶段的截面图。

27.图27a至图27c是根据一些实施例所示,由图18的方法所制造的存储器装置在各个

制造阶段的截面图。

28.图28是根据一些实施例所示,由图18的方法所制造的存储器装置在各个制造阶段的截面图。

29.图29是根据一些实施例所示,由图18的方法所制造的存储器装置的另一个实施例的截面图。

30.图30是根据一些实施例所示,由图18的方法所制造的存储器装置的又一个实施例的截面图。

31.图31是根据一些实施例所示,由图18的方法所制造的存储器装置的又一个实施例的截面图。

32.图32是根据一些实施例所示,由图18的方法所制造的存储器装置的又一个实施例的截面图。

33.其中,附图标记说明如下:

34.100:存储器单元

35.110:第一晶体管

36.110g:栅极

37.110s:源极

38.110d:漏极

39.120:第二晶体管

40.120g:栅极

41.120s:源极

42.120d:漏极

43.130:编程字元线

44.132:读取字元线

45.134:位元线

46.136:电阻器

47.200:存储器单元

48.210:第一晶体管

49.210g:栅极

50.210s:源极

51.210d:漏极

52.220:第二晶体管

53.220g:栅极

54.220s:源极

55.220d:漏极

56.230:第三晶体管

57.230g:栅极

58.230s:源极

59.230d:漏极

60.240:编程字元线

61.242:第一读取字元线

62.244:第二读取字元线

63.250:位元线

64.300:存储器装置

65.302:编程晶体管

66.304:读取晶体管

67.306:半导体基板

68.306a:第一主动区

69.306b:第二主动区

70.308:栅极结构

71.310:栅极结构

72.310a~310d:栅极堆叠

73.316~322:源极/漏极结构

74.332:突出结构

75.342:半导体层

76.342a~342c:半导体层

77.a

‑

a’:线段

78.400:存储器装置

79.402:编程晶体管

80.404:第一读取晶体管

81.406:第二读取晶体管

82.408:半导体基板

83.408a:第一主动区

84.408b:第二主动区

85.410~414:栅极结构

86.416~424:源极/漏极结构

87.432:突出结构

88.442:半导体层

89.442a~442c:半导体层

90.452:半导体层

91.452a~452c:半导体层

92.500:布局

93.501:单元边界

94.502a:主动特征

95.502b:主动特征

96.504:栅极特征

97.506:栅极特征

98.508~514:次主动特征

99.520~532:特征

100.534:互连结构

101.536:位元线

102.538:编程字元线

103.540:读取字元线

104.w1:宽度

105.w2:宽度

106.600:布局

107.602:虚拟栅极结构

108.604:虚拟栅极结构

109.700:布局

110.702:特征

111.704:互连结构

112.800:布局

113.802a:主动区

114.900:布局

115.901:单元边界

116.902a:主动特征

117.902b:主动特征

118.904~908:栅极特征

119.910~918:次主动特征

120.920~928:特征

121.930~934:特征

122.940:互连结构

123.942:位元线

124.944:编程字元线

125.946:第一读取字元线

126.948:第二读取字元线

127.w3:宽度

128.w4:宽度

129.1000:布局

130.1002:虚拟栅极结构

131.1004:虚拟栅极结构

132.1100:方法

133.1102~1110:操作

134.1200:存储器装置

135.1202:半导体基板

136.1202a:第一区域

137.1202b:第二区域

138.1203:顶部表面

139.1304:图案化遮罩

140.1306:硬遮罩

141.1308:图案化光阻层

142.1205:底部表面

143.1207:侧壁

144.1306:硬遮罩

145.1402:凹槽

146.1502:第一半导体层

147.1502a~1502c:第一半导体层

148.1504:第二半导体层

149.1504a~1504c:第二半导体层

150.1602a:第一主动结构

151.1602b:第二主动结构

152.1603a:第一主动区

153.1603b:第二主动区

154.1610:半导体层

155.1610a~1610c:半导体层

156.1620:半导体层

157.1620a~1620c:半导体层

158.1625a:图案化遮罩

159.1625b:图案化遮罩

160.1630:隔离结构

161.1700:方法

162.1702~1712:操作

163.1800:方法

164.1802~1820:操作

165.1902:第一虚拟栅极结构

166.1904:虚拟栅极介电质

167.1906:虚拟栅极

168.1908:硬遮罩

169.1910:栅极间隔物

170.1912:第二虚拟栅极结构

171.1914:虚拟栅极介电质

172.1916:虚拟栅极

173.1918:硬遮罩

174.1920:栅极间隔物

175.2001:阻挡遮罩

176.2010:半导体层

177.2010a~2010c:半导体层

178.2020:半导体层

179.2020a~2020c:半导体层

180.2102:内部间隔物

181.2202:源极/漏极结构

182.2204:源极/漏极结构

183.2210:gaa晶体管

184.h1:高度

185.h2:高度

186.2301:阻挡遮罩

187.2402:源极/漏极结构

188.2404:源极/漏极结构

189.2410:非gaa晶体管

190.h3:高度

191.2500:层间介电质

192.2702:第一主动栅极结构

193.2704:栅极介电质

194.2706:栅极金属

195.2712:第二主动栅极结构

196.2714:栅极介电质

197.2716:栅极金属

198.2800:层间介电质

199.2802:互连结构

200.2803:介电质硬遮罩

201.2804~2812:互连结构

202.2813:介电质硬遮罩

203.2814:互连结构

204.2816:互连结构

205.2900:虚拟栅极结构

206.2902:虚拟栅极介电质

207.2904:虚拟栅极

208.2906:间隔物

209.2908:介电质硬遮罩

210.2920:虚拟栅极结构

211.2922:虚拟栅极介电质

212.2924:虚拟栅极

213.2926:间隔物

214.2928:介电质硬遮罩

215.3000:gaa晶体管

216.3002:半导体层

217.3004:源极/漏极结构

218.3006:主动栅极结构

219.3008:互连结构

220.3010:互连结构

221.3100:虚拟栅极结构

222.3102:虚拟栅极介电质

223.3104:虚拟栅极

224.3106:间隔物

225.3108:介电质硬遮罩

226.3120:虚拟栅极结构

227.3122:虚拟栅极介电质

228.3124:虚拟栅极

229.3126:间隔物

230.3128:介电质硬遮罩

231.3200:非gaa晶体管

232.3202:主动栅极结构

233.3204:栅极介电质

234.3206:栅极金属

235.3208:栅极间隔物

具体实施方式

236.以下的公开提供许多不同实施例或范例,用以实施本公开的不同特征。本公开的各部件及排列方式,其特定范例叙述于下以简化说明。理所当然的,这些范例并非用以限制本公开。举例来说,若叙述中有着第一特征成形于第二特征之上或上方,其可能包含第一特征与第二特征以直接接触成形的实施例,亦可能包含有附加特征形成于第一特征与第二特征之间,而使第一特征与第二特征间并非直接接触的实施例。此外,本公开可在多种范例中重复参考数字及/或字母。该重复的目的是为简化及清晰易懂,且本身并不规定所讨论的多种实施例及/或配置间的关系。

237.进一步来说,本公开可能会使用空间相对术语,例如“在

…

下方”、“下方”、“低于”、“在

…

上方”、“高于”及类似词汇,以便于叙述图式中一个元件或特征与其他元件或特征间的关系。除了图式所描绘的方位外,空间相对术语亦欲涵盖使用中或操作中的装置其不同方位。设备可能会被转向不同方位(旋转90度或其他方位),而此处所使用的空间相对术语则可相应地进行解读。

238.在当代的半导体装置制造制程中,单一晶圆上会制造有大量的半导体装置,例如硅通道n型场效晶体管(n

‑

type field effect transistor,nfet)以及硅锗通道p型场效晶体管(pfet)。非平面晶体管装置的构造,例如鳍式(fin

‑

based)晶体管(通常被称为“finfet”),可提供比平面晶体管(planar transistor)更高的装置密度与更好的性能。一些先进的非平面晶体管构造,例如纳米片(nanosheet)(或纳米线(nanowire))晶体管,可进一步提供更胜于finfet的性能。与通道被栅极结构部分包裹(wrap)(例如:跨坐

(straddle))的finfet相比,纳米片晶体管通常包括包裹环绕(wrap around)一或多个纳米片的整个周长的栅极结构,以改进通道电流的控制。举例来说,在具有相似尺寸的finfet与纳米片晶体管中,纳米片晶体管可提供较大的驱动电流(driving current,i

on

)以及较小的次临界漏电流(subthreshold leakage current,i

off

)。具有完全包裹环绕其通道的栅极结构的晶体管通常称为栅极全环(gate

‑

all

‑

around,gaa)晶体管;具有部分包裹环绕或覆盖其通道的栅极结构的晶体管,包括finfet以及平面晶体管,通常被称为非栅极全环(non

‑

gaa)晶体管。

239.鉴于纳米片晶体管与finfet相较的下的相对性能,一些现行的存储器装置已在纳米片晶体管的配置中配置对应的存储器单元(cell)。举例来说,抗熔丝(anti

‑

fuse)存储器单元可包括编程(programming)晶体管与读取(reading)晶体管,它们中的每一者被配置为gaa晶体管。然而,因为gaa晶体管通常具有多个独立的纳米结构(例如:纳米片、纳米线),因此当对抗熔丝存储器单元进行编程时,可能仅有一部分的栅极介电质(例如:耦接至其中一个纳米片)被破坏,这会不利地导致抗熔丝存储器单元具有高电阻及/或大范围变化的崩溃电压(breakdown voltage,v

bd

)。因此,现行的已采用了gaa配置的存储器单元并非是完全令人满意的。

240.本公开提供存储器单元的各种实施例。在一些实施例中,所公开的存储器单元包括抗熔丝存储器单元,抗熔丝存储器单元包括编程晶体管以及一或多个读取晶体管。编程晶体管被配置为非gaa晶体管(例如:finfet、平面晶体管),而一或多个读取晶体管的每一者被配置为gaa晶体管。在基板上方,非gaa晶体管与一或多个gaa晶体管通过至少一个隔离结构(例如:浅沟槽隔离(shallow trench isolation,sti))彼此分隔。换句话说,非gaa晶体管可被形成在基板的第一主动区(active region)中,而gaa晶体管可被形成在第二主动区中,其中第一主动区与第二主动区通过sti彼此分隔(例如:电性隔离)。通过将编程晶体管配置为非gaa晶体管,以及将每个读取晶体管配置为gaa晶体管,如同本文所公开的,存储器单元可具有更加可控的崩溃电压(例如:变化范围较窄的崩溃电压),同时在编程存储器单元后维持gaa晶体管的性能。

241.图1是根据一些实施例所示,存储器单元100的范例性电路示意图。如图所示,存储器单元(有时称作存储器位元单元、存储器位元、或是位元)100包括第一晶体管110以及第二晶体管120。第一晶体管110及第二晶体管120中的每一者,可包括n型金属氧化物半导体场效晶体管(metal

‑

oxide

‑

semiconductor field

‑

effect

‑

transistor,mosfet)。第一晶体管110及第二晶体管120中的每一者,可包括另一种类型的mosfet,例如:p型mosfet。在一些其他实施例中,第一晶体管110及第二晶体管120中的至少一者,可由另一种类型的电子装置(例如:mos电容)所取代,但仍包含在本公开的范围中。第一晶体管110与第二晶体管120彼此串联地电性耦接。举例来说,第一晶体管110的漏极110d连接至第二晶体管120的源极120s。

242.存储器单元100可被配置为一次性可编程(one

‑

time

‑

programmable,otp)存储器单元,例如抗熔丝单元。应理解的是,存储器单元100可被配置为任何类型的存储器单元,这些存储器单元包括彼此串联地电性耦接的两个晶体管,这些存储器单元例如nor型非易失性存储器单元、动态随机存取存储器(dynamic random

‑

access memory,dram)单元、双晶体管静态随机存取存储器(static random

‑

access memory,sram)单元等。

243.当存储器单元100被配置为抗熔丝单元时,第一晶体管110可用作编程晶体管(因此亦可称为编程晶体管110),而第二晶体管120可用作读取晶体管(因此亦可称为读取晶体管120)。如此一来,第一晶体管的源极110s是浮动的(floating)(例如:未耦接至任何东西),而第一晶体管的栅极110g耦接至编程字元线(programming word line,wlp)130;另一方面,第二晶体管的栅极120g耦接至读取字元线(reading word line,wlr)132,而第二晶体管的漏极120d耦接至位元线(bl)134。

244.为了使存储器单元100编程,经由读取字元线132向栅极120g提供电压(例如:对应逻辑高(logic high)状态的正电压)以导通读取晶体管120。在读取晶体管120被导通之前、导通的同时或导通之后,足够高的电压(例如:崩溃电压(v

bd

)被施加到编程字元线130,且低电压(例如:对应逻辑低(logic low)的正电压)被施加到位元线134。低电压(施加在位元线134上)可被传送到漏极110d,以产生跨越漏极110d与栅极110g的v

bd

,以使编程晶体管110的栅极介电质的一部分(例如:漏极110d与栅极110g之间的部分)崩溃。在编程晶体管110的栅极介电质崩溃之后,互连栅极110与漏极110d的部分展现出相当于电阻的行为。举例来说,此部分可作为电阻器136,如图1中所象征性地显示的。在编程之前(在编程晶体管110的栅极介电质崩溃之前),当读取晶体管120被导通时,不会有导电路径存在于位元线134与编程字元线130之间;而在编程之后,当读取晶体管120被导通时,会有导电路径存在于位元线134与编程字元线130之间(例如:经由电阻器136)。

245.为了读取存储器单元100,与编程操作类似,读取晶体管120被导通且位元线134被耦接到对应逻辑低状态的电压。作为响应,正电压被施加到编程晶体管的栅极110g。如上所述,若编程晶体管110的栅极介电质并未崩溃,则在位元线134与编程字元线130之间不会存在导电路径。因此,相对低的电流自编程字元线130传导,穿过第一晶体管110及第二晶体管120并到达位元线134。若编程晶体管110的栅极介电质是崩溃的,则在位元线134与编程字元线130之间存在导电路径。因此,相对高的电流自编程字元线130传导,穿过第一晶体管110(现在等效于电阻器136)以及第二晶体管120,并到达位元线134。这种低电流以及高电流有时分别被称为存储器单元110的i

off

以及i

on

。耦接至位元线134的电路组件(例如:感测放大器(sensingamplifier))可差分(differentiate)i

off

与i

on

(反之亦然),并因此判断存储器单元100是呈现逻辑高(“1”)还是呈现逻辑低(“0”)。举例来说,当i

on

被读取时,存储器单元100可代表1;而当i

off

被读取时,存储器单元100可代表0。

246.图2是根据一些实施例所示,另一个存储器单元200的范例性电路示意图。存储器单元200与图1的存储器单元100相似,除了存储器单元200包括额外的读取晶体管。如图所示,存储器单元200包括第一晶体管210、第二晶体管220、以及第三晶体管230。第一晶体管210、第二晶体管220、以及第三晶体管230中的每一者,可包括n型mosfet。在一些其他实施例中,第一晶体管210、第二晶体管220、以及第三晶体管230中的每一者,可包括p型mosfet,但仍包含在本公开的范围中。第一晶体管210、第二晶体管220、以及第三晶体管230彼此串联地电性耦接。举例来说,第一晶体管210的漏极210d连接至第二晶体管220的源极220s,且第二晶体管220的漏极220d连接至第三晶体管230的源极230s。存储器单元200可作为抗熔丝单元(如上所述),其中第一晶体管210作为抗熔丝单元的编程晶体管,而第二晶体管220与第三晶体管230共同作为抗熔丝单元的读取晶体管。与存储器单元100相似,第一晶体管210(编程晶体管)的栅极210g耦接至编程字元线240,而第二晶体管220及第三晶体管230

(读取晶体管)的栅极220g及230g分别耦接至第一读取字元线(wlr1)242及第二读取字元线(wlr2)244,且第三晶体管230(读取晶体管)的漏极230d耦接至位元线250。其中第一晶体管210还包括源极210s。存储器单元200的操作基本上与存储器单元100的操作相似,因此不再赘述。

247.参照图3,图3显示范例性的存储器装置300的透视图。根据一些实施例,存储器装置300可为抗熔丝存储器单元的一部分,该抗熔丝存储器单元包括一个编程晶体管以及一个读取晶体管,例如图1的存储器单元100。图3的透视图是为抗熔丝存储器单元的概观,因此,抗熔丝存储器单元的一些特征在图3中可能无法辨识。存储器装置300(或与存储器装置300相似的存储器装置)的更多详细特征,将在下文中参照图19a至图29及图32的截面图进行图示与讨论。

248.如图3所示,存储器装置300包括编程晶体管302以及读取晶体管304。在一些实施例中,编程晶体管302被配置为非gaa晶体管(例如:finfet),而读取晶体管被配置为gaa晶体管(例如:纳米片晶体管)。编程晶体管302以及读取晶体管304可被形成在半导体基板306上、各别的不同的主动区中。举例来说,编程晶体管302被形成在半导体基板306的第一主动区306a(亦称为主动区306a)上方;而读取晶体管304被形成在半导体基板306的第二主动区306b(亦称为主动区306b)上方,其中第一主动区306a与第二主动区306b通过隔离结构(未显示于图3中)横向地(例如:沿着x方向)彼此分隔。这种主动区有时被称为氧化扩散(oxide diffusion,od)区。

249.具体来说,编程晶体管302包括设置于第一主动区306a上方的栅极结构308;而读取晶体管304包括设置于第二主动区306b上方的栅极结构310。彼此平行的栅极结构308与310可沿着横向方向(例如:y方向)指向(orientate)以及伸长(elongate)。在第一主动区306a中,编程晶体管302包括分别形成在栅极结构308的侧面上的源极/漏极结构316以及源极/漏极结构318。在第二主动区306b中,读取晶体管304包括分别形成在栅极结构310的侧面上的源极/漏极结构320以及源极/漏极结构322。

250.栅极结构308被形成为跨坐(straddle)于自基板306突出的结构332(下文中的鳍式或突出结构332),其中源极/漏极结构316与源极/漏极结构318分别耦接至突出结构332的两端,例如沿着x方向耦接至突出结构332的两端。突出结构332可作为编程晶体管302的通道。栅极结构310被形成为包裹围绕多个纳米结构342a、342b及342c(例如:纳米片、纳米线、或其他具有纳米尺度的尺寸的半导体层,因此亦称为半导体层342a

‑

342c),且具有耦接至它们各自的末端的源极/漏极结构320与源极/漏极结构322,例如沿着x方向耦接至它们各自的末端。半导体层342a

‑

342c(有时可被称为半导体层342)可共同作为读取晶体管304的通道。突出结构332以及半导体层342a

‑

342c可沿着横向方向(例如:x方向)指向与伸长,此横向方向与源极/漏极结构316

‑

322彼此对准的方向相同。如此一来,形成有源极/漏极结构316

‑

318与突出结构332的第一主动区306a,以及形成有源极/漏极结构320

‑

322与半导体层342a

‑

342c的第二主动区306b,尽管两者在横向上彼此分隔,但是它们可沿着横向方向(例如:x方向)彼此对准。

251.仍旧参照图3,且更详细地来说,在一些实施例中,栅极结构310可包括多个栅极堆叠。栅极堆叠的每一者可包括一或多个栅极介电质以及一或多个栅极金属(为使说明清晰而未显示于图3中)。栅极堆叠中的两个被配置以共同包裹围绕一或多个半导体层342a

‑

342c中的对应的一者。举例来说,栅极结构310包括栅极堆叠310a、310b、310c以及310d。栅极堆叠310a

‑

310d可具有与栅极结构310的宽度(沿着y方向)基本相似的宽度(沿着y方向),而半导体层342a

‑

342c的特征在于宽度(沿着y方向)小于栅极堆叠310a

‑

310d的宽度。栅极堆叠310a

‑

310d中的每一者可进一步包括沿着z方向延伸的部分,以与相邻的栅极堆叠接触。如此一来,栅极堆叠310a

‑

310d中相邻的两者可包裹半导体层342a

‑

342c中对应的一者的整个周长(perimeter)。

252.举例来说,栅极堆叠310a与栅极堆叠310b可共同地包裹围绕半导体层342a的至少四个侧面,且半导体层342a的两个侧面(或末端)分别耦接至源极/漏极结构320与源极/漏极结构322;栅极堆叠310b与栅极堆叠310c可共同地包裹围绕半导体层342b的至少四个侧面,且半导体层342b的两个侧面(或末端)分别耦接至源极/漏极结构320与源极/漏极结构322;且栅极堆叠310c与栅极堆叠310d可共同地包裹围绕半导体层342c的至少四个侧面,且半导体层342c的两个侧面(或末端)分别耦接至源极/漏极结构320与源极/漏极结构322。

253.参照图4,图4显示范例性的存储器装置400的透视图。根据一些实施例,存储器装置400可为抗熔丝存储器单元的一部分,该抗熔丝存储器单元包括一个编程晶体管以及两个读取晶体管,例如图2的存储器单元200。图4的透视图是为抗熔丝存储器单元的概观,因此,抗熔丝存储器单元的一些特征在图4中可能无法辨识。存储器装置400(或与存储器装置400相似的存储器装置)的更多详细特征,将在下文中参照图30以及图31的截面图进行图示及讨论。

254.如图4所示,存储器装置400包括编程晶体管402、第一读取晶体管404(亦称为读取晶体管404)、以及第二读取晶体管406(亦称为读取晶体管406)。在一些实施例中,编程晶体管402被配置为非gaa晶体管(例如:finfet),而第一及第二读取晶体管404及406的每一者被配置为gaa晶体管(例如:纳米片晶体管)。编程晶体管402以及第一读取晶体管404、第二读取晶体管406可被形成在半导体基板408上、各别的不同的主动区中。举例来说,编程晶体管402被形成在半导体基板408的第一主动区408a(亦称为主动区408a)上方;而第一读取晶体管404、第二读取晶体管406被形成在半导体基板408的第二主动区408b(亦称为主动区408b)上方,其中第一主动区408a与第二主动区408b通过隔离结构(未显示于图4中)横向地(例如:沿着x方向)彼此分隔。这种主动区有时被称为氧化扩散(od)区。

255.具体来说,编程晶体管402包括设置于第一主动区408a上方的栅极结构410;而第一读取晶体管404及第二读取晶体管406分别包括设置于第二主动区408b上方的栅极结构412及栅极结构414。彼此平行的栅极结构410、412与414可沿着横向方向(例如:y方向)指向以及伸长。在第一主动区408a中,编程晶体管402包括分别形成在栅极结构410的各别侧面上的源极/漏极结构416以及源极/漏极结构418。在第二主动区408b中,第一读取晶体管404包括分别形成在栅极结构412的各别侧面上的源极/漏极结构420以及源极/漏极结构422;而第二读取晶体管406包括分别形成在栅极结构414的各别侧面上的源极/漏极结构422以及源极/漏极结构424。在图4所示的实施例中,第一读取晶体管404与第二读取晶体管406可共享相同的源极/漏极结构422。不过,在本公开的范围内,同样包括了第一读取晶体管404与第二读取晶体管406并未共享相同的源极/漏极结构的实施例。

256.栅极结构410被形成为跨坐自基板408突出的结构432(下文中的鳍式或突出结构432),其中源极/漏极结构416与418分别耦接至突出结构432的两端,例如沿着x方向耦接至

突出结构432的两端。突出结构432可作为编程晶体管402的通道。栅极结构412被形成为包裹围绕多个纳米结构442a、442b及442c(例如:纳米片、纳米线、或其他具有纳米尺度的尺寸的半导体层,因此亦称为半导体层442a

‑

442c),且具有耦接至它们各自的末端的源极/漏极结构420与源极/漏极结构422,例如沿着x方向耦接至它们各自的末端。半导体层442a

‑

442c(有时可被称为半导体层442)可共同作为第一读取晶体管404的通道。栅极结构414被形成为包裹围绕多个其他纳米结构452a、452b及452c(例如:半导体层,因此亦称为半导体层452a

‑

452c),且具有耦接至它们各自的末端的源极/漏极结构422与源极/漏极结构424,例如沿着x方向耦接至它们各自的末端。半导体层452a

‑

452c(有时可被称为半导体层452)可共同作为第二读取晶体管406的通道。突出结构432以及半导体层442a

‑

442c还有半导体层452a

‑

452c可沿着横向方向(例如:x方向)指向与伸长,此横向方向与源极/漏极结构416

‑

424彼此对准的方向相同。如此一来,形成有源极/漏极结构416

‑

418与突出结构432的第一主动区408a,以及形成有源极/漏极结构420

‑

424与半导体层442a

‑

442c还有半导体层452a

‑

452c的第二主动区408b,尽管两者在横向上彼此分隔,但是它们可沿着横向方向(例如:x方向)彼此对准。

257.在一些实施例中,栅极结构412及414的每一者可包括多个栅极堆叠。栅极堆叠的每一者可包括一或多个栅极介电质以及一或多个栅极金属(为使说明清晰而未显示于图4中)。栅极堆叠中的两个被配置以共同包裹围绕一或多个半导体层中对应的一者。因为栅极结构412及414与参照图3所讨论的栅极结构310相似,因此将不再重复对栅极结构412及414的讨论。

258.图5、图6、图7及图8是根据一些实施例所示,用于制造抗熔丝单元的设计布局的各种范例。图5至图8的布局可各自用于制造具有一个编程晶体管以及一个读取晶体管的抗熔丝存储器单元,例如图1的存储器单元100。此外,在一些实施例中,编程晶体管可被形成为非gaa的晶体管,而读取晶体管可被形成为gaa晶体管。举例来说,非gaa的编程晶体管可为finfet,而gaa读取晶体管可为纳米片晶体管。然而,应理解的是,图5至图8的布局可被用于制造各种其他晶体管组合中的任何一种。举例来说,非gaa的编程晶体管可为平面晶体管,而gaa读取晶体管可为纳米线晶体管。在另一个范例中,非gaa的编程晶体管可为finfet,而gaa读取晶体管可为纳米线晶体管。在又一个范例中,非gaa的编程晶体管可为finfet,而gaa读取晶体管可为垂直(vertical)晶体管。

259.作为代表性范例,图5至图8的布局的每一者,被配置以制造类似于图3所示的存储器装置300的抗熔丝存储器装置,其中存储器装置300包括非gaa的编程晶体管以及gaa读取晶体管。因此,下文将结合图3提供对图5至图8的讨论。应理解的是,出于说明的目的,已经简化了图5至图8所示的布局。因此,每个布局可包括一或多个其他特征,且这些其他特征同样维持在本公开的范围内。

260.参照图5,图5根据一些实施例显示了布局500。布局500包括定义了抗熔丝存储器单元的边界的特征501(下文中称为单元边界501)。在单元边界501上,布局500包括各种特征,每个特征对应一或多个图案化制程(例如:微影(photolithography)制程)以形成物理性的装置特征。

261.举例来说,布局500包括主动特征502a及主动特征502b还有栅极特征504及栅极特征506。沿着x方向延伸的主动特征502a可被配置以定义第一主动区,例如图3的第一主动区

306a。沿着x方向延伸的主动特征502b可被配置以定义第二主动区,例如图3的第二主动区306b。在下文中,主动特征502a及502b有时可分别被称为主动区502a(306a)及502b(306b)。沿着y方向延伸的栅极特征504可被配置以形成第一栅极结构,例如图3的栅极结构308。沿着y方向延伸的栅极特征506可被配置以形成第二栅极结构,例如图3的栅极结构310。在下文中,栅极特征504及506有时可分别被称为栅极结构504(308)及506(310)。在一些实施例中,栅极结构504(308)的宽度w1(沿着x方向延伸),可宽于栅极结构506(310)的宽度w2(沿x着方向延伸),如图5所示。在一些其他实施例中,宽度w1可以等于宽度w2。

262.每个栅极特征可行进(travel)跨越对应的一个主动特征,以在栅极特征的侧面上形成一或多个次主动(sub

‑

active)特征,次主动特征可被配置以形成对应的源极/漏极结构。举例来说,在图5中,栅极特征504行进跨越主动特征502a,以形成次主动特征508及510,其中次主动特征508及510可被用于形成源极/漏极结构,例如图3的源极/漏极结构316及318。栅极特征506行进跨越主动特征502b,以形成次主动特征512及514,其中次主动特征508及510可被用于形成源极/漏极结构,例如图3的源极/漏极结构320及322。在下文中,次主动特征508、510、512以及514有时可分别被称为源极/漏极结构508(316)、510(318)、512(320)以及514(322)。

263.在一些实施例中,主动区502a(306a)的被栅极结构504(308)所覆盖的部分,被配置以形成非gaa晶体管的通道,例如图3的突出结构332。主动区502b(306b)的被栅极结构506(310)所覆盖的部分,被配置以形成gaa晶体管的通道,例如图3的半导体层342a

‑

342c。如此一来,可基于布局500的主动特征502a与栅极特征504,来形成非gaa的编程晶体管302(图3);以及可基于布局500的主动特征502b与栅极特征506,来形成gaa读取晶体管304(图3)。

264.在形成非gaa的编程晶体管302以及gaa读取晶体管304时,可形成多个互连结构以操作编程晶体管302以及读取晶体管304。举例来说,编程晶体管302的漏极(例如:源极/漏极结构510(318))与读取晶体管304的源极(例如:源极/漏极结构512(320))通过互连结构相互连接;编程晶体管302的栅极(例如:栅极结构504(308))以及读取晶体管304的栅极(例如:栅极结构506(310))可分别连接至作为wlp(例如:图1的编程字元线130)以及wlr(例如:图1的读取字元线132)的互连结构;而读取晶体管304的漏极(例如:源极/漏极结构514(322))可连接至作为bl(例如:图1的位元线134)的互连结构。

265.如图5的范例所示,布局500包括形成这些互连结构(例如:wlp、wlr、bl等)的多个特征,以及连接那些互连结构的附加互连结构。举例来说,布局500包括沿着y方向延伸的特征520、522、524以及526。特征520、522、524以及526被配置以形成互连结构,以分别连接至源极/漏极结构508(316)、源极/漏极结构510(318)、源极/漏极结构512(320)、以及源极/漏极结构514(322)。连接至源极/漏极结构的这些互连结构有时被称为md,其中md可被形成为狭缝(slot)或沟槽(trench)结构。因此,特征520、522、524以及526在下文中可分别被称为md 520、md 522、md 524以及md 526。

266.布局500进一步包括特征528、530以及532,这些特征被配置以形成互连结构,以分别连接至md 522、524以及526。这种互连结构有时被称为vd,其中vd可被形成为通孔(via)结构。因此,特征528、530以及532在下文中可分别被称为vd 528、vd 530以及vd 532。

267.布局500进一步包括特征534及536,两者均沿着x方向延伸。特征534被配置以形成

将编程晶体管302与读取晶体管304互连在一起的互连结构,特征534在下文中被称为互连结构534。举例来说,经由md 522、vd 528、互连结构534、vd 530以及md 524,编程晶体管302的源极/漏极结构510(318)可连接至读取晶体管304的源极/漏极结构512(320)。特征536被配置以形成作为bl的互连结构,特征536在下文中被称为位元线536。位元线536可经由vd 532与md 526连接至读取晶体管304的源极/漏极结构514(322)。

268.布局500进一步包括特征538及540,两者均沿着y方向延伸。特征538及540被配置以分别形成作为wlp及wlr的互连结构,特征538以及540在下文中被称为编程字元线(wlp)538以及读取字元线(wlr)540。编程字元线538可经由有时被称为vg(未图示)的一个互连结构连接至编程晶体管302的栅极结构504(308),而读取字元线540可经由另一个vg(未图示)连接至读取晶体管304的栅极结构506(310)。在一些实施例中,这些vg可被形成为通孔结构。

269.在一些实施例中,md 520

‑

526、vd 528

‑

532以及未图示的vg,可被设置于中段制程(middle

‑

end

‑

of

‑

line,meol)网状系统(network)中。互连结构534以及位元线536可被设置于后段制程(back

‑

end

‑

of

‑

line,beol)网状系统的第一金属化(metallization)层中。编程字元线538以及读取字元线540可被设置于后段制程(beol)网状系统的第二金属化层中。第二金属化层可被设置在第一金属化层上方,且第一金属化层可被设置在meol网状系统上方。

270.参照图6,图6根据一些实施例显示了布局600。布局600与布局500相似,不同之处在于布局600还包括了形成一或多个虚拟(dummy)栅极结构的特征。因此,在下文中图6的讨论将再次使用图5的一些参考符号。

271.如图所示,布局600进一步包括特征602及604,两者均沿着y方向延伸。特征602及604可被配置以形成虚拟栅极结构,特征602及604在下文中被称为虚拟栅极结构602及604。在一些实施例中,虚拟栅极结构602

‑

604可类似于图3的栅极结构308

‑

310(例如:沿着y方向延伸),但可能不会行进跨越任何主动区。因此,虚拟栅极结构602

‑

604将不会被用作主动栅极结构以电性控制完成的半导体装置(例如:图3的存储器装置300)中的电流。如图6所示,虚拟栅极结构602被沿着单元边界501的其中一侧设置。虚拟栅极结构604被设置在主动区502a(306a)与502b(306b)之间。

272.参照图7,图7根据一些实施例显示了布局700。布局700与布局600相似,不同之处在于布局700还包括了形成一或多个互连结构的特征。因此,在下文中图7的讨论将再次使用图6的一些参考符号。

273.图所示,布局700进一步包括特征702,特征702被配置以形成互连结构(例如:vd)。在下文中,特征702可被称为vd 702。与vd 528及530相似,vd 702配置以连接至对应的md(例如:md 520)。布局700进一步包括与特征534相似的特征704,不同之处在于除了连接到vd 528及530之外,特征704还被配置以形成连接到vd 702的互连结构。换句话说,特征704可进一步延伸跨越栅极结构504(308),例如沿着x方向延伸跨越栅极结构504(308)。在下文中,特征704有时可被称为互连结构704。通过形成互连结构704,连接至md 520的源极/漏极结构508(316)、连接至md 522的源极/漏极结构510(318)、以及连接至md 524的源极/漏极结构512(320),可被彼此互连。

274.参照图8,图8根据一些实施例显示了布局800。布局800与布局600相似,不同之处

在于布局800还包括了形成被对应的栅极结构所部分覆盖的主动区的特征。因此,在下文中图8的讨论将再次使用图6的一些参考符号。

275.如图所示,布局800包括特征802a,特征802a被配置以形成主动区。在下文中,特征802a有时可被称为主动区802a。主动区802a与图5至图7所示的主动区502a(306a)相似,不同之处在于主动区802a被栅极结构504(308)部分地覆盖。具体来说,在一些实施例中,主动区802a被栅极结构504(308)所覆盖的部分向主动区502b(306b)偏移。如此一来,当使用布局800来形成图3中的存储器装置300时,存储器装置300不具有源极/漏极结构316。进一步地,由主动区802a的被栅极结构504(308)所覆盖的部分形成的突出结构332,可具有同样由栅极结构504(308)所覆盖的额外侧壁。此侧壁应该已经耦接到源极/漏极结构316。仅具有耦接到其通道(例如:突出结构332)的一个源极/漏极结构(例如:源极/漏极结构318)的编程晶体管302,有时可被称为mos(或mosfet)电容器。

276.图9及图10是根据一些实施例所示,用于制造抗熔丝单元的设计布局的各种范例。图9及图10的布局可各自用于制造具有一个编程晶体管以及两个读取晶体管的抗熔丝存储器单元,例如图2的存储器单元200。此外,在一些实施例中,编程晶体管可被形成为非gaa的晶体管,而读取晶体管可被形成为gaa晶体管。举例来说,非gaa的编程晶体管可为finfet,而每个gaa读取晶体管可为纳米片晶体管。然而,应理解的是,图9及图10的布局可被用于制造各种其他晶体管组合中的任何一种,且这些实施例同样包括在本公开的范围中。

277.作为代表性范例,图9及图10的布局的每一者,被配置以制造类似于图4所示的存储器装置400的抗熔丝存储器装置,其中存储器装置400包括非gaa的编程晶体管以及两个gaa读取晶体管。因此,下文将结合图4提供对图9及图10的讨论。应理解的是,出于说明的目的,已经简化了图9及图10所示的布局。因此,每个布局可包括一或多个其他特征,且这些其他特征同样维持在本公开的范围内。

278.参照图9,图9根据一些实施例显示了布局900。布局900包括定义了抗熔丝存储器单元的边界的特征901(下文中称为单元边界901)。在单元边界901上方,布局900包括各种特征,每个特征对应一或多个图案化制程(例如:微影制程)以形成物理性的装置特征。

279.举例来说,布局900包括主动特征902a及主动特征902b,还包括栅极特征904、栅极特征906及栅极特征908。沿着x方向延伸的主动特征902a可被配置以定义第一主动区,例如图4的第一主动区408a。沿着x方向延伸的主动特征902b可被配置以定义第二主动区,例如图4的第二主动区408b。在下文中,主动特征902a以及902b有时可分别被称为主动区902a(408a)以及902b(408b)。沿着y方向延伸的栅极特征904可被配置以形成第一栅极结构,例如图4的栅极结构410。沿着y方向延伸的栅极特征906可被配置以形成第二栅极结构,例如图4的栅极结构412。沿着y方向延伸的栅极特征908可被配置以形成第三栅极结构,例如图4的栅极结构414。在下文中,栅极特征904、906及908有时可分别被称为栅极结构904(410)、906(412)及908(414)。在一些实施例中,栅极结构904(410)的宽度w3(沿着x方向延伸),可宽于栅极结构906(412)及908(414)的宽度w4(沿x着方向延伸),如图9所示。在一些其他实施例中,宽度w3可以等于宽度w4。

280.每个栅极特征可行进跨越对应的一个主动特征,以在栅极特征的侧面上形成一或多个次主动特征,次主动特征可被配置以形成对应的源极/漏极结构。举例来说,在图9中,栅极特征904行进跨越主动特征902a以形成次主动特征910及912,次主动特征910及912可

被用于形成源极/漏极结构,例如图4的源极/漏极结构416及418。栅极特征906及908分别行进跨越主动特征902b以形成次主动特征914、916及918,次主动特征914、916及918可分别被用于形成源极/漏极结构,例如图4的源极/漏极结构420、422及424。在下文中,次主动特征910、912、914、916以及918,有时可分别被称为源极/漏极结构910(416)、912(418)、914(420)、916(422)以及918(424)。

281.在一些实施例中,主动区902a(408a)的被栅极结构904(410)所覆盖的部分,被配置以形成非gaa晶体管的通道,例如图4的突出结构432。主动区902b(408b)的被栅极结构906(412)所覆盖的部分,被配置以形成第一gaa晶体管的通道,例如图4的半导体层442a

‑

442c。主动区902b(408b)的被栅极结构908(414)所覆盖的部分,被配置以形成第二gaa晶体管的通道,例如图4的半导体层452a

‑

452c。如此一来,可基于布局900的主动特征902a与栅极特征904来形成非gaa的编程晶体管402(图4);可基于布局900的主动特征902b与栅极特征906来形成gaa读取晶体管404(图4);以及可基于布局900的主动特征902b与栅极特征908来形成gaa读取晶体管406(图4)。

282.在形成非gaa的编程晶体管402以及gaa读取晶体管404

‑

406时,可形成多个互连结构以操作编程晶体管402以及读取晶体管404

‑

406。举例来说,编程晶体管402的漏极(例如:源极/漏极结构912(418))与读取晶体管404的源极(例如:源极/漏极结构914(420))通过互连结构相互连接;编程晶体管402的栅极(例如:栅极结构904(410))、读取晶体管404的栅极(例如:栅极结构906(412))、以及读取晶体管406的栅极(例如:栅极结构908(414))可分别连接至作为wlp(例如:图2的编程字元线240)、wlr1(例如:图2的第一读取字元线242)、以及wlr2(例如:图2的第二读取字元线244)的互连结构;而读取晶体管406的漏极(例如:源极/漏极结构918(424))可连接至作为bl(例如:图2的位元线250)的互连结构。

283.如图9的范例所示,布局900包括形成这些互连结构(例如:wlp、wlr1、wlr2、bl等)的多个特征,以及连接那些互连结构的附加互连结构。举例来说,布局900包括沿着y方向延伸的特征920、922、924、926以及928。特征920、922、924、926以及928被配置以形成互连结构,以分别连接至源极/漏极结构910(416)、源极/漏极结构912(418)、源极/漏极结构914(420)、源极/漏极结构916(422)、以及源极/漏极结构918(424)。连接至源极/漏极结构的这些互连结构有时被称为md。因此,特征920、922、924、926以及928在下文中可分别被称为md 920、md 922、md 924、md 926以及md 928。

284.布局900进一步包括特征930、932及934,这些特征被配置以形成互连结构,以分别连接至md 922、924及928。这种互连结构有时被称为vd。因此,特征930、932及934在下文中可分别被称为vd 930、vd 932及vd 934。

285.布局900进一步包括特征940及942,两者均沿着x方向延伸。特征940被配置以形成将编程晶体管402与读取晶体管404互连在一起的互连结构,特征940在下文中被称为互连结构940。举例来说,经由md 922、vd 930、互连结构940、vd 932以及md 924,编程晶体管402的源极/漏极结构912(418)可连接至读取晶体管404的源极/漏极结构914(420)。特征942被配置以形成作为bl的互连结构,特征942在下文中被称为位元线942。位元线942可经由vd 934与md 928连接至读取晶体管406的源极/漏极结构918(424)。

286.布局900进一步包括特征944、946及948,三者均沿着y方向延伸。特征944、946及948被配置以分别形成作为wlp、wlr1及wlr2的互连结构,特征944、946以及948在下文中分

别被称为编程字元线(wlp)944、第一读取字元线(wlr1)946、以及第二读取字元线(wlr2)948。编程字元线944可经由有时被称为vg(未图示)的一个互连结构,连接至编程晶体管402的栅极结构904(410),第一读取字元线946可经由另一个vg(未图示)连接至读取晶体管404的栅极结构906(412),而第二读取字元线948可经由又一个vg(未图示)连接至读取晶体管406的栅极结构908(414)。

287.在一些实施例中,md 920

‑

928、vd 930

‑

934以及未图示的vg,可被设置于中段制程(meol)网状系统中。互连结构940以及位元线942可被设置于后段制程(beol)网状系统的第一金属化层中。编程字元线538、第一读取字元线946、以及第二读取字元线948,可被设置在后段制程(beol)网状系统的第二金属化层中。第二金属化层可被设置在第一金属化层上方,且第一金属化层可被设置在meol网状系统上方。

288.照图10,图10根据一些实施例显示了布局1000。布局1000与布局900相似,不同之处在于布局1000还包括了形成一或多个虚拟栅极结构的特征。因此,在下文中图10的讨论将再次使用图9的一些参考符号。

289.如图所示,布局1000进一步包括特征1002及1004,两者均沿着y方向延伸。特征1002及1004可被配置以形成虚拟栅极结构,特征1002及1004在下文中被称为虚拟栅极结构1002及1004。在一些实施例中,虚拟栅极结构1002

‑

1004可类似于图4的栅极结构410

‑

414(例如:沿着y方向延伸),但可能不会行进跨越任何主动区。因此,虚拟栅极结构1002

‑

1004将不会被用作主动栅极结构以电性控制完成的半导体装置(例如:图4的存储器装置400)中的电流。如图10所示,虚拟栅极结构1002被沿着单元边界901的其中一侧设置。虚拟栅极结构1004被设置在主动区902a(408a)与902b(408b)之间。

290.图11根据本公开一或多个实施例,显示方法1100的流程图,方法1100在基板上定义第一主动区与第二主动区。第一主动区与第二主动区可通过至少一个隔离结构横向地彼此分隔。在一些实施例中,第一主动区可包括自基板突出的结构(例如:鳍式结构),而第二主动区可包括交替地堆叠在另一者顶部上的多个纳米结构(例如:纳米片、纳米线、或其他具有纳米尺度的尺寸的半导体层)。在定义了第一主动区与第二主动区之后,方法1100可由图18的方法1800接续,以分别在第一主动区及第二主动区中形成一或多个非gaa晶体管以及一或多个gaa晶体管,这将在下文中进行进一步的讨论。

291.方法1100的操作可与如图12、图13、图14、图15及图16所示的各个制造阶段的存储器装置1200的截面图相关。举例来说,存储器装置1200可类似于图3的存储器装置300或图4的存储器装置400。图12至图16的截面图,可为沿着图3及图4的线段a

‑

a’切割的截面图。在一些实施例中,存储器装置1200可被包括在微处理器、另一个存储器装置及/或其他集成电路(ic)中,或是另外耦接至微处理器、另一个存储器装置及/或其他集成电路(ic)。此外,图12至图16经过简化,以更好地理解本公开的概念。尽管图式显示了存储器装置1200,但应理解的是,ic可包括许多其他装置,例如电感器(inductor)、电阻器、电容器(capacitor)、晶体管等,为使说明清晰易懂,这些装置并未显示于图12至图16中。

292.简要地对方法1100进行概述,方法1100从操作1102开始,在操作1102中提供半导体基板。接着,方法1100进入操作1104,在操作1104中,半导体基板的第一区域被遮蔽(mask)。接着,方法1100进入操作1106,在操作1106中,半导体基板的第二区域被蚀刻以形成凹槽。接着,在操作1108中,多个第一半导体层与多个第二半导体层在凹槽中外延生长

(epitaxially grow),以交替地堆叠在另一者的顶部上。在第二区域中生长第一半导体层以及第二半导体层之后,方法1100进入操作1110,在操作1110中,定义了第一主动区及第二主动区。

293.对应图11的操作1102,图12是为处于各个制造阶段之一的存储器装置1200的截面图,其中存储器装置1200包括半导体基板1202。

294.半导体基板1202包括半导体材料基板,例如硅。替代性地,半导体基板1202可包括其他元素(elementary)半导体材料,例如锗。半导体基板1202亦可包括化合物(compound)半导体,例如碳化硅、砷化镓、砷化铟及磷化铟。半导体基板1202可包括合金(alloy)半导体,例如硅锗、碳化硅锗、磷砷化镓及磷化铟镓。在一个实施例中,半导体基板1202包括外延层。举例来说,半导体基板1202可具有覆盖体(bulk)半导体的外延层。此外,半导体基板1202可包括绝缘层上半导体(semiconductor

‑

on

‑

insulator,soi)结构。举例来说,半导体基板1202可包括埋入式氧化物(buried oxide,box)层,形成box层的制程例如布植氧分离(separation by implanted oxygen,simox)或其他合适的技术,例如晶圆接合(bonding)及研磨(grinding)。

295.对应图11的操作1104,图13是为处于各个制造阶段之一的存储器装置1200的截面图,其中存储器装置1200包括形成在半导体基板1202的顶部表面1203上的图案化遮罩1304。

296.图案化遮罩1304覆盖半导体基板1202的第一区域1202a(亦称为区域1202a),且图案化遮罩1304包括曝露半导体基板1202的第二区域1202b(亦称为区域1202b)的开口。在一个实施例中,第一区域1202a可包括被定义以用于形成一或多个非gaa晶体管(例如:图3的编程晶体管302、图4的编程晶体管402)的主动区,其中非gaa晶体管被配置为n型晶体管,而第二区域1202b可包括被定义以用于形成一或多个gaa晶体管(例如:图3的读取晶体管304、图4的第一读取晶体管404及第二读取晶体管406)的主动区,其中gaa晶体管被配置为n型晶体管。如此一来,第一区域1202a及第二区域1202b可被以p型掺杂物掺杂。应理解的是,存储器装置1200可替代地具有形成在第一区域1202a及第二区域1202b中的p型晶体管。

297.图案化遮罩1304可为诸如图案化光阻(resist)层的软遮罩,或是诸如介电材料层的硬遮罩,或者为其组合。在图13所示的实施例中,图案化遮罩1304包括设置在第一区域1202a上的硬遮罩1306,以及包括以微影制程形成在硬遮罩1306上的图案化光阻层1308。硬遮罩1306被蚀刻以将开口自图案化光阻层1308转移到硬遮罩1306。举例来说,硬遮罩1306包括氧化硅、氮化硅、氮氧化硅(silicon oxynitride)、碳化硅、碳氮化硅(silicon carbide nitride)、碳氮氧化硅(silicon carbide oxynitride)、其他半导体材料、及/或其他介电材料。在一个实施例中,硬遮罩1306的厚度处于约1纳米(nm)至约40nm的范围内。可通过下列方法形成硬遮罩1306:热氧化(thermal oxidation)、化学气相沉积(chemical vapor deposition,cvd)、原子层沉积(atomic layer deposition,ald)、或是任何其他适当的方法。范例性的微影制程可包括形成光阻层、通过微影曝光制程来曝光光阻、执行曝后烤(post

‑

exposure bake)制程、以及显影(develope)光阻层以形成图案化的光阻层。微影制程可替代性地以其他技术取代,例如电子束写入(e

‑

beam writing)、离子束写入(ion

‑

beam writing)、无光罩图案化(maskless patterning)、或是分子印刷(molecular printing)。在一些实施例中,图案化光阻层1308可在后续的蚀刻制程中直接被用作蚀刻遮

罩。在将硬遮罩1306图案化之后,可通过合适的制程移除图案化光阻层1308,例如湿式剥离(wet stripping)或是等离子体灰化(plasma ashing)。

298.对应图11的操作1106,图14是为处于各个制造阶段之一的存储器装置1200的截面图,其中存储器装置1200被蚀刻以形成凹槽1402。

299.第二区域1202b中的半导体基板1202被蚀刻,以形成凹槽1402。蚀刻制程经过设计,以使用硬遮罩1306作为蚀刻遮罩来选择性地移除第二区域1202b中的半导体基板1202。蚀刻制程可持续执行,以确保半导体基板1202的底部表面1205在凹槽1402中曝露。第一区域1202a中的半导体基板1202的侧壁1207也被曝露,并定义了凹槽1402的边缘。蚀刻制程可包括干式蚀刻、湿式蚀刻或其组合。图案化的硬遮罩1306在蚀刻中保护第一区域1202a之中的半导体基板1202。在各种范例中,蚀刻制程可包括使用合适的蚀刻剂的干式蚀刻,例如使用含氟(fluorine

‑

containing)的蚀刻气体或含氯(chlorine

‑

containing)的蚀刻气体,这些蚀刻气体例如cl2、ccl2f2、cf4、sf6、nf3、ch2f2或其他合适的蚀刻气体。在一些其他范例中,蚀刻制程可包括使用合适的蚀刻剂的湿式蚀刻,例如基于氢氟酸(hydrofluoric acid,hf)的溶液、基于硫酸(h2so4)的溶液、基于盐酸(hcl)的溶液、基于氢氧化铵(ammonium hydroxide,nh4oh)的溶液、其他合适的蚀刻溶液、或其组合。蚀刻制程可包括一个以上的步骤。

300.对应图11的操作1108,图15是为处于各个制造阶段之一的存储器装置1200的截面图,其中存储器装置1200包括多个第一半导体层1502(例如:第一半导体层1502a、1502b及1502c)以及多个第二半导体层1504(例如:第二半导体层1504a、1504b及1504c)。

301.在一些实施例中,第一半导体层1502a

‑

1502c以及第二半导体层1504a

‑

1504c于凹槽1402(图14)中被交替地设置在另一者的顶部上(例如:沿着z方向交替地设置),以形成堆叠。举例来说,其中一个第二半导体层(例如:第二半导体层1504a)被设置在其中一个第一半导体层(例如:第一半导体层1502a)上方,接着,另一个第一半导体层(例如:第一半导体层1502b)被设置在第二半导体层1504a上方,依此类推。

302.在各种实施例中,堆叠可包括任何数量的交替设置的第一半导体层1502与第二半导体层1504。第一半导体层1502与第二半导体层1504可具有不同的厚度。第一半导体层1502中的一层与另一层之间可具有不同的厚度。第二半导体层1504中的一层与另一层之间可具有不同的厚度。第一半导体层1502与第二半导体层1504中的每一者的厚度,可处于自数纳米到数十纳米的范围内。堆叠中的第一层可厚于其他的第一半导体层1502及第二半导体层1504。举例来说,第一半导体层1502a可厚于第一半导体层1502b

‑

1502c以及第二半导体层1504a

‑

1504c。在一个实施例中,第一半导体层1502a

‑

1502c的每一者的厚度,处于约5nm至约20nm的范围内,而第二半导体层1504a

‑

1504c的每一者的厚度,处于约5nm至约20nm的范围内。

303.第一半导体层1502与第二半导体层1504两者可具有不同的组成(composition)。在各种实施例中,第一半导体层1502与第二半导体层1504两者所具有的组成,在层与层之间提供了不同的氧化速率及/或不同的蚀刻选择性(selectivity)。在一个实施例中,第一半导体层1502包括硅锗(si1‑

x

ge

x

),而第二半导体层1504包括硅(si)。在一个实施例中,第二半导体层1504的每一者为硅,且可以是未掺杂或是实质上不含掺杂物的(即:所具有的外质(extrinsic)掺杂物浓度自约0cm

‑3至约1x10

17

cm

‑3),其中作为范例,当形成第二半导体层

1504(例如:硅)时,并未进行有意的(intentional)掺杂。替代性地,第二半导体层1504可被有意地掺杂。举例来说,第二半导体层1504的每一者可为硅,且被以诸如硼(b)、铝(al)、铟(in)及镓(ga)的p型掺杂物掺杂,以形成p型通道,或者是被以诸如磷(p)、砷(as)、锑(sb)的n型掺杂物掺杂,以形成n型通道。在一些实施例中,第一半导体层1502的每一者为si1‑

x

ge

x

,其包括莫耳比(molar ratio)小于50%(x<0.5)的ge。举例来说,以莫耳比来看,ge可占si1‑

x

ge

x

组成的第一半导体层1502的约15%至35%。此外,对于第一半导体层1502,在它们之间可包括不同的组成,而对于第二半导体层1504,在它们之间亦可包括不同的组成。

304.在各种实施例中,第一半导体层1502或是第二半导体层1504可包括其他材料,举例来说,诸如碳化硅、砷化镓、磷化镓、磷化铟、砷化铟及/或锑化铟的化合物半导体,以及诸如gaasp、alinas、algaas、ingaas、gainp、及/或gainasp的合金半导体、或其组合。可基于提供不同的氧化速率及/或蚀刻选择性来选择第一半导体层1502及第二半导体层1504的材料。如上所述,第一半导体层1502及第二半导体层1504可以是经掺杂的或是未掺杂的。

305.在各种实施例中,第一半导体层1502及第二半导体层1504自第二区域1202b中的底部表面1205外延生长。举例来说,第一半导体层1502及第二半导体层1504中的每一者,可通过下列制程进行生长:分子束外延(molecular beam epitaxy,mbe)制程、诸如金属有机化学气相沉积(metal organic cvd,mocvd)制程的化学气相沉积(cvd)制程、及/或其他合适的外延生长制程。在外延生长期间,半导体基板1202的晶体结构(crystal structure)向上(例如:沿着z方向)延伸,作为结果,第一半导体层1502及第二半导体层1504具有与半导体基板1202相同的晶体方向(crystal orientation)。

306.在第一区域1202a中,硬遮罩1306(图14)可作为半导体基板1202的顶部表面1203上的覆盖层,以阻止外延生长发生在第一区域1202a中。尽管并未图示,但可选择用的介电层可被形成为沿着侧壁1207延伸。如此一来,此介电层可以覆盖侧壁1207,进而阻止自侧壁1207开始的外延生长,使得在从侧壁1207进入第二区域1202b的横向方向上不会发生外延生长。因此,在一些实施例中,第一半导体层1502及第二半导体层1504的外延生长被限制在第二区域1202b中。在一些实施例中,在形成所需数量的第一半导体层1502及第二半导体层1504(例如:第三个第二半导体层1504c)之后,可执行抛光(polishing)制程(例如:化学机械研磨(chemical mechanical polishing,cmp)制程),以使第一区域1202a与第二区域1202b齐平(level)。

307.对应图11的操作1110,图16是为处于各个制造阶段之一的存储器装置1200的截面图,其中存储器装置1200包括第一主动结构1602a以及第二主动结构1602b。

308.第一主动结构1602a可被形成在并未形成交替堆叠的半导体层(例如:第一半导体层1502与第二半导体层1504)的第一区域1202a中,而第二主动结构1602b被形成在形成有交替堆叠的半导体层(例如:第一半导体层1502与第二半导体层1504)的第二区域1202b中。如同将在下文中讨论的,第一主动结构1602a的对应区域(在下文中被称为“第一主动区1603a”)被定义为将形成一或多个非gaa晶体管(例如:图3的编程晶体管302、图4的编程晶体管402)的区域或覆盖区(footprint),而第二主动结构1602b的对应区域(在下文中被称为“第二主动区1603b”)则被定义为将形成一或多个gaa晶体管(例如:图3的读取晶体管304、图4的第一读取晶体管404及第二读取晶体管406)的区域或覆盖区。

309.如图16所示,第一主动结构1602a被形成为自半导体基板1202突出的鳍式结构,而

第二主动结构1602b被形成为设置于半导体基板1202上方的交替半导体层行(column)。在一些实施例中,第一主动结构1602a可为自半导体基板1202延伸的整体连续的结构。第一主动结构1602a可沿着横向方向(例如:x方向)伸长。第二主动结构1602b包括彼此交错的半导体层1610与半导体层1620的堆叠。

310.在第一主动结构1602a及第二主动结构1602b的形成中,图案化遮罩1625a及图案化遮罩1625b(以虚线显示)可分别被形成在半导体基板1202上方的第一区域1202a及第二区域1202b中。图案化遮罩1625a及图案化遮罩1625b可定义第一主动结构1602a及第二主动结构1602b的覆盖区(例如:通过遮蔽将要形成的第一主动结构1602a或第二主动结构1602b),且一或多个蚀刻制程可被分别施加到第一区域1202a中的半导体基板1202以及第二区域1202b中的第一半导体层1502与第二半导体层1504,以形成第一主动结构1602a及第二主动结构1602b。因此,可定义第一主动区1603a及第二主动区1603b。在一些实施例中,半导体层1610a、1620a、1610b、1620b、1610c以及1620c,可分别为第一半导体层1502a、第二半导体层1504a、第一半导体层1502b、第二半导体层1504b、第一半导体层1502c以及第二半导体层1504c的剩余部分。在形成第一主动结构1602a及第二主动结构1602b之后,图案化遮罩1625a及图案化遮罩1625b可被移除。

311.一或多个蚀刻制程可包括一或多个干式蚀刻制程、湿式蚀刻制程、以及其他合适的蚀刻技术。举例来说,干式蚀刻制程可实施含氧气体、含氟气体(例如:cf4、sf6、ch2f2、chf3及/或c2f6)、含氯气体(例如:cl2、chcl2、ccl4及/或bcl3)、含溴(bromine

‑

containing)气体(例如:hbr及/或chbr3)、含碘(iodine

‑

containing)气体、其他合适的气体及/或等离子体、及/或其组合。举例来说,湿式蚀刻制程可包括在下列溶液中进行蚀刻:稀氢氟酸(diluted hydrofluoric acid,dhf)、氢氧化钾(potassium hydroxide,koh)溶液、氨(ammonia)、含氢氟酸(hf)溶液、硝酸(nitric acid,hno3)、及/或乙酸(acetic acid,ch3cooh)、或是其他合适的湿式蚀刻剂。

312.在一些实施例中,可根据布局的各个主动特征来形成用于形成第一主动结构1602a及第二主动结构1602b的图案化遮罩1625a及图案化遮罩1625b。在各种实施例中,图5至图10的布局500

‑

1000中的任何一者,均可用于形成第一主动结构1602a及第二主动结构1602b,以及形成对应的第一主动区1603a及第二主动区1603b。举例来说,在半导体基板上方的对应区域中生长第一半导体层1502及第二半导体层1504(图15)之后,如图5至图8所示的主动特征502a及502b可分别被用于形成第一主动结构1602a及第二主动结构1602b,并因此分别定义第一主动区1603a及第二主动区1603b。在另一个范例中,在半导体基板上方的对应区域中生长第一半导体层1502及第二半导体层1504(图15)之后,如图9至图10所示的主动特征902a及主动特征902b可分别被用于形成第一主动结构1602a及第二主动结构1602b,并因此分别定义第一主动区1603a及第二主动区1603b。

313.在形成第一主动结构1602a及第二主动结构1602b之后,一或多个隔离结构1630可被形成于第一主动结构1602a与第二主动结构1602b之间。由绝缘材料所形成的隔离结构1630,可将相邻的主动结构彼此电性隔离。绝缘材料可为诸如氧化硅的氧化物、氮化物等、或其组合,且可由高密度等离子体化学气相沉积(high density plasma chemical vapor deposition,hdp

‑

cvd)、流动式化学气相沉积(flowable cvd,fcvd)(例如:在远程等离子体系统中进行基于cvd的材料沉积,并进行后硬化(post curing)以使其转变为另一种材料,

例如氧化物)等、或其组合来形成。亦可使用其他绝缘材料及/或其他形成制程。在一个范例中,绝缘材料为通过fcvd制程形成的氧化硅。一旦绝缘材料被形成,便可执行退火制程(anneal process)。诸如化学机械研磨(cmp)制程的平坦化制程,可移除任何多余的绝缘材料,并形成共面(coplanar)的绝缘材料的顶部表面与图案化遮罩1625a及1625b的顶部表面(未图示)。亦可通过平坦化制程移除图案化遮罩1625a及1625b。

314.接着,绝缘材料被掘入(recess)以形成如图16所示的隔离结构1630,隔离结构1630有时被称为浅沟槽隔离(shallow trench isolation,sti)。隔离结构1630被掘入,使得第一主动结构1602a及第二主动结构1602b自相邻的隔离结构1630之间突出。各别隔离结构(sti)1630的顶部表面可具有平坦表面(如图所示)、凸出表面、凹陷表面(例如:碟压(dishing))、或其组合。隔离结构1630的顶部表面可通过适当的蚀刻而被形成为平坦的、凸起的及/或凹陷的。可使用可接受的蚀刻制程来掘入隔离结构1630,例如使用对隔离结构1630的材料具有选择性的蚀刻制程。举例来说,可执行干式蚀刻或使用稀氢氟酸(dhf)的湿式蚀刻制程,以掘入隔离结构1630。

315.图17是根据本公开一或多个实施例所示的流程图,显示用于定义第一主动区1603a以及第二主动区1603b的另一种方法1700。与图11的方法1100相似,方法1700可由图18的方法1800接续,以分别在第一主动区及第二主动区中形成一或多个非gaa晶体管及一或多个gaa晶体管,这将在下文中进行进一步的讨论。方法1700的操作将在下文中参照图12至图16的截面图简洁地进行讨论。

316.举例来说,方法1700从操作1702开始,在操作1702中提供半导体基板1202(图12)。接着,不同于方法1100(例如:不同于在凹槽1402中生长第一半导体层1502以及第二半导体层1504),方法1700进入操作1704,在操作1704中,第一半导体层1502以及第二半导体层1504在半导体基板1202上方被外延生长。第一半导体层1502与第二半导体层1504交替地堆叠在另一者的顶部上。接着,方法1700进入操作1706,在操作1706中,第二区域1202b被遮蔽,紧接着在操作1708中,第一区域1202a被蚀刻以形成凹槽。接着,在操作1710中,与第二半导体层相似的第三半导体层被外延生长于第一区域的凹槽中。在第一区域中生长第三半导体层之后,与方法1100相似,方法1700进入操作1712,在操作1712中,定义了第一主动结构1602a及第二主动结构1602b。

317.如上所述,在方法1100(图11)以及方法1700(图17)的任一者之后,可接续方法1800(图18)。在各种实施例中,方法1800的操作可分别在第一主动区1603a以及第二主动区1603b中形成一或多个非gaa晶体管以及一或多个gaa晶体管。

318.参照图18,图18根据本公开一或多个实施例绘制了方法1800的流程图,方法1800用于分别在第一主动区1603a以及第二主动区1603b中形成至少一个非gaa晶体管以及至少一个gaa晶体管。方法1800的操作可与如图19a、图19b、图19c、图20、图21、图22、图23、图24、图25、图26、图27a、图27b、图27c及图28所示的各个制造阶段的存储器装置1200的截面图相关。图19a、图20至图27a以及图28的截面图可沿着图3及图4所示的线段a

‑

a’截取;图19b以及图27b的截面图可沿着图3及图4所示的线段b

‑

b’截取;而图19c以及图27c的截面图可沿着图3及图4所示的线段c

‑

c’截取。图19a至图28经过简化,以更好地理解本公开的概念,且因此,应理解的是,存储器装置1200可包括许多其他装置,例如电感器、电阻器、电容器、晶体管等,为使说明清晰易懂,这些装置并未显示于图19a至图28中。

319.简要地对方法1800进行概述,方法1800从操作1802开始,在操作1802中形成虚拟栅极结构。接着,方法1800进入操作1804,在操作1804中,移除第二主动结构的末端部分。接着,方法1800继续进行到操作1806,在操作1806中,在第二主动结构中形成内部间隔物。接着,方法1800继续进行到操作1808,在操作1808中,形成耦接至第二主动结构的源极/漏极结构。接着,方法1800继续进行到操作1810,在操作1810中,移除第一主动结构的末端部分。接着,方法1800继续进行到操作1812,在操作1812中,形成耦接至第一主动结构的源极/漏极结构。接着,方法1800继续进行到操作1814,在操作1814中,形成层间介电质。接着,方法1800继续进行到操作1816,在操作1816中,首先移除虚拟栅极结构,接着自第二主动结构移除第一半导体层。接着,方法1800继续进行到操作1818,在操作1818中,形成主动栅极结构。接着,方法1800继续进行到操作1820,在操作1820中,形成互连结构。

320.对应图18的操作1802,图19a是为处于各个制造阶段之一的存储器装置1200的沿着线段a

‑

a’截取的截面图,其中存储器装置1200包括第一虚拟栅极结构1902(亦称为虚拟栅极结构1902)以及第二虚拟栅极结构1912(亦称为虚拟栅极结构1912)。为使说明清晰易懂,图19b显示存储器装置1200沿着线段b

‑

b’(例如:如图3至图4所示)截取的对应截面图,而图19c则显示存储器装置1200沿着线段c

‑

c’(例如:如图3至图4所示)截取的对应截面图。

321.每个虚拟栅极结构包括虚拟栅极介电质、虚拟栅极以及硬遮罩。举例来说,在图19a及图19b中,第一虚拟栅极结构1902包括形成在第一主动结构1602a上方的虚拟栅极介电质1904、形成在虚拟栅极介电质1904上方的虚拟栅极1906、以及形成在虚拟栅极1906上方的硬遮罩1908;而在图19a及图19c中,第二虚拟栅极结构1912包括形成在第二主动结构1602b上方的虚拟栅极介电质1914、形成在虚拟栅极介电质1914上方的虚拟栅极1916、以及形成在虚拟栅极1916上方的硬遮罩1918。

322.如图19a至图19c所示,虚拟栅极结构1902被形成在第一主动结构1602a的顶部表面上,并围绕第一主动结构1602a的侧壁;而虚拟栅极结构1912被形成在第二主动结构1602b的顶部表面上,并围绕第二主动结构1602b的侧壁。为了形成虚拟栅极结构1902(虚拟栅极结构1902的形成作为代表性的范例),介电层被形成在第一主动结构1602a上方。举例来说,介电层可为氧化硅、氮化硅、其多层等,且介电层可被沉积或热生长。栅极层被形成在介电层上方,而遮罩层被形成在栅极层上方。栅极层可被沉积在介电层上方,并接着被平坦化,例如通过cmp平坦化。遮罩层可被沉积在栅极层上方。在形成这些薄层(例如:介电层、栅极层以及遮罩层)之后,可使用可接受的微影与蚀刻技术来图案化遮罩层,以形成硬遮罩1908。然后可通过可接受的蚀刻技术,将硬遮罩1908的图案转移到栅极层及介电层,以分别形成虚拟栅极1906以及下方的虚拟栅极介电质1904。使用如上所述的相似操作,可同时或另外形成虚拟栅极结构1912。

323.在形成第一虚拟栅极结构1902及第二虚拟栅极结构1912之后,栅极间隔物1910以及栅极间隔物1920可被分别形成为沿着第一虚拟栅极结构1902以及第二虚拟栅极结构1912的各自的侧壁延伸,如图19a所示。可使用间隔物下拉(pull down)形成制程来形成栅极间隔物1910及1920。亦可通过顺应性(conformal)的沉积介电材料(例如:氧化硅、氮化硅、氮氧化硅、sibcn、siocn、sioc、或这些材料的任何合适组合)以及接着执行的指向性蚀刻(例如:反应式离子蚀刻(rie)),来形成栅极间隔物1910以及1920。

324.在一些实施例中,可根据布局500

‑

1000(图5至图10)的每一者的栅极特征,来形成

虚拟栅极结构可被设置在存储器装置1200的非gaa晶体管与两个gaa晶体管之间(类似于图4的存储器装置400,不同之处在于包括至少一个额外的虚拟栅极结构),这将进一步显示于图31中。

328.尽管图19a至图19c所示的虚拟栅极结构1902跨坐第一主动结构1602a,其中第一主动结构1602a的侧壁沿着x方向曝露,但应理解的是,存储器装置1200可包括沿着x方向进一步延伸至其中一个侧壁的虚拟栅极结构,且这些实施例均维持在本公开的范围内。举例来说,当使用图8的布局800来形成虚拟栅极结构时,因为栅极特征504仅行进跨越主动特征802a(用于形成第一主动结构1602a),因此虚拟栅极结构1902除了跨坐第一主动结构1602a的顶部表面及侧壁(沿着y方向)之外,还可以沿着其中一个侧壁延伸(沿着x方向),其中该侧壁是面对第二主动结构1602b的一侧的相对侧。在各种实施例中,虚拟栅极结构1902及1912可随后被各自的主动栅极结构所取代,其中栅极间隔物1910及1920基本上保持完整。因此,当完成存储器装置1200时,这些主动栅极结构可分别被用作存储器装置1200的非gaa晶体管与gaa晶体管的栅极。具体来说,非gaa晶体管可能仅具有一个源极/漏极结构,其中对应的主动栅极结构沿着一个侧壁延伸(类似于图3的存储器装置300,不同之处在于并未包括源极/漏极结构316),而该源极/漏极结构形成在与该侧壁相对的另一个侧壁处,这将进一步显示图32中。在一些实施例中,这种仅具有一个源极/漏极结构的晶体管,有时被称为mos电容器。

329.在下文中,用于制造存储器装置1200的方法1800的讨论,将聚焦在图5的布局500。换句话说,在图20至图28中的存储器装置1200的截面图,将不会显示第一主动结构1602a与第二主动结构1602b之间额外的虚拟栅极结构、形成于第二主动结构1602b上方的第三主动/虚拟栅极结构、或是mos电容器。这些存储器装置1200的其他实施例的截面图,可基于图6至图10所示的布局来形成,且将分别显示于图29至图32中。

330.对应图18的操作1804,图20是为处于各个制造阶段之一的存储器装置1200的沿着线段a

‑

a’(例如:如图3至图4所示)截取的截面图,其中第二主动结构1602b的末端部分被移除。

331.在一些实施例中,在移除第二主动结构1602b的末端部分时,第一主动结构1602a(或第一主动区1603a)可被阻挡遮罩2001所覆盖。阻挡遮罩2001被形成以覆盖第一主动结构1602a,同时保持第二主动结构1602b的曝露。阻挡遮罩2001可被形成为具有足够大的厚度(或高度),使得第一主动结构1602a的顶部表面与侧壁被完全覆盖,如图20所示。阻挡遮罩2001的形成,可允许一或多个制程仅被执行于第二主动结构1602b,这将在下文中进行讨论。阻挡遮罩2001可由相对于蚀刻剂(可蚀刻sige)具有抗性的材料所形成,例如氧化硅、氮化硅、氮氧化硅、sibcn、siocn、sioc、或这些材料的任何合适的组合。

332.在以阻挡遮罩2001覆盖第一主动结构1602a(或第一主动区1603a)之后,虚拟栅极结构1912与栅极间隔物1920可一起被用作遮罩,以蚀刻第二主动结构1602b的末端部分,作为结果,第二主动区1603b中的第二主动结构1602b具有半导体层1610与1620的剩余部分的交替堆叠。举例来说,如图20所示,第二主动结构1602b的半导体层2010a、2020a、2010b、2020b、2010c以及2020c,分别为半导体层1610a、1620a、1610b、1620b、1610c以及1620c的剩余部分。半导体层2010a

‑

2010c以及2020a

‑

2020c可分别被统称为半导体层2010以及2020。在一些实施例中,半导体层2010a

‑

2010c以及半导体层2020a

‑

2020c有时可被称为纳米结构

2010a

‑

2010c以及纳米结构2020a

‑

2020c。

333.对应图18的操作1806,图21是为处于各个制造阶段之一的存储器装置1200的沿着线段a

‑

a’(例如:如图3至图4所示)截取的截面图,其中存储器装置1200包括内部间隔物2102,内部间隔物2102被沿着每个半导体层2010a

‑

2010c的各自的被蚀刻的末端形成。

334.为了形成内部间隔物2102,可首先移除每个半导体层2010a

‑

2010c的各自的末端部分。在移除半导体层2010a

‑

2010c的各自的末端部分期间,第一主动结构1602a可维持被阻挡遮罩2001覆盖的状态,这允许第一主动结构1602a保持完整。可使用“回拉(pull

‑

back)”制程来移除(例如:蚀刻)半导体层2010a

‑

2010c的末端部分,以将半导体层2010a

‑

2010c回拉到初始回拉距离,使得半导体层2010a

‑

2010c的末端部分终止于栅极间隔物1920的下方(例如:与栅极间隔物1920对齐)。尽管在图21所示的实施例中,每个半导体层2010a

‑

2010c的被蚀刻的末端约略与栅极间隔物1920的侧壁对准,但应理解的是,回拉距离(即:每个半导体层2010a

‑

2010c被蚀刻或回拉的程度)可被任意地增加或减少。在半导体层2020a

‑

2020c包括si而半导体层2010a

‑

2010c包括si1‑

x

ge

x

的范例中,回拉制程可包括氯化氢(hcl)气体等向性(isotropic)蚀刻制程,其在蚀刻sige的同时不会伤害si。如此一来,在此制程期间,半导体层2020a

‑

2020c得以保持完整。

335.接着,可沿着每个半导体层2010a

‑

2010c的被蚀刻的末端形成内部间隔物2102,其中第一主动结构1602a被阻挡遮罩2001所覆盖。在一些实施例中,内部间隔物2102可通过化学气相沉积(cvd),或是通过氮化物的单层掺杂(mld)并接续间隔物rie来顺应性地形成。可使用例如顺应性的沉积制程来沉积内部间隔物2102,并接着执行等向性或非等向性(anisotropic)回蚀刻(etch back),以移除第二主动结构1602b的侧壁上以及半导体基板1202的表面上的过量间隔物材料。可由与栅极间隔物1920相同或不同的材料(例如:氮化硅)来形成内部间隔物2102的材料。举例来说,内部间隔物2102可由下列材料形成:氮化硅、硅硼碳氮化物(silicoboron carbonitride)、碳氮化硅、碳氮氧化硅(silicon carbon oxynitride)、或任何其他类型的适合形成晶体管的绝缘栅极侧壁间隔物的介电材料(例如:所具有的介电常数k小于约5的介电材料)。

336.对应图18的操作1808,图22是为处于各个制造阶段之一的存储器装置1200的沿着线段a

‑

a’(例如:如图3至图4所示)截取的截面图,其中存储器装置1200包括第二主动区1603b中的源极/漏极结构2202及2204。源极/漏极结构2202及2204耦接至第二主动结构1602b的对应的末端。

337.在形成源极/漏极结构2202及2204的期间,第一主动结构1602a可保持被阻挡遮罩2001所覆盖的状态。可使用外延层生长制程在每个半导体层2020a

‑

2020c的曝露末端上形成源极/漏极结构2202及2204。在一些实施例中,源极/漏极结构2202及2204的底部表面,可与隔离结构1630的顶部表面齐平,如图22的实线所示。因此,源极/漏极结构2202及2204可具有高度h1。在一些其他实施例中,源极/漏极结构2202及2204的底部表面,可低于隔离结构1630的顶部表面,如图22的虚线所示。因此,源极/漏极结构2202及2204可具有高度h2。

338.源极/漏极结构2202及2204电性耦接至半导体层2020a

‑

2020c。在各个实施例中,半导体层2020a

‑

2020c可共同作为gaa晶体管(在下文中称为gaa晶体管2210)的通道。应注意的是,在一些实施例中,在制造的这个阶段,gaa晶体管2210尚未完成。再次参考图3,gaa晶体管2210在完成时可类似于作为gaa晶体管的读取晶体管304。因此,半导体层2020a

‑

2020c可分别对应半导体层342a

‑

342c;而源极/漏极结构2202及2204可分别对应源极/漏极结构320及322。

339.可施加原位掺杂(in

‑

situ doping,isd)以形成掺杂的源极/漏极结构2202及2204,进而创造用于gaa晶体管2210的接面(junction)。n型fet与p型fet是通过将不同类型的掺杂物布植(implant)到装置的被选定的区域(例如:源极/漏极结构2202及2204)以形成接面而形成的。n型装置可通过布植砷(as)或磷(p)来形成,而p型装置可通过布植硼(b)来形成。

340.对应图18的操作1810,图23是为处于各个制造阶段之一的存储器装置1200的沿着线段a

‑

a’(例如:如图3至图4所示)截取的截面图,其中第一主动结构1602a的末端部分(沿着x方向)被移除。

341.在一些实施例中,在移除第一主动结构1602a的末端部分时,部分形成的gaa晶体管2210可被阻挡遮罩2301所覆盖。阻挡遮罩2301被形成以覆盖部分形成的gaa晶体管2210,同时维持第一主动结构1602a是曝露的。阻挡遮罩2301可被形成为具有足够大的厚度(或高度),使得部分形成的gaa晶体管2210被完全覆盖,如图23所示。阻挡遮罩2301的形成,可允许一或多个制程仅被执行于第一主动结构1602a,这将在下文讨论。阻挡遮罩2301可由相对于蚀刻剂(可蚀刻sige)具有抗性的材料所形成,例如氧化硅、氮化硅、氮氧化硅、sibcn、siocn、sioc、或这些材料的任何合适的组合。

342.在以阻挡遮罩2301覆盖部分形成的gaa晶体管2210之后,虚拟栅极结构1902与栅极间隔物1910可一起被用作遮罩,以蚀刻第一主动结构1602a的末端部分,作为结果,第一主动结构1602a所具有的沿着x方向的侧壁(或末端)被曝露以形成对应的源极/漏极结构。

343.对应图18的操作1812,图24是为处于各个制造阶段之一的存储器装置1200的沿着线段a

‑

a’(例如:如图3至图4所示)截取的截面图,其中存储器装置1200包括第一主动区1603a中的源极/漏极结构2402及2404。源极/漏极结构2402及2404耦接至第一主动结构1602a的对应的末端。

344.在形成源极/漏极结构2402及2404的期间,部分形成的gaa晶体管2210可维持被阻挡遮罩2301覆盖的状态。可使用外延层生长制程在第一主动结构1602a的曝露末端上形成源极/漏极结构2402及2404。在一些实施例中,源极/漏极结构2402及2404的底部表面,可与隔离结构1630的顶部表面齐平,如图24所示。。因此,源极/漏极结构2402及2404可具有的高度h3,其中高度h3约略等于高度h1但低于高度h2(图22)。

345.源极/漏极结构2402及2404电性耦接至第一主动结构1602a。在各种实施例中,第一主动结构1602a可作为非gaa晶体管(下文中称为非gaa晶体管2410)的通道。应注意的是,在一些实施例中,在制造的这个阶段,非gaa晶体管2410尚未完成。再次参照图3,在完成之后,非gaa晶体管2410可类似于作为非gaa晶体管的编程晶体管302。因此,第一主动结构1602a可对应突出结构332;而源极/漏极结构2402及2404可分别对应源极/漏极结构316及318。

346.可施加原位掺杂(isd)以形成被掺杂的源极/漏极结构2402及2404,进而创造用于非gaa晶体管2410的接面。n型fet与p型fet是通过将不同类型的掺杂物布植到装置的被选定的区域(例如:源极/漏极结构2402及2404)以形成接面而形成的。n型装置可通过布植砷(as)或磷(p)来形成,而p型装置可通过布植硼(b)来形成。

347.对应图18的操作1814,图25是为处于各个制造阶段之一的存储器装置1200的沿着线段a

‑

a’(例如:如图3至图4所示)截取的截面图,其中存储器装置1200包括层间介电质(ild)2500。层间介电质2500有时可被称为层间介电质0(ild0)。可通过下列方式形成层间介电质2500:在部分形成的gaa晶体管2210以及非gaa晶体管2410上方大量(in bulk)沉积介电材料,接着将整体氧化物抛光(例如:使用cmp)回到与虚拟栅极1906及1916齐平,这使得硬遮罩1908及1918被移除。如此一来,虚拟栅极1906及1916可被曝露。层间介电质2500的介电材料包括氧化硅、磷硅酸盐玻璃(phosphosilicate glass,psg)、硼硅酸盐玻璃(borosilicate glass,bsg)、硼掺杂的磷硅酸盐玻璃(boron

‑

doped phosphosilicate glass,bpsg)、未掺杂的硅酸盐玻璃(undoped silicate glass,usg)、及其组合。

348.对应图18的操作1816,图26是为处于各个制造阶段之一的存储器装置1200的沿着线段a

‑

a’(例如:如图3至图4所示)截取的截面图,其中虚拟栅极结构1902及1912首先被移除,接着半导体层2010a

‑

2010c也被移除。

349.在形成层间介电质2500并曝露虚拟栅极1906及1916(图25)之后,虚拟栅极结构1902及1912被移除。可通过已知的蚀刻制程,例如rie或化学氧化移除(chemical oxide removal,cor),来移除虚拟栅极结构1902及1912。在移除虚拟栅极结构1902之后,第一主动结构1602a的顶部表面被曝露。尽管并未显示于图26的截面图中,但应理解的是,除了顶部表面之外,第一主动结构1602a的侧壁(面向y方向)亦可被曝露。相似地,在移除虚拟栅极结构1912之后,半导体层2020c的顶部表面被曝露。尽管并未显示于图26的截面图中,但应理解的是,除了顶部表面之外,半导体层2010a

‑

2010c以及2020a

‑

2020c的每一者的侧壁(面向y方向)亦可被曝露。接着,通过施加选择性蚀刻(例如:盐酸(hcl)来移除半导体层2010a

‑

2010c。在移除半导体层2010a

‑

2010c之后,半导体层2020a

‑

2020c的每一者各自的底部表面以及顶部表面可被曝露。

350.对应图18的操作1818,图27a是为处于各个制造阶段之一的存储器装置1200的沿着线段a

‑

a’(例如:如图3至图4所示)截取的截面图,其中存储器装置1200包括第一主动栅极结构2702(亦称为主动栅极结构2702)以及第二主动栅极结构2712(亦称为主动栅极结构2712)。为使说明清晰易懂,图27b显示了存储器装置1200的沿着线段b

‑

b’(例如:如图3至图4所示)截取的截面图;而图27c显示了存储器装置1200的沿着线段c

‑

c’(例如:如图3至图4所示)截取的截面图。

351.在一些实施例中,每个主动栅极结构包括栅极介电质以及栅极金属。举例来说,第一主动栅极结构2702包括栅极介电质2704以及栅极金属2706;而第二主动栅极结构2712包括栅极介电质2714以及栅极金属2716。

352.栅极介电质2704与第一主动结构1602a直接接触。栅极介电质2714包裹环绕半导体层2020a

‑

2020c的每一者。如同进一步分别显示于图27b至图27c的,栅极介电质2704被形成为跨坐第一主动结构1602a的顶部表面及侧壁;而栅极介电质2714被形成为包裹环绕半导体层2020a

‑

2020c的每一者(例如:顶部/底部表面以及与y方向垂直的侧壁)。栅极介电质2704与2714可由不同的高k值介电材料或相似的高k值介电材料形成。范例性的高k值介电材料包括hf、al、zr、la、mg、ba、ti、pb及其组合的金属氧化物或硅酸盐。栅极介电质2704与2714可包括多个高k值介电材料的堆叠。可使用任何合适的方法同时或分别沉积栅极介电质2704及2714,包括例如分子束沉积(molecular beam deposition,mbd)、原子层沉积

(ald)、等离子体增强型化学气相沉积(pecvd)等。在一些实施例中,栅极介电质2704及2714可以选择性地包括相当薄的氧化物(例如:sio

x

)层。

353.栅极金属2706可跨坐第一主动结构1602a的顶部表面及侧壁,其中栅极介电质2704被设置在栅极金属2706与第一主动结构1602a之间。栅极金属2716可包裹环绕半导体层2020a

‑

2020c的每一者,其中栅极介电质2714被设置在栅极金属2716与半导体层2020a

‑

2020c之间。如同进一步分别显示于图27b至图27c的,栅极金属2706被形成为跨坐第一主动结构1602a的顶部表面及侧壁,其中栅极介电质被设置于栅极金属2706与第一主动结构1602a之间;而栅极金属2716被形成为包裹环绕半导体层2020a

‑

2020c的每一者(例如:顶部/底部表面以及与y方向垂直的侧壁),其中栅极介电质2714被设置在栅极金属2716与半导体层2020a

‑

2020c之间。具体来说,栅极金属2716可包括沿着z方向彼此邻接(abut)的多个栅极金属部分。每个栅极金属部分不仅可以沿着水平平面(例如:由x方向与y方向扩展的平面)延伸,还可以沿着垂直方向(例如:z方向)延伸。如此一来,两个相邻的栅极金属部分可以毗连(adjoin)在一起,以围绕对应的其中一个半导体层2020a

‑

2020c,其中栅极介电质2714被设置于栅极金属部分与半导体层2020a

‑

2020c之间。

354.栅极金属2706及2716可由不同的金属材料或相似的金属材料形成。栅极金属2706及2716的每一者可包括多个金属材料的堆叠。举例来说,栅极金属2706及2716的每一者可为p型功函数层、n型功函数层、其多层、或其组合。功函数层亦可被称为功函数金属。可包括在栅极结构中以用于p型装置的范例性p型功函数金属包括tin、tan、ru、mo、al、wn、zrsi2、mosi2、tasi2、nisi2、wn、其他合适的p型功函数材料、或其组合。可包括在栅极结构中以用于n型装置的范例性n型功函数金属包括ti、ag、taal、taalc、tialn、tac、tacn、tasin、mn、zr、其他合适的n型功函数材料、或其组合。功函数数值与功函数层的材料组成有关,且因此,功函数层的材料被选择以调谐(tune)其功函数数值,使得在将要形成的装置中能够达成目标临界电压v

t

。功函数层可通过化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)、及/或其他合适的制程来沉积。

355.在一些实施例中,在形成主动栅极结构2702以及主动栅极结构2712之后,gaa晶体管2210与非gaa晶体管2410可被完成。举例来说,gaa晶体管2210可包括分别作为它的栅极、源极以及漏极的栅极结构2712、源极/漏极结构2202、以及源极/漏极结构2204;而非gaa晶体管2410可包括分别作为它的栅极、源极以及漏极的栅极结构2702、源极/漏极结构2402、以及源极/漏极结构2404。

356.为了操作gaa晶体管2210与非gaa晶体管2410,例如作为抗熔丝存储器单元操作,可形成各种互连结构。举例来说,非gaa晶体管2410可作为抗熔丝存储器单元的编程晶体管(例如:图1的编程晶体管110),而gaa晶体管2210可作为抗熔丝存储器单元的读取晶体管(例如:图1的读取晶体管120)。举例来说,各种互连结构可被形成以允许非gaa编程晶体管的漏极(源极/漏极结构2404)与gaa读取晶体管的源极(源极/漏极结构2202)之间的电性连接、将非gaa编程晶体管的栅极(主动栅极结构2702)电性连接至wlp、将gaa读取晶体管的栅极(主动栅极结构2712)电性连接至wlr、以及将gaa读取晶体管的漏极(源极/漏极结构2204)电性连接至bl。

357.对应图18的操作1820,图28是为处于各个制造阶段之一的存储器装置1200的沿着线段a

‑

a’(例如:如图3至图4所示)截取的截面图,其中存储器装置1200包括多个互连结构

(例如:接点(contact))2802、2804、2806、2812、2814及2816。在一些实施例中,互连结构2802、2804、2806提供通往(to)非gaa编程晶体管(非gaa晶体管2410)的电性连接;而互连结构2812、2814及2816提供通往gaa读取晶体管(gaa晶体管2210)的电性连接。

358.如图所示,互连结构2802耦接至主动栅极结构2702(或栅极金属2706);互连结构2804耦接至源极/漏极结构2402;互连结构2806耦接至源极/漏极结构2404;互连结构2812耦接至主动栅极结构2712(或栅极金属2716);互连结构2814耦接至源极/漏极结构2202;而互连结构2816耦接至源极/漏极结构2204。

359.在各种实施例中,为了分别将gaa晶体管2210及非gaa晶体管2410操作为抗熔丝存储器单元的读取晶体管及编程晶体管,可分别经由互连结构2806与2814在源极/漏极结构2404(其作为非gaa晶体管2410的漏极)与源极/漏极结构2202(其作为gaa晶体管2210的源极)之间建立互连结构(例如:可由图5的特征534形成,但并未显示于图28中);wlp可电性连接至主动栅极结构2702(其作为非gaa晶体管2410的栅极);wlr可电性连接至主动栅极结构2712(其作为gaa晶体管2210的栅极);bl可电性连接至源极/漏极结构2204(其作为gaa读取晶体管(gaa晶体管2210)的漏极)。

360.每个互连结构可延伸穿过另一个层间介电质2800以耦接到对应的结构。相对于ild 0(层间介电质2500),由与层间介电质2500相似的介电材料形成的层间介电质2800有时可被称为层间介电质1(ild 1)。互连结构2802可进一步延伸穿过介电质硬遮罩2803(例如:氮化硅)以耦接到主动栅极结构2702;而互连结构2812可进一步延伸穿过介电质硬遮罩2813(例如:氮化硅)以耦接到主动栅极结构2712。这些介电质硬遮罩可在形成主动栅极结构之后且在形成互连结构之前形成。举例来说,在形成主动栅极结构2702及2712之后,可执行蚀刻制程以掘入主动栅极结构2702及2712。被掘入的主动栅极结构可接着被以介电材料(例如:氮化硅)填充,然后再进行平坦化制程(例如:cmp),如此以形成介电质硬遮罩2803及2813。

361.互连结构2802

‑

2816的每一者可包括含金属的材料,例如铜、铝、钨等、其组合、或其多层。举例来说,在形成介电质硬遮罩2803及2813之后,可在存储器装置1200上方沉积层间介电质2800。接着,一或多个接点孔洞(hole)被形成(例如:通过至少一个图案化制程),以延伸穿过层间介电质2800,并选择性地使介电质硬遮罩2803或2813曝露每个结构(例如:主动栅极结构2702、源极/漏极结构2402、源极/漏极结构2404、主动栅极结构2712、源极/漏极结构2202、源极/漏极结构2204)。这些接点孔洞接着被以含金属的材料填充以形成互连结构2802

‑

2816,例如通过电镀(electroplating)、无电电镀(electroless plating)或其他合适的方法填充。在形成互连结构之后,可执行诸如cmp的平坦化制程,以移除含金属材料的多余分。

362.尽管每个互连结构2802

‑

2816在图28中被显示为单一通孔结构,但应理解的是,一些互连结构2802

‑

2816可包括由相似的含金属材料所形成且彼此连接的多个结构。举例来说,互连结构2804、2806、2814及2816中的每一者,可包括md(被形成为狭缝或沟槽结构)与vd(被形成为通孔结构),如同前文参照图5至图10所述。

363.尽管并未图示,但每个互连结构可进一步包括阻障层(barrier layer)。举例来说,每个互连结构的底部表面以及侧壁可被这种阻障层所围绕。阻障层可包括诸如氮化钛的导电材料,但可以替代性地利用诸如氮化钽、钛、钽等的其他材料。可使用cvd制程来形成

阻障层,例如使用pecvd制程。不过,亦可替代性地使用其他替代性方法,例如溅镀(sputtering)、金属有机化学气相沉积(mocvd)、或是ald。

364.图29显示了存储器装置1200的另一个实施例的截面图,此实施例可基于图6的布局600或图7的布局700来制造。再度参照图6至图7,布局600及700的每一者包括一或多个特征(例如:特征602及604),这些特征被用于形成不会被主动栅极结构取代的虚拟栅极结构。

365.如图29所示,当与基于图5的布局500制造的图28所示的实施例相比时,存储器装置1200进一步包括虚拟栅极结构2900及2920。可分别使用特征602及604(图6至图7)在图18的操作1802中形成虚拟栅极结构2900及2920。举例来说,可在形成将于操作1816及1818被对应的主动栅极结构所取代的虚拟栅极结构1902与1912的同时,形成虚拟栅极结构。因此,虚拟栅极结构2900及2920的每一者包括与虚拟栅极结构1902及1912相似的配置,不同之处在于虚拟栅极结构2900及2920被形成在隔离结构1630上方(例如:并未覆盖任何主动区)。

366.举例来说,形成在第二主动区1603b的与第一主动区1603a相对的一侧的隔离结构1630上方的虚拟栅极结构2900,包括虚拟栅极介电质2902以及虚拟栅极2904,其中间隔物2906沿着虚拟栅极结构2900的侧壁延伸;而形成在第一主动区1603a与第二主动区1603b之间的隔离结构1630上方的虚拟栅极结构2920,包括虚拟栅极介电质2922以及虚拟栅极2924,其中间隔物2926沿着虚拟栅极结构2920的侧壁延伸。不过,虚拟栅极结构2900及2920将不会在操作1816及1818中被主动栅极结构所取代,举例来说,通过在操作1816及1818中遮蔽虚拟栅极结构2900及2920,虚拟栅极结构2900及2920将不会被主动栅极结构所取代。在形成主动栅极结构2702及2712之后,主动栅极结构2702及2712还有虚拟栅极结构2900及2920均可被掘入,以被对应的介电质硬遮罩所覆盖。举例来说,虚拟栅极结构2900及2920分别被介电质硬遮罩2908及2928所覆盖。

367.图30显示了存储器装置1200的另一个实施例的截面图,此实施例可基于图9的布局900来制造。再度参照图9,布局900包括额外的栅极特征908(相对于图5的布局500),栅极特征908行进跨越主动特征902b,这使得存储器装置1200形成了另一个gaa晶体管的主动栅极结构。举例来说,在图19a至图19c中,于图18的操作1802处使用栅极特征908形成额外的虚拟栅极结构(相对于虚拟栅极结构1902及1912)之后,图18的方法1800的剩余操作可被用于形成存储器装置1200,其中存储器装置1200包括一个非gaa晶体管与两个gaa晶体管。

368.如图30所示,除了可分别由栅极特征904及906所形成的非gaa晶体管2410及gaa晶体管2210的主动栅极结构之外,存储器装置1200还包括另一个gaa晶体管3000的主动栅极结构3006,其中主动栅极结构3006可通过栅极特征908形成。因为栅极特征906及908均行进穿过主动特征902b,因此形成的gaa晶体管2210及3000可共享源极/漏极结构2204,但具有各自的通道。举例来说,gaa晶体管3000包括共同作为它的通道的多个半导体层3002。gaa晶体管3000包括连接至半导体层3002的一端的共享的源极/漏极结构2204,以及包括连接至半导体层3002的另一端的源极/漏极结构3004。主动栅极结构3006及源极/漏极结构3004通过各自的互连结构3008及3010连接,以致能(enable)包括一个非gaa编程晶体管与两个gaa读取晶体管的存储器装置1200的操作。举例来说,第二读取字元线(wlr2)经由互连结构3008连接至gaa晶体管3000的主动栅极结构3006(其中第一读取字元线(wlr1)连接至gaa晶体管2210的主动栅极结构),而bl经由互连结构3010连接至gaa晶体管3000的源极/漏极结构3004。

369.图31显示了存储器装置1200的另一个实施例的截面图,此实施例可基于图10的布局1000来制造。再度参照图10,当与图9的布局900相比时,布局1000包括一或多个附加特征(例如:特征1002及1004)。特征1002及1004可被配置以形成不会被主动栅极结构所取代的虚拟栅极结构。

370.如图31所示,当与基于图9的布局900制造的图30所示的实施例相比时,存储器装置1200进一步包括虚拟栅极结构3100及3120。可分别使用特征1002及1004(图10)在图18的操作1802中形成虚拟栅极结构3100及3120。举例来说,在图19a至图19c中,可在形成将于操作1816及1818被对应的主动栅极结构所取代的虚拟栅极结构1902与1912的同时,形成虚拟栅极结构。因此,虚拟栅极结构3100及3120的每一者包括与虚拟栅极结构1902及1912相似的配置,不同之处在于虚拟栅极结构3100及3120被形成在隔离结构1630上方(例如:并未覆盖任何主动区)。

371.举例来说,形成在第二主动区1603b的与第一主动区1603a相对的一侧的隔离结构1630上方的虚拟栅极结构3100,包括虚拟栅极介电质3102以及虚拟栅极3104,其中间隔物3106沿着虚拟栅极结构3100的侧壁延伸;而形成在第一主动区1603a与第二主动区1603b之间的隔离结构1630上方的虚拟栅极结构3120,包括虚拟栅极介电质3122以及虚拟栅极3124,其中间隔物3126沿着虚拟栅极结构3120的侧壁延伸。不过,虚拟栅极结构3100及3120将不会在操作1816及1818中被主动栅极结构所取代,举例来说,通过在操作1816及1818中遮蔽虚拟栅极结构3100及3120,虚拟栅极结构3100及3120将不会被主动栅极结构所取代。在形成主动栅极结构2702、2712及3006之后,主动栅极结构2702、2712及3006还有虚拟栅极结构3100及3120均可被掘入,以被对应的介电质硬遮罩所覆盖。举例来说,虚拟栅极结构3100及3120分别被介电质硬遮罩3108及3128所覆盖。

372.图32显示了存储器装置1200的另一个实施例的截面图,此实施例可基于图8的布局800来制造。再度参照图8,布局800包括由栅极特征504所部分覆盖的特征802a(主动特征)(相对于图5至图7的布局500

‑

700),这使得所形成的非gaa晶体管仅具有一个源极/漏极结构(mos电容器)。举例来说,在图19a至图19c中,在使用特征802a于图11的操作1110(或图17的操作1712)中形成第一主动结构1602a,并接着使用栅极特征504于图18的操作1802中形成虚拟栅极结构1902之后,虚拟栅极结构1902可不仅是跨坐第一主动结构1602a,还可以在x方向上沿着第一主动结构1602a的其中一个侧壁延伸。图18的方法1800的剩余操作可被用于形成存储器装置1200,此存储器装置1200包括一个被形成为mos电容器的非gaa晶体管以及一个gaa晶体管。

373.如图32所示,存储器装置1200包括被形成为mos电容器的非gaa晶体管3200。非gaa晶体管3200包括主动栅极结构3202,主动栅极结构3202取代了如上所述由栅极特征504所形成的虚拟栅极结构1902。包括栅极介电质3204及栅极金属3206的主动栅极结构3202不仅跨坐第一主动结构1602a,还在x方向上沿着第一主动结构1602a的其中一个侧壁延伸。主动栅极结构3202的各个侧壁(沿着x方向)亦被栅极间隔物3208所覆盖。如此一来,非gaa晶体管3200可仅包括沿着第一主动结构1602a的其中一个侧壁(沿着x方向)形成的源极/漏极结构2404,其中该侧壁并未被主动栅极结构3202所覆盖。

374.在本公开的一个态样中,公开了一种存储器装置。上述存储器装置包括形成于一基板的第一区域中的第一晶体管。第一晶体管包括自上述基板突出的突出结构,以及耦接

至突出结构的第一端的第一源极/漏极(s/d)结构。上述存储器装置包括形成于上述基板的第二区域中的第二晶体管。第二晶体管包括垂直地彼此间隔的多个第一半导体层、耦接至多个第一半导体层的第一端的第二源极/漏极结构、以及耦接至多个第一半导体层的第二端的第三源极/漏极结构。第一区域与第二区域通过隔离结构彼此横向地分隔。

375.在一或多个实施例中,第一晶体管被配置为抗熔丝存储器单元的编程晶体管,而第二晶体管被配置为抗熔丝存储器单元的读取晶体管。在一或多个实施例中,第一晶体管经由互连结构串联地电性耦接至第二晶体管,互连结构被设置于上述基板上方,且将第一源极/漏极结构连接至第二源极/漏极结构或第三源极/漏极结构中的至少一者。

376.在一或多个实施例中,第一晶体管包括第一栅极结构,第一栅极结构跨坐于突出结构的中心部分,而第二晶体管包括第二栅极结构,第二栅极结构包括有效地与第一半导体层关联的多个全环栅极堆叠。在一或多个实施例中,第一晶体管包括第四源极/漏极结构,耦接至突出结构的第二端,其中与第一源极/漏极结构相比,第四源极/漏极结构被设置为更加远离隔离结构。

377.在一或多个实施例中,第一晶体管包括鳍式晶体管,而第二晶体管包括栅极全环晶体管。在一或多个实施例中,上述存储器装置还包括至少一个虚拟栅极结构,至少一个虚拟栅极结构设置于第一区域与第二区域之间。

378.在一或多个实施例中,上述存储器装置还包括形成在上述基板的第二区域中的第三晶体管,第三晶体管包括:多个第二半导体层,垂直地彼此分隔,第三源极/漏极结构耦接至多个第二半导体层的第一端;以及第五源极/漏极结构,电性耦接至第二半导体层的第二端。

379.在一或多个实施例中,第一晶体管被配置为抗熔丝存储器单元的编程晶体管,第二晶体管被配置为抗熔丝存储器单元的第一读取晶体管,而第三晶体管被配置为抗熔丝存储器单元的第二读取晶体管。

380.在一或多个实施例中,第一源极/漏极结构具有第一垂直高度,而第二源极/漏极结构以及第三源极/漏极结构具有第二垂直高度,其中第二垂直高度大于第一垂直高度。

381.在本公开的另一个态样中,公开了一种一次性可编程(otp)存储器装置。上述一次性可编程存储器装置包括形成于一基板的第一区域中的编程晶体管。上述一次性可编程存储器装置包括串联地电性连接至编程晶体管且形成于上述基板的第二区域中的第一读取晶体管。第一区域通过隔离结构与第二区域横向分隔。编程晶体管包括第一栅极结构,第一栅极结构跨坐于突出自上述基板的突出结构,而第一读取晶体管包括第二栅极结构,第二栅极结构包裹环绕多个第一纳米结构的每一者,其中多个第一纳米结构彼此间垂直地分隔。

382.在一或多个实施例中,突出结构被配置以作为编程晶体管的通道,而第一纳米结构被配置以作为第一读取晶体管的通道。在一或多个实施例中,编程晶体管包括耦接至突出结构的第一端的第一源极/漏极结构,而第一读取晶体管包括分别耦接至多个第一纳米结构的第一端以及第二端的第二源极/漏极结构以及第三源极/漏极结构。

383.在一或多个实施例中,第一源极/漏极与第二源极/漏极接近地彼此相邻,但通过隔离结构彼此分隔。在一或多个实施例中,第一源极/漏极结构具有第一垂直高度,而第二源极/漏极结构与第三源极/漏极结构具有第二垂直高度,其中第二垂直高度大于第一垂直

高度。

384.在一或多个实施例中,上述一次性可编程存储器装置还包括互连结构,互连结构设置于上述基板上方,且将第一源极/漏极结构连接至第二源极/漏极结构或第三源极/漏极结构中的至少一者。

385.在一或多个实施例中,上述一次性可编程存储器装置还包括第二读取晶体管,串联地电性耦接至第一读取晶体管且形成于上述基板的第二区域中,其中第二读取晶体管包括第三栅极结构,第三栅极结构包裹围绕多个第二纳米结构的每一者,多个第二纳米结构彼此垂直分隔。

386.在一或多个实施例中,上述一次性可编程存储器装置还包括至少一个虚拟栅极结构,至少一个虚拟栅极结构设置于第一区域与第二区域之间。

387.在本公开的又一个态样中,公开了一种存储器装置的制造方法。上述存储器装置的制造方法包括在一基板上定义第一主动区与第二主动区。第一主动区与第二主动区通过隔离结构彼此横向地分隔。上述存储器装置的制造方法包括在第一主动区中形成第一晶体管。第一晶体管包括自上述基板突出的突出结构所形成的第一通道、跨坐于第一通道上方的第一主动栅极结构、以及至少包括耦接至第一通道的一端的第一源极/漏极结构。上述存储器装置的制造方法包括在第二主动区中形成第二晶体管。第二晶体管包括设置于上述基板上方的一或多个半导体层所共同形成的第二通道、包裹围绕第二通道的第二主动栅极结构、耦接至第二通道的一端的第二源极/漏极结构、以及耦接至第二通道的另一端的第三源极/漏极结构。

388.在一或多个实施例中,第一晶体管被配置为抗熔丝存储器单元的编程晶体管,而第二晶体管被配置为抗熔丝存储器单元的读取晶体管。

389.前述内文概述多项实施例或范例的特征,如此可使于本技术领域中具有通常知识者更佳地了解本公开的态样。本技术领域中具有通常知识者应当理解他们可轻易地以本公开为基础设计或修改其他制程及结构,以完成相同的目的及/或达到与本文介绍的实施例或范例相同的优点。本技术领域中具有通常知识者亦需理解,这些等效结构并未脱离本公开的精神及范围,且在不脱离本公开的精神及范围的情况下,可对本公开进行各种改变、置换以及变更。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1