基于标准CMOS工艺的浮栅突触

基于标准cmos工艺的浮栅突触

技术领域

1.本发明涉及神经形态器件技术领域,尤其涉及一种基于标准cmos工艺的浮栅突触。

背景技术:

2.随着人工智能领域的兴起,全球产生的数据集规模每两年翻一番,并将很快超越目前计算和存储设备的极限。传统的冯

·

诺依曼计算机架构由于内存模块和处理器的分离将面临一系列问题,如“存储墙”、“功耗墙”等。未来的智能化社会势必需要高能效、自适应强的新型计算范式作为支撑。

3.人脑由约10

11

个神经元和约10

15

个突触组成,是自然界高性能、低功耗计算硬件的典范。21世纪以来,神经形态(或类脑)计算以其存算一体、高度并行和极低功耗等优点,被认为是最有希望解决冯

·

诺依曼瓶颈的方法之一。在人脑中,神经元是人脑功能的基本单元,而突触是神经元进行信号传递和信息交换的重要结构,也是模拟人脑记忆和学习的基础。因此,实现神经形态计算的重要前提是开发能模拟生物突触行为的人工突触器件。

4.使用新兴的忆阻器构建人工突触器件是当下实现神经形态计算的研究热点。但忆阻器件种类繁杂,大多数由特殊的材料和特定的工艺制造,缺乏用于制造它们的统一工艺流程,这导致现有忆阻器件难与标准cmos工艺兼容。忆阻器的商业化进一步受到可靠性问题的阻碍,包括工艺一致性和泄漏电流路径问题。对于忆阻器的大规模集成而言,其制造工艺仍很不成熟。

5.因此,基于浮栅mos晶体管的突触器件应运而生。目前流行的浮栅mos突触器件普遍采用双层多晶硅工艺的结构,不能完全与标准cmos工艺兼容。该结构有两层栅,分别为控制栅和浮栅,需要不同的栅氧化层厚度,以及需要调整不同的掺杂浓度等,都增加了工艺的复杂性和成本。面对这一系列的挑战,寻找一种完全与标准cmos工艺兼容的突触器件是有必要的。

技术实现要素:

6.为克服上述现有技术中存在的问题,本发明提供了一种基于标准cmos工艺的浮栅突触,以实现一种工艺简单、成本低及易于大规模集成的神经形态突触器件。

7.为达到上述目的,本发明采用如下技术方案:

8.本发明提供了一种基于标准cmos工艺的浮栅突触,包括2个标准mos晶体管m1和m2,其中m1为隧穿晶体管,其当作突触前神经元,用来接收尖峰刺激v

pre

;m2为输出信号管,其当作突触后神经元,用来输出突触后电流;通过共浮栅方式隧穿晶体管m1控制输出信号管m2的沟道电流状态,进而影响输出信号管m2的漏极电流,并以此模拟生物突触行为。

9.所述隧穿晶体管m1是一个mos电容器,由漏极、源极和阱短接的标准mos晶体管构成,其短接端口连接到输入电压v

pre

。

10.所述输出信号管m2通过共浮栅的方式与隧穿晶体管m1连接在一起,而且输出信号

管m2的源极外接固定偏压v

bias

,以保证其工作在晶体管亚阈值区,实现低功耗的工作状态。

11.所述共浮栅方式指隧穿晶体管m1和输出信号管m2的控制栅相连接并形成浮栅,浮栅被栅氧化层隔离,具有非易示性。通过福勒-诺德海姆(fn)隧穿对浮栅电荷进行改变,进而影响所述输出信号管m2的漏极电流,因此m2的漏极电流可以用来表征突触强度。

12.进一步地,所述输出信号管m2工作在亚阈值区,而mos晶体管亚阈值区的漏极电流和栅极电压之间的指数性质恰恰与生物突触电流的指数性质相吻合,这将有助于突触功能的实现。

13.进一步地,所述基于标准cmos工艺的浮栅突触器件,包括兴奋性突触器件和抑制性突触器件两种结构:

14.所述兴奋性突触由两个nmos晶体管构成,用来实现生物突触的兴奋性突触后电流(epsc)、短时程增强(stp)和双脉冲易化(ppf)等行为,

15.所述兴奋性突触由两个pmos晶体管构成,用来实现生物突触的抑制性突触后电流(ipsc)、短时程抑制(std)和双脉冲抑制(ppd)等行为。

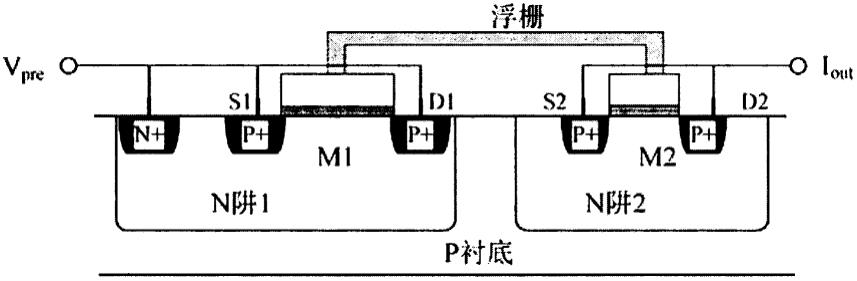

16.本发明的有益效果如下:

17.1、本发明提供的浮栅突触完全与标准cmos工艺兼容,易于大规模集成,是一种潜在的商业化突触器件方案。

18.2、本发明提出的突触器件工作在晶体管亚阈值区,为构建高密度的低功耗神经形态系统奠定了基础。

19.3、本发明提出的突触器件中的浮栅通过单多晶硅工艺实现,可以降低制造成本。

附图说明

20.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图。

21.图1为基于标准cmos工艺的浮栅突触的结构示意图;

22.图2为兴奋性突触后电流的理想曲线图;

23.图3为兴奋性突触器件的电路模型图;

24.图4为单个脉冲下的兴奋性突触后电流仿真图;

25.图5为连续脉冲下的短时程增强现象;

26.图6为双脉冲易化现象;

27.图7为抑制性突触器件的电路模型图;

28.图8为单个脉冲下的兴奋性突触后电流仿真图;

29.图9为在连续脉冲下的短时程抑制现象;

30.图10为双脉冲抑制现象。

具体实施方式

31.为使本发明的上述目的、特征和优点能够更加明显易懂,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例

仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动的前提下所获得的所有其它实施例,均属于本发明保护的范围。

32.现阶段,具有独特物理机制的神经突触器件是神经形态计算硬件的基本组成单元,对新型非冯

·

诺依曼架构芯片的研发乃至类脑智能的最终实现都具有重要意义。然而,目前的人工神经突触器件大多由特殊的材料和特定的工艺制造,没有统一的制造流程。对于大规模的集成而言,其制造成本高、制造工艺不成熟。

33.为解决上述问题,本发明的实施例提供了一种基于标准cmos工艺的浮栅突触。

34.实施例1

35.图1示出了本发明实施例提供的基于标准cmos工艺的浮栅突触的结构示意图(以pmos为例),包括一个隧穿晶体管m1和输出晶体管m2。隧穿管m1是一个mos电容器,由漏极,源极和阱短接的标准mos晶体管构成,其短接端口连接到输入电压v

pre

。隧穿管m1和输出管m2的栅极相连形成浮栅,浮栅被栅氧化层隔离,可以长时间存储电荷,具有非易失性。在输入电压v

pre

的作用下,隧穿管m1的栅和阱之间发生福勒-诺德海姆(fn)隧穿效应,进而改变浮栅电荷。那么根据浮栅上的电荷量来更改输出管m2的漏极电流,因此输出管m2的漏极电流可以代表突触强度。此外,输出管m2的源极外接固定偏压v

bias

,以此保证其工作在晶体管亚阈值区,实现低功耗的突触器件。而晶体管亚阈值区中驱动电流扩散和漂移的力与神经元中驱动离子电流通过离子通道的力相同。因此,亚阈值区的mos晶体管是模拟神经突触离子通道行为的理想结构。本发明提出的基于标准cmos工艺的浮栅突触,包括兴奋性突触器件和抑制性突触器件两种结构。二者的结构相同,均基于上述原理,其中兴奋性突触利用nmos晶体管实现,抑制性突触利用pmos晶体管实现。

36.模拟生物突触行为的关键是模拟突触电流的形状与特性。为了创建精确的突触电路,需要研究由前突触动作电位产生的突触后电流。兴奋性突触后电流的数学模型为

[0037][0038]

其中t

peak

的大小通常为0.1ms。由公式(1)可以看出,突触电流与时间呈现出指数相关。图2为通过matlab拟合的兴奋性突触电流的曲线图,其首先在短时间内达到峰值,然后再缓慢下降恢复为初始状态。事实上,抑制性突触后电流为其镜像结果。mos晶体管亚阈值区域的漏极电流和栅极电压之间的指数性质恰恰和公式(1)所给出的数学模型中突触输出电流的指数性质相吻合,这将有助于突触功能的实现。

[0039]

实施例2

[0040]

图3示出了在cadence spectre中,构建的兴奋性突触的电路模型图,它由两个nmos晶体管n1和n2构成。n1为隧穿晶体管,其漏极、源极和阱短接形成mos电容器,短接端口连接到输入电压v

pre

。它的设计目的是实现栅极和阱之间的隧穿,允许修改浮栅中的电荷,进而影响突触输出电流。为了保证输出晶体管n2工作在亚阈值区,在其源极施加一个固定的正偏压,且输出晶体管n2的漏极电流为突触的输出电流。

[0041]

图4为兴奋性突触后电流(epsc)的仿真图。通过对兴奋性突触的隧穿管n1短接端施加三角脉冲电压,输出管n2的漏极输出兴奋突触后电流。输入三角脉冲的斜率会影响突触电流的形状,突触电流先是快速上升然后是缓慢下降的指数衰减,其形状和图3中的兴奋

性突触后电流的数学模型的曲线图相吻合。

[0042]

图5为在连续三角脉冲电压的刺激下,兴奋性突触后电流的仿真结果图。可以看出,在连续三角脉冲电压的刺激下,兴奋性突触后电流的幅度随时间逐渐升高,并在数十毫秒内保持稳定,这类似于生物突触的短时程增强(stp)现象。这是由于随着隧穿效应的发生,浮栅积累的电荷导致隧穿管两端的压降变低,直至对于隧穿所需的电压差时,隧穿停止,因此突触电流的增幅也逐渐减弱最终趋于稳定。

[0043]

图6为在两个连续的三角脉冲刺激下,兴奋性突触后电流的仿真结果图。可以看出,第二个脉冲比第一个脉冲产生更大幅度的兴奋性突触后电流,这类似于生物突触的双脉冲易化(ppf)现象。这是由于在第一个脉冲阶段内的隧穿效应积累到第二个脉冲阶段。

[0044]

实施例3

[0045]

图7示出了在cadence spectre中,构建的抑制性突触的电路模型图,它由两个pmos晶体管p1和p2构成。其中p1为隧穿晶体管,其漏极、源极和阱短接形成mos电容器,短接端口连接到隧穿电势v

pre

。它的设计目的同样是实现栅极和阱之间的隧穿,允许修改浮栅中的电荷,进而影响突触输出电流。为了保证输出晶体管p2工作在亚阈值区,在其源极施加一个固定的负偏压,输出晶体管p2的漏极电流为突触输出电流。

[0046]

图8为抑制性突触后电流(ipsc)的仿真图。通过对抑制性突触的隧穿管p1短接端施加三角脉冲电压,输出管p2的漏极输出抑制性突触后电流。抑制性突触后电流具有先快速下降然后缓慢上升的形状,恰恰是兴奋性突触后电流的镜像结果。

[0047]

图9为在连续的三角脉冲刺激下,抑制性突触后电流的仿真结果图。可以看出,在连续三角脉冲电压的刺激下,抑制性突触后电流的幅度随时间逐渐降低,并在数十毫秒内保持稳定,这类似于生物突触的短时程抑制(std)现象。短时程抑制指突触传递效率降低的变化现象,这种变化也持续在数十毫秒内,与仿真结果一致。

[0048]

图10为在两个连续的三角脉冲刺激下,抑制性突触后电流的仿真结果图。可以看出,第二个脉冲比第一个脉冲产生更小幅度的兴奋性突触后电流,这类似于生物突触的双脉冲抑制(ppd)现象。

[0049]

综上所述,本发明提出的基于标准cmos工艺的浮栅突触可以很好的模拟生物突触行为,是一款结构简单、成本较低、易大规模集成的神经突触器件,在未来有广阔的应用前景。

[0050]

以上所述仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1