用于测试错误校正电路的半导体器件和半导体系统的制作方法

用于测试错误校正电路的半导体器件和半导体系统

1.相关申请的交叉引用

2.本技术要求于2021年3月31日提交的申请号为10-2021-0042383的韩国专利申请的优先权,其全部内容通过引用合并于此。

技术领域

3.本公开的实施例涉及一种半导体系统,其在错误校正测试模式下测试半导体器件中包括的错误校正电路。

背景技术:

4.近来,为了提高半导体器件的运行速度,使用了在每个时钟周期中输入/输出具有多个比特位的数据的各种方案。在其中数据的输入/输出速度提高的情况下,在数据传输过程期间出现错误的概率也会增加。因此,额外需要一种用于确保数据传输的可靠性的单独装置和方法。

5.例如,存在一种产生错误码的方法,其能够在每次传输数据时检查错误的出现并将错误码与数据一起传输,从而保证数据传输的可靠性。错误码包括能够检测出现的错误的错误检测码(edc)和能够在出现错误时自校正错误的错误校正码(ecc)。

技术实现要素:

6.在一个实施例中,一种半导体器件可以包括:控制电路,其被配置为基于用于执行错误校正测试模式的写入控制信号、写入检查命令、读取控制信号和读取检查命令来产生输入使能信号、输出使能信号、锁存控制信号和错误校正控制信号;锁存电路,在锁存的控制信号被使能的时段期间,其被配置为通过锁存输入数据、输入奇偶校验和输入掩蔽信号来产生锁存数据、锁存奇偶校验和锁存掩蔽信号,并且被配置为将经校正的数据重新储存为锁存数据;以及错误校正电路,其被配置为:在错误校正控制信号被使能的时段期间通过基于锁存数据、锁存奇偶校验和锁存掩蔽信号来校正锁存数据中包括的错误以产生经校正的数据。

7.在一个实施例中,一种半导体系统可以包括:控制器,其被配置为:通过向半导体器件输出用于进入错误校正测试模式的命令,输出第一外部数据、第一外部奇偶校验和第一掩蔽信息信号,以及接收从半导体器件输出的第二外部数据和第二掩蔽信息信号来测试半导体器件中包括的错误校正电路;以及包括错误校正电路的半导体器件,该半导体器件被配置为:基于第一外部数据、第一外部奇偶校验和第一掩蔽信息信号来校正第一外部数据中包括的错误,输出经错误校正的第一外部数据作为第二外部数据,以及输出关于第一外部数据的错误信息作为第二掩蔽信息信号。

附图说明

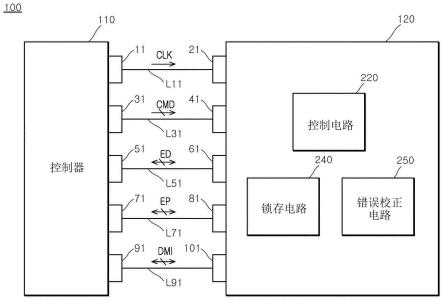

8.图1是示出根据本公开的实施例的半导体系统的配置的框图。

9.图2是示出图1所示的半导体系统中包括的半导体器件的配置的框图。

10.图3是示出图2所示的半导体器件中包括的控制电路的配置的框图。

11.图4是示出图3所示的控制电路中包括的缓冲器控制电路的配置的框图。

12.图5是示出图4所示的缓冲器控制电路中包括的输入控制电路的配置的电路图。

13.图6是示出图4所示的缓冲器控制电路中包括的输出控制电路的配置的电路图。

14.图7是示出图3所示的控制电路中包括的测试控制电路的配置的电路图。

15.图8至图11是帮助说明在根据本公开的实施例的半导体系统中执行错误校正测试模式的操作的示图。

16.图12是示出应用了图1至图11所示的半导体系统的电子系统的实施例的配置的示图。

具体实施方式

17.术语“预设”是指当在过程或算法中使用参数时该参数的数值是预先确定的。根据实施例,参数的数值可以在过程或算法开始时或在过程或算法被执行期间设置。

18.诸如“第一”和“第二”等用于区分各种组件的术语不受组件的限制。例如,第一组件可以被称为第二组件,并且反之亦然。

19.当一个组件被称为“耦接”或“连接”到另一组件时,应当理解,这些组件可以直接耦接或连接到彼此,或者通过介于其间的另一组件耦接或连接到彼此。另一方面,当一个组件被称为“直接耦接”或“直接连接”到另一组件时,应当理解,这些组件直接耦接或连接到彼此,而没有另一组件介于其间。

[0020]“逻辑高电平”和“逻辑低电平”被用于描述信号的逻辑电平。具有“逻辑高电平”的信号区别于具有“逻辑低电平”的信号。例如,当具有第一电压的信号对应于“逻辑高电平”时,具有第二电压的信号可以对应于“逻辑低电平”。根据实施例,“逻辑高电平”可以被设置为高于“逻辑低电平”的电压。根据实施例,信号的逻辑电平可以被设置为不同的逻辑电平或相反的逻辑电平。例如,根据实施例可以将具有逻辑高电平的信号设置为具有逻辑低电平,并且根据实施例可以将具有逻辑低电平的信号设置为具有逻辑高电平。

[0021]

在下文中,将通过实施例更详细地描述本公开的教导。实施例仅被用于举例说明本公开的教导,并且本公开的范围不受这些实施例的限制。

[0022]

各种实施例针对一种半导体系统,该半导体系统通过经由半导体器件中包括的错误校正电路校正包括错误的外部数据的错误并由控制器检测外部数据的错误是否得到校正来在错误校正测试模式中测试错误校正电路。

[0023]

根据本公开的实施例,能够通过经由半导体器件中包括的错误校正电路校正包括错误的外部数据的错误并由控制器检测外部数据的错误是否得到校正来在错误校正测试模式中测试错误校正电路。

[0024]

此外,根据本公开的实施例,通过在错误校正测试模式中测试半导体器件中包括的错误校正电路,能够确保其错误通过错误校正电路得到校正的数据在正常模式中的可靠性。

[0025]

如在图1中所示的,根据本公开的实施例的半导体系统100可以包括控制器110和半导体器件120。半导体器件120可以包括控制电路220、锁存电路240和错误校正电路250。

[0026]

控制器110可以包括第一控制引脚11、第二控制引脚31、第三控制引脚51、第四控制引脚71和第五控制引脚91。半导体器件120可以包括第一半导体引脚21、第二半导体引脚41、第三半导体引脚61、第四半导体引脚81和第五半导体引脚101。第一传输线l11可以耦接在第一控制引脚11与第一半导体引脚21之间。第二传输线l31可以耦接在第二控制引脚31与第二半导体引脚41之间。第三传输线l51可以耦接在第三控制引脚51与第三半导体引脚61之间。第四传输线l71可以耦接在第四控制引脚71与第四半导体引脚81之间。第五传输线l91可以耦接在第五控制引脚91与第五半导体引脚101之间。控制器110可以通过第一传输线l11将时钟clk传输到半导体器件120,以便控制半导体器件120。控制器110可以通过第二传输线l31将命令cmd传输到半导体器件120,以便控制半导体器件120。控制器110和半导体器件120可以通过第三传输线l51发送和接收外部数据ed。控制器110和半导体器件120可以通过第四传输线l71发送和接收外部奇偶校验ep。控制器110和半导体器件120可以通过第五传输线l91发送和接收掩蔽信息信号dmi。

[0027]

控制器110可以将用于执行错误校正测试模式操作的时钟clk和命令cmd输出到半导体器件120。在错误校正测试模式中,控制器110可以将包括错误的外部数据ed输出到半导体器件120。在错误校正测试模式中,控制器110可以将包括关于不包括错误的外部数据ed的错误信息的外部奇偶校验ep输出到半导体器件120。在错误校正测试模式中,控制器110可以将用于阻挡外部数据ed中包括的一些比特位的掩蔽信息信号dmi输出到半导体器件120。在错误校正测试模式中,控制器110可以通过接收外部数据ed和掩蔽信息信号dmi来测试半导体器件120中包括的错误校正电路250。在错误校正测试模式中,当从半导体器件120输出的外部数据ed得到错误校正时,控制器110可以确认错误校正电路250执行正常操作。在错误校正测试模式中,当从半导体器件120输出的外部数据ed没有得到错误校正时,控制器110可以确认错误校正电路250执行异常操作。在错误校正测试模式中,当作为从半导体器件120输出的掩蔽信息信号dmi而输出的奇偶校验被正常地产生时,控制器110可以确认错误校正电路250执行正常操作。在错误校正测试模式中,当作为从半导体器件120输出的掩蔽信息信号dmi而输出的奇偶校验没有被正常产生时,控制器110可以确认错误校正电路250执行异常操作。命令cmd、外部数据ed、外部奇偶校验ep和掩蔽信息信号dmi可以同步于时钟clk中包括的奇数脉冲或偶数脉冲而被连续地输入和输出。

[0028]

控制电路220可以基于写入控制信号wec(参见图2)、读取控制信号rec(参见图2)、写入检查命令wcs(参见图2)和读取检查命令rcs(参见图2)来产生锁存控制信号lc_ctr(参见图2)和错误校正控制信号ecc_ctr(参见图2),所述写入控制信号wec、读取控制信号rec、写入检查命令wcs和读取检查命令rcs是基于用于执行错误校正测试模式的命令cmd和码信号code(参见图2)的逻辑电平来产生的。

[0029]

锁存电路240可以通过在锁存控制信号lc_ctr(参见图2)被使能的时段期间锁存输入数据in_d(参见图2)、输入奇偶校验in_p(参见图2)和输入掩蔽信号in_dmi(参见图2)来产生锁存数据ld(参见图2)、锁存奇偶校验lp(参见图2)和锁存掩蔽信号ldmi(参见图2)。锁存电路240可以将当输入数据in_d(参见图2)中包括的错误被校正而产生的经校正的数据cd(参见图2)重新储存为锁存数据ld(参见图2)。可以从外部数据ed产生输入数据in_d(参见图2),可以从外部奇偶校验ep产生输入奇偶校验in_p(参见图2),并且可以从掩蔽信息信号dmi产生输入掩蔽信号in_dmi(参见图2)。

[0030]

在错误校正控制信号ecc_ctr(参见图2)被使能的时段期间,错误校正电路250可以通过基于锁存数据ld(参见图2)、锁存奇偶校验lp(参见图2)和锁存掩蔽信号ldmi(参见图2)校正锁存数据ld(参见图2)中包括的错误来产生经校正的数据cd(参见图2)。在错误校正控制信号ecc_ctr(参见图2)被使能的时段期间,错误校正电路250可以通过经由执行ecc解码操作校正锁存数据ld(参见图2)中包括的错误来产生经校正的数据cd(参见图2)。

[0031]

在错误校正测试模式中,半导体器件120可以基于外部数据ed、外部奇偶校验ep和掩蔽信息信号dmi来校正外部数据ed中包括的错误。在错误校正测试模式中,半导体器件120可以将经错误校正的外部数据ed和掩蔽信息信号dmi输出到控制器110。

[0032]

图2是示出半导体器件120的实施例的配置的框图。如图2中所示,半导体器件120可以包括命令解码器210、控制电路220、输入电路230、锁存电路240、错误校正电路250、寄存器260、核心电路270和输出电路280。

[0033]

命令解码器210可以同步于时钟clk来基于码信号code的逻辑电平产生写入控制信号wec和读取控制信号rec。命令解码器210可以通过同步于时钟clk对码信号code进行解码来产生被选择性地使能的写入控制信号wec和读取控制信号rec。码信号code可以被设置为被内部产生以进入错误校正测试模式的信号。虽然码信号code被示出为一个信号,但是要注意,码信号code可以被设置为包括多个比特位的信号。命令解码器210可以同步于时钟clk来基于命令cmd的逻辑电平产生写入检查命令wcs和读取检查命令rcs。命令解码器210可以通过同步于时钟clk对命令cmd进行解码来产生被选择性地使能的写入检查命令wcs和读取检查命令rcs。命令cmd可以被设置为从控制器110输入以进入错误校正测试模式的信号。虽然命令cmd被示为一个信号,但是要注意,命令cmd可以被设置为包括多个比特位的信号。

[0034]

控制电路220可以基于写入控制信号wec、读取控制信号rec、写入检查命令wcs和读取检查命令rcs来产生输入使能信号in_en、输出使能信号out_en、锁存控制信号lc_ctr和错误校正控制信号ecc_ctr。控制电路220可以基于写入控制信号wec、读取控制信号rec、写入检查命令wcs和读取检查命令rcs的逻辑电平来产生输入使能信号in_en、输出使能信号out_en、锁存控制信号lc_ctr和错误校正控制信号ecc_ctr。

[0035]

输入电路230可以在输入使能信号in_en被使能的时段期间从内部数据id、外部数据ed、外部奇偶校验ep和掩蔽信息信号dmi产生输入数据in_d、输入奇偶校验in_p和输入掩蔽信号in_dmi。在输入使能信号in_en被使能的时段期间,输入电路230可以通过基于掩蔽信息信号dmi阻挡外部数据ed的一些比特位并且用内部数据id替换外部数据ed的被阻挡的一些比特位来产生输入数据in_d。在输入使能信号in_en被使能的时段期间,输入电路230可以通过缓冲外部奇偶校验ep和掩蔽信息信号dmi来产生输入奇偶校验in_p和输入掩蔽信号in_dmi。当错误校正测试模式结束并进入正常模式时,输入电路230可以通过缓冲外部数据ed来产生内部数据id。

[0036]

在锁存控制信号lc_ctr被使能的时段期间,锁存电路240可以通过锁存输入数据in_d、输入奇偶校验in_p和输入掩蔽信号in_dmi来产生锁存数据ld、锁存奇偶校验lp和锁存掩蔽信号ldmi。在锁存控制信号lc_ctr被使能的时段期间,锁存电路240可以将当输入数据in_d中包括的错误被校正而产生的经校正的数据cd重新储存为锁存数据ld。在锁存控制信号lc_ctr被使能的时段期间,锁存电路240可以重新储存包括关于输入数据in_d的错误

信息的锁存奇偶校验lp。

[0037]

在错误校正控制信号ecc_ctr被使能的时段期间,错误校正电路250可以通过基于锁存数据ld、锁存奇偶校验lp和锁存掩蔽信号ldmi校正锁存数据ld中包括的错误来产生经校正的数据cd。在错误校正控制信号ecc_ctr被使能的时段期间,错误校正电路250可以通过执行ecc解码操作校正锁存数据ld中包括的错误来产生经校正的数据cd。在错误校正控制信号ecc_ctr被使能的时段期间,错误校正电路250可以通过执行ecc编码操作来产生包括关于锁存数据ld的错误信息的锁存奇偶校验lp。在错误校正控制信号ecc_ctr被使能的时段期间,错误校正电路250可以通过执行ecc解码操作来产生单比特位错误信号sbe,该单比特位错误信号sbe在锁存数据ld中包括的错误为1比特位时被使能。在错误校正控制信号ecc_ctr被使能的时段期间,错误校正电路250可以通过执行ecc解码操作来产生双比特位错误信号dbe,该双比特位错误信号dbe在锁存数据ld中包括的错误至少为比特2比特时被使能。ecc解码操作可以包括通过使用错误校正码(ecc)检测锁存数据ld中包括的错误并基于检测结果来将锁存数据ld的已经出现错误的比特位反相的操作。ecc解码操作可以包括通过使用错误校正码(ecc)产生奇偶校验的操作,所述奇偶校验包括关于锁存数据ld中包括的错误的信息。

[0038]

寄存器260可以在输入写入控制信号wec和读取控制信号rec的时间点被初始化。在初始化之后,寄存器260可以储存单比特位错误信号sbe和双比特位错误信号dbe。当错误校正测试模式结束并且进入模式寄存器读取操作时,寄存器260可以输出所储存的单比特位错误信号sbe作为单比特位错误信息信号sb_if。当错误校正测试模式结束并进入模式寄存器读取操作时,寄存器260可以输出所储存的双比特位错误信号dbe作为双比特位错误信息信号db_if。寄存器260可以利用储存半导体器件120的操作信息的模式寄存器组(mrs)来实现。

[0039]

当错误校正测试模式被执行时,核心电路270可以将储存在其中的内部数据id输出到输入电路230。当错误校正测试模式结束并且执行正常模式时,核心电路270可以储存从输入电路230输入的内部数据id。当错误校正测试模式结束并且执行正常模式时,核心电路270可以将储存在其中的内部数据id输出到输出电路280。

[0040]

在输出使能信号out_en被使能的时段期间,输出电路280可以从锁存数据ld和锁存奇偶校验lp产生外部数据ed和掩蔽信息信号dmi。在输出使能信号out_en被使能的时段期间,输出电路280可以输出锁存数据ld作为外部数据ed。在输出使能信号out_en被使能的时段期间,输出电路280可以输出锁存奇偶校验lp作为掩蔽信息信号dmi。在输出使能信号out_en被使能的时段期间,输出电路280可以将外部数据ed和掩蔽信息信号dmi输出到控制器110。当错误校正测试模式结束并且进入正常模式时,输出电路280可以从内部数据id产生外部数据ed并将所产生的外部数据ed输出到控制器110。当错误校正测试模式结束并且执行模式寄存器读取操作时,输出电路280可以从单比特位错误信息信号sb_if和双比特位错误信息信号db_if产生外部数据ed,并且可以将所产生的外部数据ed输出到控制器110。

[0041]

图3是示出控制电路220的实施例的配置的框图。如图3所示,控制电路220可以包括缓冲器控制电路221和测试控制电路222。

[0042]

缓冲器控制电路221可以基于写入控制信号wec、读取控制信号rec、写入检查命令wcs和读取检查命令rcs来产生第一锁存使能信号lcenl、第二锁存使能信号lcen2、错误校

正使能信号eccen、输入使能信号in_en和输出使能信号out_en。缓冲器控制电路221可以基于写入控制信号wec、读取控制信号rec、写入检查命令wcs和读取检查命令rcs的逻辑电平来产生第一锁存使能信号lcenl、第二锁存使能信号lcen2、错误校正使能信号eccen、输入使能信号in_en和输出使能信号out_en。

[0043]

测试控制电路222可以基于第一锁存使能信号lcenl、第二锁存使能信号lcen2和错误校正使能信号eccen来产生锁存控制信号lc_ctr和错误校正控制信号ecc_ctr。测试控制电路222可以基于第一锁存使能信号lcenl、第二锁存使能信号lcen2和错误校正使能信号eccen的逻辑电平来产生锁存控制信号lc_ctr和错误校正控制信号ecc_ctr。

[0044]

图4是示出缓冲器控制电路221的实施例的配置的框图。如图4所示,缓冲器控制电路221可以包括输入控制电路221_1和输出控制电路221_2。

[0045]

输入控制电路221_1可以基于写入控制信号wec、读取控制信号rec和写入检查命令wcs来产生第一锁存使能信号lcenl和输入使能信号in_en。输入控制电路221_1可以基于写入控制信号wec、读取控制信号rec和写入检查命令wcs的逻辑电平来产生第一锁存使能信号lcenl和输入使能信号in_en。稍后将参考图5详细描述用于在输入控制电路221_1中产生第一锁存使能信号lcen1和输入使能信号in_en的写入控制信号wec、读取控制信号rec和写入检查命令wcs的逻辑电平。

[0046]

输出控制电路221_2可以基于写入控制信号wec、读取控制信号rec和读取检查命令rcs来产生错误校正使能信号eccen、第二锁存使能信号lcen2和输出使能信号out_en。输出控制电路221_2可以基于写入控制信号wec、读取控制信号rec和读取检查命令rcs的逻辑电平来产生错误校正使能信号eccen、第二锁存使能信号lcen2和输出使能信号out_en。稍后将参考图6详细描述用于在输出控制电路221_2中产生错误校正使能信号eccen、第二锁存使能信号lcen2和输出使能信号out_en的写入控制信号wec、读取控制信号rec和读取检查命令rcs的逻辑电平。

[0047]

图5是示出输入控制电路221_1的实施例的配置的电路图。如图5所示,输入控制电路221_1可以包括与非门(nand)210《1》、210《3》和210《7》,反相器210《2》、210《4》和210《6》,以及或非(nor)门210《5》。

[0048]

当写入控制信号wec被使能为逻辑高电平并且写入检查命令wcs被使能为逻辑高电平时,输入控制电路221_1可以产生被禁止而为逻辑低电平的第一锁存使能信号lcenl。当读取控制信号rec被使能为逻辑高电平并且写入检查命令wcs被使能为逻辑高电平时,输入控制电路221_1可以产生被禁止而为逻辑低电平的第一锁存使能信号lcen1。

[0049]

当写入控制信号wec被使能为逻辑高电平并且写入检查命令wcs被使能为逻辑高电平时,输入控制电路221_1可以产生被使能为逻辑高电平的输入使能信号in_en。当读取控制信号rec被使能为逻辑高电平并且写入检查命令wcs被使能为逻辑高电平时,输入控制电路221_1可以产生被使能为逻辑高电平的输入使能信号in_en。

[0050]

当错误校正测试模式结束并且进入正常模式时,输入控制电路221_1可以通过被使能为逻辑高电平的缓冲器使能信号buf_en来产生被使能为逻辑高电平的输入使能信号in_en。

[0051]

图6是示出输出控制电路221_2的实施例的配置的电路图。如图6所示,输出控制电路221_2可以包括与非门220《1》、220《3》和220《7》,反相器220《2》、220《4》和220《6》,以及或

非门220《5》。

[0052]

当写入控制信号wec被使能为逻辑高电平并且读取检查命令rcs被使能为逻辑高电平时,输出控制电路221_2可以产生被使能为逻辑高电平的错误校正使能信号eccen。当写入控制信号wec和读取检查命令rcs中的任何一个被禁止而为逻辑低电平时,输出控制电路221_2可以产生被禁止而为逻辑低电平的错误校正使能信号eccen。

[0053]

当写入控制信号wec被使能为逻辑高电平并且读取检查命令rcs被使能为逻辑高电平时,输出控制电路221_2可以产生被禁止而为逻辑低电平的第二锁存使能信号lcen2。当读取控制信号rec被使能为逻辑高电平并且读取检查命令rcs被使能为逻辑高电平时,输出控制电路221_2可以产生被禁止而为逻辑低电平的第二锁存使能信号lcen2。

[0054]

当写入控制信号wec被使能为逻辑高电平并且读取检查命令rcs被使能为逻辑高电平时,输出控制电路221_2可以产生被使能为逻辑高电平的输出使能信号out_en。当读取控制信号rec被使能为逻辑高电平并且读取检查命令rcs被使能为逻辑高电平时,输出控制电路221_2可以产生被使能为逻辑高电平的输出使能信号out_en。

[0055]

当错误校正测试模式结束并且进入正常模式时,输出控制电路221_2可以通过被使能为逻辑高电平的缓冲器使能信号buf_en来产生被使能为逻辑高电平的输出使能信号out_en。

[0056]

图7是示出测试控制电路222的实施例的配置的电路图。如图7所示,测试控制电路222可以包括锁存控制信号发生电路222_1和错误校正控制信号发生电路222_2。

[0057]

锁存控制信号发生电路222_1可以利用与非门230《1》来实现。锁存控制信号发生电路222_1可以基于第一锁存使能信号lcen1和第二锁存使能信号lcen2来产生锁存控制信号lc_ctr。当第一锁存使能信号lcen1和第二锁存使能信号lcen2中的任何一个被产生为处于逻辑低电平时,锁存控制信号发生电路222_1可以产生被使能为逻辑高电平的锁存控制信号lc_ctr。当第一锁存使能信号lcen1和第二锁存使能信号lcen2二者都被产生为处于逻辑高电平时,锁存控制信号发生电路222_1可以产生被禁止而为逻辑低电平的锁存控制信号lc_ctr。

[0058]

错误校正控制信号发生电路222_2可以利用反相器230《2》和或非门230《3》来实现。错误校正控制信号发生电路222_2可以基于锁存控制信号lc_ctr和错误校正使能信号eccen来产生错误校正控制信号ecc_ctr。当在锁存控制信号lc_ctr被使能为逻辑高电平的时段期间错误校正使能信号eccen以逻辑低电平而输入时,错误校正控制信号发生电路222_2可以产生被使能为逻辑高电平的错误校正控制信号ecc_ctr。当锁存控制信号lc_ctr以逻辑低电平而输入时,错误校正控制信号发生电路222_2可以产生被禁止而为逻辑低电平的错误校正控制信号ecc_ctr。当错误校正使能信号eccen以逻辑高电平而输入时,错误校正控制信号发生电路222_2可以产生被禁止而为逻辑低电平的错误校正控制信号ecc_ctr。

[0059]

将在下面参考图8和图9以在写入操作中通过使用包括错误的外部数据ed来测试错误校正电路250的操作为例来描述根据本公开的实施例的半导体器件120的错误校正测试模式的操作。

[0060]

首先,将在下面参考图8以在写入操作中接收到包括错误的外部数据ed并且通过校正外部数据ed中包括的错误来产生锁存数据ld的操作为例来描述错误校正测试模式的

操作。

[0061]

命令解码器210可以同步于时钟clk来基于码信号code产生被使能为逻辑高电平的写入控制信号wec。命令解码器210可以同步于时钟clk来基于命令cmd产生被使能为逻辑高电平的写入检查命令wcs。

[0062]

控制电路220可以基于具有逻辑高电平的写入控制信号wec和具有逻辑高电平的写入检查命令wcs来产生被使能为逻辑高电平的输入使能信号in_en。控制电路220可以基于具有逻辑高电平的写入控制信号wec、具有逻辑低电平的读取控制信号rec和具有逻辑低电平的读取检查命令rcs来产生被禁止而为逻辑低电平的输出使能信号out_en。控制电路220可以基于具有逻辑高电平的写入控制信号wec和具有逻辑高电平的写入检查命令wcs产生被使能为逻辑高电平的锁存控制信号lc_ctr。控制电路220可以基于具有逻辑高电平的锁存控制信号lc_ctr、具有逻辑高电平的写入控制信号wec和具有逻辑低电平的读取检查命令rcs来产生被使能为逻辑高电平的错误校正控制信号ecc_ctr。

[0063]

在输入使能信号in_en被使能为逻辑高电平的时段期间,输入电路230可以从内部数据id、外部数据id、外部奇偶校验ep和掩蔽信息信号dmi来产生输入数据in_d、输入奇偶校验in_p和输入掩蔽信号in_dmi。此时,掩蔽信息信号dmi中包括的所有比特位可以以逻辑低电平而输入,以便不阻挡外部数据ed中包括的比特位。

[0064]

在锁存控制信号lc_ctr被使能为逻辑高电平的时段期间,锁存电路240可以通过锁存输入数据in_d、输入奇偶校验in_p和输入掩蔽信号in_dmi来产生锁存数据ld、锁存奇偶校验lp和锁存掩蔽信号ldmi。

[0065]

在错误校正控制信号ecc_ctr被使能为逻辑高电平的时段期间,错误校正电路250可以通过基于锁存数据ld、锁存奇偶校验lp和锁存掩蔽信号ldmi执行ecc解码操作来校正锁存数据ld中包括的错误而产生经校正的数据cd的操作。在错误校正控制信号ecc_ctr被使能的时段期间,错误校正电路250可以通过执行ecc编码操作来产生锁存奇偶校验lp,该锁存奇偶校验lp包括关于锁存数据ld中包括的错误的信息。在错误校正控制信号ecc_ctr被使能的时段期间,错误校正电路250可以通过执行ecc解码操作来产生单比特位错误信号sbe,该单比特位错误信号sbe在锁存数据ld中包括的错误为1比特位时被使能。在错误校正控制信号ecc_ctr被使能的时段期间,错误校正电路250可以通过执行ecc解码操作来产生双比特位错误信号dbe,该双比特位错误信号dbe在锁存数据ld中包括的错误为至少2比特位时被使能。

[0066]

锁存电路240可以在锁存控制信号lc_ctr被使能为逻辑高电平的时段期间将经校正的数据cd重新储存为锁存数据ld。锁存电路240可以在锁存控制信号lc_ctr被使能为逻辑高电平的时段期间重新储存锁存奇偶校验lp。

[0067]

寄存器260可以基于具有逻辑高电平的写入控制信号wec而被初始化,并且在被初始化之后,储存单比特位错误信号sbe和双比特位错误信号dbe。

[0068]

接下来,将在下面参考图9以在写入操作中从得到错误校正的锁存数据ld产生外部数据ed并将该外部数据ed输出到控制器110的操作为例来描述错误校正测试模式的操作。

[0069]

命令解码器210可以同步于时钟clk来基于码信号code产生被使能为逻辑高电平的写入控制信号wec。命令解码器210可以同步于时钟clk来基于命令cmd产生被使能为逻辑

高电平的读取检查命令rcs。

[0070]

控制电路220可以基于具有逻辑高电平的写入控制信号wec、具有逻辑低电平的写入检查命令wcs和具有逻辑低电平的读取控制信号rec来产生被禁止而为逻辑低电平的输入使能信号in_en。控制电路220可以基于具有逻辑高电平的写入控制信号wec和具有逻辑高电平的读取检查命令rcs来产生被使能为逻辑高电平的输出使能信号out_en。控制电路220可以基于具有逻辑高电平的写入控制信号wec和具有逻辑高电平的读取检查命令rcs来产生被使能为逻辑高电平的锁存控制信号lc_ctr。控制电路220可以基于具有逻辑高电平的锁存控制信号lc_ctr、具有逻辑高电平的写入控制信号wec和具有逻辑高电平的读取检查命令rcs来产生被禁止而为逻辑低电平的错误校正控制信号ecc_ctr。

[0071]

因为输入使能信号in_en被禁止而为逻辑低电平,所以输入电路230可以不被驱动。

[0072]

锁存电路240可以在锁存控制信号lc_ctr被使能为逻辑高电平的时段期间将锁存数据ld和锁存奇偶校验lp输出到输出电路280。

[0073]

因为错误校正控制信号ecc_ctr被禁止而为逻辑低电平,所以错误校正电路250可以不被驱动。

[0074]

在输出使能信号out_en被使能为逻辑高电平的时段期间,输出电路280可以从锁存数据ld产生外部数据ed并且可以从锁存奇偶校验lp产生掩蔽信息信号dmi。在输出使能信号out_en被使能为逻辑高电平的时段期间,输出电路280可以将外部数据ed和掩蔽信息信号dmi输出到控制器110。

[0075]

控制器110可以通过接收外部数据ed和掩蔽信息信号dmi来测试半导体器件120中包括的错误校正电路250。当外部数据ed的错误被校正时,控制器110可以确认错误校正电路250执行正常操作。当外部数据ed的错误未被校正时,控制器110可以确认错误校正电路250执行异常操作。

[0076]

根据本公开的实施例,如上所述配置的半导体系统100可以通过以下操作来在错误校正测试模式中测试错误校正电路250:经由半导体器件120中包括的错误校正电路250来校正包括错误的外部数据ed的错误,以及由控制器110检测外部数据ed的错误是否已经被校正。通过在错误校正测试模式中测试半导体器件120中包括的错误校正电路250,半导体系统100可以确保通过错误校正电路250而得到错误校正的数据在正常模式下的可靠性。

[0077]

将在下面参考图10和图11以在数据掩蔽操作中使用不包括错误的内部数据id和外部数据ed来测试错误校正电路250的操作为例来描述根据本公开的实施例的半导体器件120的错误校正测试模式的操作。

[0078]

首先,将在下面参考图10以在数据掩蔽操作中接收到外部数据ed、从不包括错误的内部数据id和外部数据ed产生锁存数据ld、以及锁存数据ld的错误被校正的操作为例来描述错误校正测试模式的操作。

[0079]

命令解码器210可以同步于时钟clk来基于码信号code产生被使能为逻辑高电平的读取控制信号rec。命令解码器210可以同步于时钟clk来基于命令cmd产生被使能为逻辑高电平的写入检查命令wcs。

[0080]

控制电路220可以基于具有逻辑高电平的读取控制信号rec和具有逻辑高电平的写入检查命令wcs来产生被使能为逻辑高电平的输入使能信号in_en。控制电路220可以基

于具有逻辑低电平的写入控制信号wec、具有逻辑高电平的读取控制信号rec和具有逻辑低电平的读取检查命令rcs来产生被禁止而为逻辑低电平的输出使能信号out_en。控制电路220可以基于具有逻辑高电平的读取控制信号rec和具有逻辑高电平的写入检查命令wcs来产生被使能为逻辑高电平的锁存控制信号lc_ctr。控制电路220可以基于具有逻辑高电平的锁存控制信号lc_ctr、具有逻辑低电平的写入控制信号wec和具有逻辑低电平的读取检查命令rcs来产生被使能为逻辑高电平的错误校正控制信号ecc_ctr。

[0081]

核心电路270可以将储存在其中的内部数据id输出到输入电路230。

[0082]

在输入使能信号in_en被使能为逻辑高电平的时段期间,输入电路230可以通过基于掩蔽信息信号dmi阻挡外部数据ed的一些比特位并通过用内部数据id替换外部数据ed的被阻挡的一些比特位来产生输入数据in_d。在输入使能信号in_en被使能的时段期间,输入电路230可以通过缓冲外部奇偶校验ep和掩蔽信息信号dmi来产生输入奇偶校验in_p和输入掩蔽信号in_dmi。此时,掩蔽信息信号dmi中包括的比特位可以被选择性地以逻辑高电平输入,以便阻挡外部数据ed中包括的比特位。

[0083]

在锁存控制信号lc_ctr被使能为逻辑高电平的时段期间,锁存电路240可以通过锁存输入数据in_d、输入奇偶校验in_p和输入掩蔽信号in_dmi来产生锁存数据ld、锁存奇偶校验lp和锁存掩蔽信号ldmi。

[0084]

在错误校正控制信号ecc_ctr被使能为逻辑高电平的时段期间,错误校正电路250可以通过基于锁存数据ld、锁存奇偶校验lp和锁存掩蔽信号ldmi执行ecc解码操作来校正锁存数据ld中包括的错误而产生经校正的数据cd。在错误校正控制信号ecc_ctr被使能的时段期间,错误校正电路250可以通过执行ecc编码操作来产生锁存奇偶校验lp,该锁存奇偶校验lp包括关于锁存数据ld中包括的错误的信息。在错误校正控制信号ecc_ctr被使能的时段期间,错误校正电路250可以通过执行ecc解码操作来产生单比特位错误信号sbe,该单比特位错误信号sbe在锁存数据ld中包括的错误为1比特位时被使能。在错误校正控制信号ecc_ctr被使能的时段期间,错误校正电路250可以通过执行ecc解码操作来产生双比特位错误信号dbe,该双比特位错误信号dbe在锁存数据ld中包括的错误为至少2比特位时被使能。

[0085]

锁存电路240可以在锁存控制信号lc_ctr被使能为逻辑高电平的时段期间将经校正的数据cd重新储存为锁存数据ld。锁存电路240可以在锁存控制信号lc_ctr被使能为逻辑高电平的时段期间重新储存锁存奇偶校验lp。

[0086]

寄存器260可以基于具有逻辑高电平的读取控制信号rec而被初始化,并且在被初始化之后,储存单比特位错误信号sbe和双比特位错误信号dbe。

[0087]

接着,下面将参考图11以从在数据掩蔽操作经错误校正的锁存数据ld产生外部数据ed并将该外部数据ed输出到控制器110的操作为例来描述错误校正测试模式的操作。

[0088]

命令解码器210可以同步于时钟clk来基于码信号code产生被使能为逻辑高电平的读取控制信号rec。命令解码器210可以同步于时钟clk来基于命令cmd产生被使能为逻辑高电平的读取检查命令rcs。

[0089]

控制电路220可以基于具有逻辑低电平的写入控制信号wec、具有逻辑低电平的写入检查命令wcs和具有逻辑高电平的读取控制信号rec来产生被禁止而为逻辑低电平的输入使能信号in_en。控制电路220可以基于具有逻辑高电平的读取控制信号rec和具有逻辑

高电平的读取检查命令rcs来产生被使能为逻辑高电平的输出使能信号out_en。控制电路220可以基于具有逻辑高电平的读取控制信号rec和具有逻辑高电平的读取检查命令rcs来产生被使能为逻辑高电平的锁存控制信号lc_ctr。控制电路220可以基于具有逻辑高电平的锁存控制信号lc_ctr、具有逻辑低电平的写入控制信号wec和具有逻辑高电平的读取检查命令rcs来产生被使能为逻辑高电平的错误校正控制信号ecc_ctr。

[0090]

因为输入使能信号in_en被禁止而为逻辑低电平,所以输入电路230可以不被驱动。

[0091]

在锁存控制信号lc_ctr被使能为逻辑高电平的时段期间,锁存电路240可以将锁存数据ld和锁存奇偶校验lp输出到输出电路280。

[0092]

在输出使能信号out_en被使能为逻辑高电平的时段期间,输出电路280可以从锁存数据ld产生外部数据ed并且可以从锁存奇偶校验lp产生掩蔽信息信号dmi。在输出使能信号out_en被使能为逻辑高电平的时段期间,输出电路280可以将外部数据ed和掩蔽信息信号dmi输出到控制器110。

[0093]

控制器110可以通过接收外部数据ed和掩蔽信息信号dmi来测试半导体器件120中包括的错误校正电路250。当外部数据ed的错误被校正时,控制器110可以确认错误校正电路250执行正常操作。当外部数据ed的错误没有被校正时,控制器110可以确认错误校正电路250执行异常操作。

[0094]

根据本公开的实施例,如上所述配置的半导体系统100可以通过以下操作来在错误校正测试模式中测试错误校正电路250:经由半导体器件120中包括的错误校正电路250来校正包括错误的外部数据ed的错误;以及由控制器110检测外部数据ed的错误是否已被校正。通过在错误校正测试模式下测试半导体器件120包括中的错误校正电路250,半导体系统100可以确保通过错误校正电路250得到错误校正的数据在正常模式下的可靠性。

[0095]

图12是示出根据本公开的实施例的电子系统1000的配置的框图。如图12所示,电子系统1000可以包括主机1100和半导体系统1200。

[0096]

主机1100和半导体系统1200可以通过使用接口协议来相互传输信号。在主机1100和半导体系统1200之间使用的接口协议的示例可以包括mmc(多媒体卡)、esdi(增强型小型磁盘机接口)、ide(集成驱动电子设备)、pci-e(快速外围组件互连)、ata(高级技术附件)、sata(串行ata)、pata(并行ata)、sas(串行附接scsi)和usb(通用串行总线)。

[0097]

半导体系统1200可以包括控制器1300和半导体器件1400(k:1)。控制器1300可以控制半导体器件1400(k:1),以使得半导体器件1400(k:1)执行错误校正测试模式和正常模式。在错误校正测试模式中,半导体器件1400(k:1)中的每一个可以通过错误校正电路来校正包括错误的外部数据ed的错误,并且可以将经错误校正的外部数据ed输出到控制器1300。控制器1300可以通过从每个半导体器件1400(k:1)接收外部数据ed并检测外部数据ed是否得到错误校正来测试错误校正电路。通过在错误校正测试模式下测试半导体器件1400(k:1)中的每一个中包括的错误校正电路,半导体系统1200可以确保通过错误校正电路得到错误校正的数据在正常模式下的可靠性。

[0098]

控制器1300可以利用图1所示的控制器110来实现。半导体器件1400(k:1)中的每一个都可以利用图1和图2所示的半导体器件120来实现。根据实施例,半导体器件1400(k:1)中的每一个可以利用dram(动态随机存取存储器)、pram(相变随机存取存储器)、rram(电

阻随机存取存储器)、mram(磁性随机存取存储器)和fram(铁电随机存取存储器)中的一个来实现。

[0099]

虽然为了说明的目的已经公开了本教导的一些实施例,但是本领域技术人员将理解,在不脱离所附权利要求中定义的本教导的范围和精神的情况下,各种修改、添加和替换是可能的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1