记忆体阵列、其系统及其操作方法与流程

1.本揭露大体上是关于高密度记忆体元件、其系统及其操作方法,且更特定而言,是关于其中安排多个记忆体单元平面来提供三维阵列(包括分隔字线及/或开关以降低位元线电容)的记忆体元件、其系统及其操作方法。

背景技术:

2.计算机、可携式装置、智能手机、物联网装置等电子装置的发展促使对于记忆体元件的需求增加。大体而言,记忆体元件可为挥发性元件及非挥发性元件。挥发性记忆体元件可在提供电力时储存数据,但一旦切断电力则可能丢失所储存的数据。不同于挥发性记忆体元件,非挥发性记忆体元件即使在切断电力之后亦能保留数据,但速率比挥发性记忆体元件慢。

技术实现要素:

3.本揭露的一些实施方式提供一种记忆体阵列,其包含第一组记忆体单元及第一开关。第一组记忆体单元包括第一串记忆体单元及第二串记忆体单元,其各自在记忆体阵列的多个层上延伸,每一层包括:第一串记忆体单元的记忆体单元,其具有耦接至与层关联的第一字线的栅电极;第二组记忆体单元的记忆体单元,其具有耦接至与层关联的第二字线的栅电极。第一开关包括第一电极连接至第一串记忆体单元的多个第一电极及第二串记忆体单元的多个第一电极,及第二电极连接至第一全域位元线。

4.本揭露的一些实施方式提供一种记忆体系统,其包含记忆体阵列以及控制器连接至记忆体阵列。记忆体阵列包括第一组记忆体单元以及第一开关,第一组记忆体单元包括:第一串记忆体单元,具有耦接至第一字线的多个栅电极;及第二串记忆体单元,具有耦接至第二字线的多个栅电极。控制器将切换第一开关,将第一全域位元线电耦接至第一串记忆体单元的多个第一电极及第二串记忆体单元的多个第一电极。控制器将回应于切换第一开关而使用第一字线配置第一串记忆体单元。

5.本揭露的一些实施方式提供操作记忆体阵列的方法,其包含:在第一时间周期内将第一组记忆体单元的多个第一电极耦接至第一全域位元线;在第一时间周期内将第一组记忆体单元的多个第二电极耦接至第一全域选择线,其中第一组记忆体单元包括第一串记忆体单元及第二串记忆体单元;在第一时间周期内将第二组记忆体单元的多个第一电极与第一全域选择线去耦;在第一时间周期内将第二组记忆体单元的多个第二电极与第一全域位元线去耦;及在第一时间周期内,在不存取记忆体单元的第一子集的第二串记忆体单元的栅电极的情况下,存取记忆体单元的第一子集的第一串记忆体单元的栅电极。

附图说明

6.下文参考以下图形或图示详细地描述本解决方案的各个例示性实施例。仅出于图示的目的提供图示,且图示仅描绘本解决方案的例示性实施例,以便于读者理解本解决方

案。因此,图示不应限制本解决方案的广度、范畴或适用性。应指出,出于清晰及易于图示的目的,这些图示未按比例绘制。

7.图1为根据本揭露的实施例的记忆体系统的图;

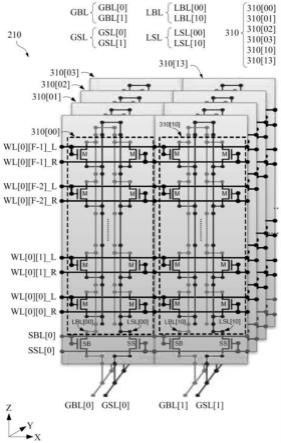

8.图2为展示根据本揭露的实施例的三维记忆体阵列的图;

9.图3a为展示根据一实施例的三维记忆体阵列210的一部分的图,三维记忆体阵列210包括布置于底侧上的开关ss、sb及用于降低电容负载的分割字线;

10.图3b为展示根据一实施例的三维记忆体阵列210的一部分的图,三维记忆体阵列210包括布置于顶侧上的开关ss、sb及用于降低电容负载的分割字线;

11.图4a为展示根据一实施例的三维记忆体阵列210的一部分的图,三维记忆体阵列210包括布置于底侧上的开关ss、sb,分割字线及用于降低电容负载的合并开关sb、ss;

12.图4b为展示根据一实施例的三维记忆体阵列210的部分的图,三维记忆体阵列210包括布置于顶侧上的开关ss、sb,分割字线及用于降低电容负载的合并开关sb、ss;

13.图5为展示根据本揭露的实施例的驱动器的图,驱动器驱动一或多个记忆体;

14.图6为展示根据本揭露的实施例的脉冲的图,脉冲施加至记忆体阵列的开关;

15.图7为展示根据本揭露的实施例的由开关导致电容负载降低的效应的图;

16.图8a为展示根据一实施例的记忆体阵列的例示性实施的图,记忆体阵列包括gsl/gbl连接及单侧开关ss、sb;

17.图8b为展示根据一实施例的记忆体阵列的例示性实施的图,记忆体阵列具有gsl/gbl连接及单侧开关ss、sb;

18.图8c至图8d为展示根据一些实施例的记忆体阵列的例示性实施的图;

19.图8e为展示根据一实施例的记忆体阵列的例示性实施的图,记忆体阵列具有gsl/gbl连接及位于记忆体阵列的顶侧上的单侧开关ss、sb;

20.图8f至图8g为展示根据一些实施例的记忆体阵列的例示性实施的图,对于不同应用,记忆体阵列具有与位元单元大小相关的不同大小的开关sb、ss;

21.图8h为展示hp应用、lp应用及hv应用的例示性实施例的表;

22.图8i为展示根据一实施例的记忆体阵列的例示性实施的图,记忆体阵列具有gsl/gbl连接及位于记忆体阵列的顶侧上的单侧开关ss、sb;

23.图8j至图8k为展示根据一实施例的记忆体阵列的例示性实施的图,记忆体阵列具有gsl/gbl连接及合并选择闸;

24.图8l为从四个不同的视角展示根据一实施例的记忆体阵列的例示性实施的图;

25.图9为展示根据一些实施例的用于存取及/或操作记忆体单元及/或记忆体阵列的方法的流程图;

26.图10为根据本揭露的一些实施例的计算系统1000的例示性方块图。

27.【符号说明】

28.100:记忆体系统

29.105:记忆体控制器

30.110:时序控制器

31.112:位元线控制器

32.114:栅极线控制器

33.120:记忆体阵列

34.125:记忆体单元

35.210:记忆体阵列

36.210a:记忆体阵列

37.210n:记忆体阵列

38.210n-1:记忆体阵列

39.310:子集

40.310[00]:子集

[0041]

310[01]:子集

[0042]

310[02]:子集

[0043]

310[03]:子集

[0044]

310[10]:子集

[0045]

310[13]:子集

[0046]

500:图

[0047]

600:时序图

[0048]

610:高电压

[0049]

620:高电压

[0050]

630:低电压

[0051]

640:低电压

[0052]

700:图

[0053]

710:情况

[0054]

720:情况

[0055]

800a:记忆体阵列

[0056]

800b:记忆体阵列

[0057]

800c:记忆体阵列

[0058]

800d:记忆体阵列

[0059]

800e:记忆体阵列

[0060]

800f:记忆体阵列

[0061]

800g:记忆体阵列

[0062]

800i:记忆体阵列

[0063]

800j:记忆体阵列

[0064]

800k:记忆体阵列

[0065]

800l:记忆体阵列

[0066]

802a:结构

[0067]

802b:结构

[0068]

802e:结构

[0069]

802l:结构

[0070]

804a:结构

[0071]

804b:结构

[0072]

804e:结构

[0073]

806a:结构

[0074]

806b:结构

[0075]

806e:结构

[0076]

806f:结构

[0077]

806i:结构

[0078]

806j:结构

[0079]

806k:结构

[0080]

806l:结构

[0081]

808a:结构

[0082]

808b:结构

[0083]

808e:结构

[0084]

808i:结构

[0085]

810a:结构

[0086]

810b:结构

[0087]

810e:结构

[0088]

810f:结构

[0089]

810i:结构

[0090]

810l:结构

[0091]

811:结构

[0092]

813:结构

[0093]

815:结构

[0094]

817:结构

[0095]

819:结构

[0096]

820a:结构

[0097]

820b:结构

[0098]

820e:结构

[0099]

822a:结构

[0100]

822b:结构

[0101]

822e:结构

[0102]

824a:结构

[0103]

824b:结构

[0104]

824e:结构

[0105]

824l:结构

[0106]

830e:选择区域

[0107]

832e:记忆体单元区域

[0108]

900:方法

[0109]

902:操作

[0110]

904:操作

[0111]

906:操作

[0112]

908:操作

[0113]

910:操作

[0114]

912:操作

[0115]

1000:计算系统

[0116]

1005:主装置

[0117]

1010:记忆体元件

[0118]

1015:输入装置

[0119]

1020:输出装置

[0120]

1025a:接口

[0121]

1025b:接口

[0122]

1025c:接口

[0123]

1030a:cpu核心

[0124]

1030n:cpu核心

[0125]

1035:标准单元应用

[0126]

1040:记忆体控制器

[0127]

1045:记忆体阵列

[0128]

bl:位元线

[0129]

bl0:位元线

[0130]

bl1:位元线

[0131]

blk:位元线

[0132]

db[0]:驱动器

[0133]

db[1]:驱动器

[0134]

ds[0]:驱动器

[0135]

ds[1]:驱动器

[0136]

dw[0]_l:驱动器

[0137]

dw[0]_r:驱动器

[0138]

dw[f-1]_l:驱动器

[0139]

dw[f-1]_r:驱动器

[0140]

gbl:全域位元线

[0141]

gbl[0]:全域位元线

[0142]

gbl[1]:全域位元线

[0143]

gl:栅极线

[0144]

gl0:栅极线

[0145]

gl1:栅极线

[0146]

glj:栅极线

[0147]

gsl:全域选择线

[0148]

gsl[0]:全域选择线

[0149]

gsl[1]:全域选择线

[0150]

lbl:局部位元线

[0151]

lbl[00]:局部位元线

[0152]

lbl[10]:局部位元线

[0153]

lsl:局部选择线

[0154]

lsl[00]:局部选择线

[0155]

lsl[10]:局部选择线

[0156]

m:记忆体单元

[0157]

p1:脉冲

[0158]

p2:脉冲

[0159]

p3:脉冲

[0160]

p4:脉冲

[0161]

sb:开关

[0162]

sbl:开关控制线

[0163]

sbl[0]:开关控制线

[0164]

sbl[1]:开关控制线

[0165]

sl:选择线

[0166]

sml[0]:开关合并控制线

[0167]

ss:开关

[0168]

ssl:开关控制线

[0169]

ssl[0]:开关控制线

[0170]

ssl[1]:开关控制线

[0171]

wl[0][0]_l:字线

[0172]

wl[0][0]_r:字线

[0173]

wl[0][1]_l:字线

[0174]

wl[0][1]_r:字线

[0175]

wl[0][f-1]_l:字线

[0176]

wl[0][f-1]_r:字线

[0177]

wl[0][f-2]_l:字线

[0178]

wl[0][f-2]_r:字线

[0179]

wl[1][0]_l:字线

[0180]

wl[1][0]_r:字线

[0181]

wl[1][f-1]_l:字线

[0182]

wl[1][f-1]_r:字线

[0183]

x:方向

[0184]

y:方向

具体实施方式

[0185]

本文揭示的例示性实施例涉及解决与此项技术中的一或多个问题相关的问题,以及提供其他特征,当结合附图参考以下详细描述时,这些特征将显而易见。根据各个实施

例,本文揭示例示性系统、方法、装置及计算机程序产品。然而,应理解这些实施例仅为实例且不具限制性,且熟悉此项技术者阅读本揭露后将理解可在本揭露的范畴内对所揭示的实施例作出各种修改。

[0186]

以下揭示案提供用于实现所提供标的物的不同特征的许多不同的实施例或实例。为简化本揭露,下文描述部件和布置的特定实例。当然,这些仅为实例,不意欲具有限制性。举例而言,在下文的描述中,在第二特征上方或其上形成第一特征可包括第一及第二特征直接相接触而形成的实施例,亦可包括第一及第二特征之间形成额外特征而使得第一及第二特征并非直接相接触的实施例。此外,本揭露可在各个实例中重复元件符号及/或字母。这种重复是出于简洁和清晰的目的,且本身并未规定所讨论的各个实施例及/或设置之间具有关系。

[0187]

另外,为便于描述,本文可使用诸如“之下”、“下方”、“下部”、“上方”、“上部”及类似者的空间相对性术语,以表述如图中所示的一元件或特征与另一或另一些元件或特征的关系。除图中所描绘的定向外,空间相对性术语意欲涵盖使用中或运行中装置的不同定向。设备可按其他方式经定向(旋转90度或其他定向),因此可类似地解读本文中使用的空间相对性描述词。

[0188]

根据一些实施例,记忆体系统包括一或多个开关(有时称为“选择栅极”)以将局部线与全域线耦接或去耦。局部线可为金属轨道,其连接至两个或更多个记忆体单元。举例而言,局部线可为局部选择线(例如图3a中的lsl[00]或lsl[10]),其连接至记忆体单元的第一电极(例如漏极(或源极)电极)。举例而言,局部线可为局部位元线(例如图3a中的lbl[00]或lbl[10]),其连接至记忆体单元的第二电极(例如源极(或漏极)电极)。全域线可为金属轨道,其可经由开关电耦接至一或多个所选择的局部线。举例而言,全域线可为全域选择线(例如图3a中的gsl[0]),其可经由开关电耦接至两个或更多个局部选择线。举例而言,全域线可为全域位元线(例如图3a中的gbl[0]),其可经由开关电耦接至两个或多个局部位元线。

[0189]

有利地,利用所揭示开关的记忆体系统可具有若干好处。在一态样中,全域线与局部线之间的开关可经单独配置或操作以将各别局部线与全域线电耦接或去耦。通过将所选择的局部线耦接至全域线,连接至所选择局部线的一组记忆体单元的子集可电耦接至全域线,而连接至未选择局部线的此组记忆体单元的另一子集可与全域线电去耦。由此,全域线可具有与此组记忆体单元的所选择子集对应的电容负载,而非与整组记忆体单元对应的电容负载。因此,具有许多记忆体单元的记忆体单元组可经由全域线经配置或操作有对应于记忆体单元组的子集的低电容负载。

[0190]

在另一态样中,可将记忆体阵列中的每一字线分割为两个字线(例如第一字线及第二字线),以在读取及/或写入操作期间进一步降低控制器上的电容负载。通过分割字线,记忆体单元的子集(例如图3a中的子集310)中的一半记忆体单元耦接至第一字线,而另一半耦接至第二字线。

[0191]

通过降低电容负载,可提高记忆体系统的操作速率,同时这又降低记忆体系统的电力消耗。此外,本揭露的技术及/或特征亦可改进路由及屏蔽。

[0192]

1.1.记忆体架构

[0193]

图1为根据本揭露的实施例的记忆体系统100的图。在一些实施例中,将记忆体系

统100实施为集成电路。在一些实施例中,记忆体系统100包括记忆体控制器105及记忆体阵列120。记忆体阵列120可包括以二维或三维阵列布置的多个储存电路或记忆体单元125。每一记忆体单元125可连接至对应的栅极线gl及对应的位元线bl。每一栅极线gl可包括任何导电材料。记忆体控制器105可根据经由栅极线gl及位元线bl的电信号将数据写入至记忆体阵列120或自记忆体阵列120读取数据。在其他实施例中,记忆体系统100包括比图1中所示的元件多或少或数量相同的组件。

[0194]

记忆体阵列120为储存数据的硬件组件。在一态样中,将记忆体阵列120实施为半导体记忆体元件。记忆体阵列120包括多个储存电路或记忆体单元125。在一些实施例中,记忆体阵列120包括栅极线gl0、gl1

…

glj及位元线bl0、bl1

…

blk,每一栅极线沿第一方向延伸,每一位元线沿第二方向延伸。栅极线gl及位元线bl可为导电金属或导电轨道。每一栅极线gl可包括字线及控制线。在一态样中,每一记忆体单元125连接至对应的栅极线gl及对应的位元线bl,且可根据穿过对应栅极线gl及对应位元线bl的电压或电流来操作。在一态样中,每一记忆体单元125可为非挥发性记忆体单元。在一些实施例中,记忆体阵列120包括其他线(例如感测线、参考线、参考控制线、电力轨道等)。

[0195]

记忆体控制器105为控制记忆体阵列120的操作的硬件元件。在一些实施例中,记忆体控制器105包括位元线控制器112、栅极线控制器114及时序控制器110。在一配置中,栅极线控制器114为电路,其经由记忆体阵列120的一或多个栅极线gl提供电压或电流。在一态样中,位元线控制器112为电路,其经由记忆体阵列120的一或多个位元线bl提供电压或电流,且经由一或多个感测线自记忆体阵列120感测电压或电流。在一配置中,时序控制器110为电路,其向栅极线控制器114及位元线控制器112提供控制信号或时钟信号,以同步位元线控制器112及栅极线控制器114的操作。位元线控制器112可连接至记忆体阵列120的位元线bl及感测线,栅极线控制器114可连接至记忆体阵列120的栅极线gl。在一实例中,为将数据写入至记忆体单元125,栅极线控制器114经由连接至记忆体单元125的栅极线gl对记忆体单元125施加电压或电流,且位元线控制器112经由连接至记忆体单元125的位元线bl对记忆体单元125施加对应于待写入数据的电压或电流。在一实例中,为自记忆体单元125读取数据,栅极线控制器114通过连接至记忆体单元125的栅极线gl对记忆体单元125施加电压或电流,且位元线控制器112通过连接至记忆体单元125的感测线或位元线感测对应于由记忆体单元125储存的数据的电压或电流。在一些实施例中,记忆体控制器105包括比图1中所示的组件多或少或数量相同的元件。

[0196]

图2为展示根据一实施例的三维记忆体阵列210a

…

210n的图。在一些实施例中,记忆体阵列120包括记忆体阵列210a

…

210n。每一记忆体阵列210可包括以三维阵列布置的多个记忆体单元125。在一些实施例中,每一记忆体阵列210可包括相同数量的记忆体单元125。在一些实施例中,两个或更多个记忆体阵列210可包括不同数量的记忆体单元125。在一配置中,沿z方向堆叠记忆体阵列210a

…

210n。每一记忆体阵列210可在记忆体阵列210的一侧上具有位元线bl,在记忆体阵列210的对侧上具有选择线sl。在一些实施例中,两个相邻的记忆体阵列210可共享选择线sl。在一些实施例中,两个相邻的记忆体阵列210可共享位元线bl。举例而言,记忆体阵列210n-1、210n共享一组选择线sl或电耦接至此组选择线sl。举例而言,记忆体阵列210n-2、210n-1共享一组位元线bl或电耦接至此组位元线bl。通过共享选择线sl及/或位元线bl,可减少经由选择线sl及/或位元线bl施加信号的记忆体控

制器105的驱动器的数量,以实现面积效率。在一些实施例中,记忆体阵列120包括其他记忆体阵列,其具有与图2中所示的选择线sl及/或位元线bl不同的选择线sl及/或位元线bl。

[0197]

2.具有开关及/或分割字线的记忆体系统

[0198]

图3a为展示根据一实施例的三维记忆体阵列210的一部分的图,三维记忆体阵列210包括布置于底侧上的开关ss、sb及用于降低电容负载的分割字线。在图3a中,记忆体阵列210包括第一组记忆体单元及第二组记忆体单元。在一配置中,第一组记忆体单元包括记忆体单元的子集3100.…

310[03],其可电耦接至沿y方向延伸的全域位元线gbl[0]及全域选择线gsl[0]。在一配置中,第二组记忆体单元包括记忆体单元的子集310[10]

…

310[13],其可电耦接至沿y方向延伸的全域位元线gbl[1]及全域选择线gsl[1]。记忆体单元的每一子集310可包括沿z方向安置的f个记忆体单元m(记忆体单元125),其中f亦对应于记忆体阵列210中平层或层的总数。每一组记忆体单元可包括沿y方向比图3a中所示的记忆体单元数量多的记忆体单元子集310。记忆体阵列210可包括比图3a中所示的沿x方向堆叠的记忆体单元组数量更多的记忆体单元组。通过如图3a所示布置记忆体单元,可增加记忆体阵列210的储存密度。

[0199]

在一配置中,子集310的一或多个记忆体单元可位于子集310的左侧,子集310的其他记忆体单元可位于子集310的右侧。在一配置中,子集310可包括沿z方向安置的第一垂直串记忆体单元及沿z方向安置的第二垂直串记忆体单元,其中第一垂直串与第二垂直串相互平行。可根据在子集310中的位置及在记忆体阵列210中的x-y-z位置来识别(例如索引、参考、标记等)每一记忆体单元。举例而言,如图3a所示,子集310[00]包括m[0][0][0]_l、m[0][0][0]_r、m[0][0][1]_l、m[0][0][1]_r、m[0][0][f-2]_l、m[0][0][f-2]_r、m[0][0][f]_l及m[0][0][f]_r,子集310[10]包括m[1][0][0]_l、m[1][0][0]_r、m[1][0][1]_l、m[1][0][1]_r、m[1][0][f-2]_l、m[1][0][f-2]_r、m[1][0][f]_l及m[1][0][f]_r。

[0200]

每一记忆体单元m可为挥发性记忆体单元、非挥发性记忆体单元或可储存数据的任何记忆体单元。每一记忆体单元m可实施为晶体管,诸如金属氧化物半导体场效晶体管(mosfet)、环绕式栅极fet(gaafet)或鳍式场效晶体管(finfet)。每一记忆体单元m可包括耦接至局部选择线lsl[x][y]的第一电极(例如漏电极)、耦接至局部位元线lbl[x][y]的第二电极(例如源电极)及耦接至对应字线(例如wl[x][z]_l或字线wl[x][z]_r)的第三电极(例如栅电极)。每一记忆体单元m可根据施加至记忆体单元m的栅电极的电压储存数据或传导电流。

[0201]

在一配置中,在局部选择线lsl与局部位元线lbl之间平行连接记忆体单元m的子集310。局部选择线lsl可为金属轨道,记忆体单元子集310的第一电极(例如漏电极)可在此金属轨道处连接。局部位元线lbl可为金属轨道,记忆体单元子集310的第二电极(例如源电极)可在此金属轨道处连接。局部选择线lsl可沿z方向延伸,且连接至对应的开关ss。类似地,局部位元线lbl可沿与局部位元线lbl平行的z方向延伸且连接至对应的开关sb。

[0202]

可将字线wl[x][y]分割(例如分离、划分、分隔等)为wl[x][y]_l(左)及wl[x][y]_r(右),且使其沿x方向延伸,以将不同组中对应的记忆体单元m的栅电极连接至记忆体控制器(例如栅极线控制器114)。在一配置中,wl[x][y]_l连接至位于子集310左侧上的记忆体单元m的栅电极,wl[x][y]_r连接至位于子集310右侧上的记忆体单元m的栅电极。在一配置中,wl[x][y]_l连接至位于多个子集(例如子集310[00]、310[10])左侧上的记忆体单元m的

栅电极,wl[x][y]_r连接至位于多个子集(例如子集310[00]、310[10])右侧上的记忆体单元m的栅电极。在一配置中,将字线wl[x][y]分割为两个字线(例如wl[x][y]_l及wl[x][y]_r),此两个字线分别为沿记忆体阵列210的x方向的每一子集310的记忆体单元m(左或右)专用的。

[0203]

举例而言,如图3a所示,wl[0][0]_l连接至m[0][0][0]_l(例如位于子集310[00]的左侧上的记忆体单元m)的栅电极及m[1][0][0]_l(例如位于子集310[10]的左侧上的记忆体单元m)的栅电极,wl[0][0]_r连接至m[0][0][0]_r(例如位于子集310[00]的右侧上的记忆体单元m)的栅电极及m[1][0][0]_r(例如位于子集310[10]的右侧上的记忆体单元m)的栅电极,wl[0][1]_l连接至m[0][0][1]_l的栅电极及m[1][0][1]_l的栅电极,wl[0][1]_r连接至m[0][0][1]_r的栅电极及m[1][0][1]_r的栅电极,wl[0][f-2]_l连接至m[0][0][f-2]_l的栅电极及m[1][0][f-2]_l的栅电极,wl[0][f-2]_r连接至m[0][0][f-2]_r的栅电极及m[1][0][f-2]_r的栅电极,wl[0][f-1]_l连接至m[0][0][f-1]_l的栅电极及m[1][0][f-1]_l的栅电极,wl[0][f-1]_r连接至m[0][0][f-1]_r的栅电极及m[1][0][f-1]_r的栅电极。

[0204]

在一配置中,虽然图3a未展示,但可调换wl[x][y]_l及wl[x][y]_r的连接,wl[x][y]_l连接至位于多个子集(例如子集310[00]、310[10])右侧上的记忆体单元m的栅电极,wl[x][y]_r连接至位于多个子集(例如子集310[00]、310[10])左侧上的记忆体单元m的栅电极。举例而言,wl[0][0]_l连接至m[0][0][0]_r(例如位于子集310[00]右侧上的记忆体单元m)的栅电极及m[1][0][0]_r(例如位于子集310[10]右侧上的记忆体单元m)的栅电极,wl[0][0]_r连接至m[0][0][0]_l(例如位于子集310[00]左侧上的记忆体单元m)的栅电极及m[1][0][0]_l(例如位于子集310[10]左侧上的记忆体单元m)的栅电极,诸如此类。

[0205]

将字线wl[x][y]分割为两个字线(例如wl[x][y]_l及wl[x][y]_r)可降低位元线(例如lbl[x][y]或gbl[x][y])上的电容负载,由此允许记忆体阵列210维持各种记忆体应用(例如储存)需要的大单元位元数,且没有额外的处理成本。

[0206]

每一开关sb可实施为晶体管(例如mosfet、gaafet、finfet等)。每一开关sb可包括连接至局部位元线lbl的第一电极(例如漏电极)、连接至对应的全域位元线gbl的第二电极(例如源电极)及连接至对应的开关控制线sbl(有时称为“左选择闸”或“sg[x]_l”)的第三电极(例如栅电极)。开关控制线sbl可为金属轨道,其沿x方向延伸以将记忆体控制器105(例如栅极线控制器114)连接至开关sb的栅电极。根据经由开关控制线sbl施加的电压或信号,可切换(例如启用或禁用)连接至开关控制线sbl的一或多个开关sb。举例而言,回应于经由开关控制线sbl提供的对应于逻辑状态

‘1’

的电压,可启用开关sb,以将记忆体单元的子集310的第二电极(例如源电极)电耦接(例如连接、接合等)至全域位元线gbl。举例而言,回应于经由开关控制线sbl提供的对应于逻辑状态

‘0’

的电压,可禁用开关sb,以将记忆体单元的子集310的第二电极(例如源电极)与全域位元线gbl电去耦(例如断接、切断等)。

[0207]

每一开关ss可实施为晶体管(例如mosfet、gaafet、finfet等)。开关ss可包括连接至局部选择线lsl的第一电极(例如源电极)、连接至对应的全域选择线gsl的第二电极(例如漏电极)及连接至对应的开关控制线ssl(有时称为“右选择闸”或“sg[x]_r”)的第三电极(例如栅电极)。开关控制线ssl可为金属轨道,其沿x方向延伸以将记忆体控制器105(例如栅极线控制器114)连接至开关ss的栅电极。根据通过开关控制线ssl施加的电压或信号,可

启用或禁用连接至开关控制线ssl的一或多个开关ss。举例而言,回应于经由开关控制线ssl提供的对应于逻辑状态

‘1’

的电压,可启用开关ss,以将记忆体单元的子集310的第一电极(例如漏电极)电耦接至全域选择线gsl。举例而言,回应于经由开关控制线ssl提供的对应于逻辑状态

‘0’

的电压,可禁用开关ss,以将记忆体单元的子集310的第一电极(例如漏电极)自全域选择线gsl电去耦。

[0208]

在一配置中,全域选择线gsl为金属轨道,对应的开关ss在此处连接。全域选择线gsl可沿y方向延伸。在一实施中,全域选择线gsl可连接至记忆体控制器105(例如位元线控制器112)。全域位元线gbl可为金属轨道,对应的开关sb在此处连接。全域位元线gbl可沿平行于全域选择线gsl的y方向延伸。在一实施中,全域位元线gbl可连接至记忆体控制器105(例如位元线控制器112)。

[0209]

开关sb、ss位于记忆体阵列210的同一侧上,以降低处理成本及/或处理复杂度。举例而言,如图3a所示,开关sb、ss位于及/或布置于记忆体阵列210的底侧上。在一配置中,开关sb、ss可位于记忆体阵列210的顶侧上。举例而言,图3b为展示根据一实施例的三维记忆体阵列210的部分的图,三维记忆体阵列210包括布置于顶侧上的开关ss、sb及用于降低电容负载的分割字线。

[0210]

重新参考图3a,在一配置中,可根据记忆体控制器105(例如栅极线控制器114)的电压或信号操作或配置开关sb、ss,以将记忆体单元的子集310选择性电耦接(有时称为“耦接方法”)至对应的全域线bl、sl。举例而言,自连接至局部选择线lsl[x0]

…

lsl[x3]及局部位元线lbl[x0]

…

lbl[x3]的一组记忆体单元310[x0]

…

310[x3],连接至局部选择线lsl[xy]及局部位元线lbl[xy]的记忆体单元的子集310[xy]可经由所选择的开关sb、ss电耦接至全域位元线gbl[x]及全域选择线gsl[x]。同时,连接至其他局部选择线lsl及局部位元线lbl的记忆体单元的其他子集310可自全域位元线gbl[x]及全域选择线gsl[x]电去耦(有时称为“去耦方法”)。通过将记忆体单元的所选择子集310[xy]经由开关sb、ss电耦接至全域位元线gbl[x]及全域选择线gsl[x],全域位元线gbl[x]及全域选择线gsl[x]可具有对应于记忆体单元的所选择子集310[xy]而非记忆体单元的子集310[x1]

…

310[x3](例如多个或所有)的电容负载。因此,可实施全域位元线gbl[x]及全域选择线gsl[x],以在不增加电容负载的情况下提供电压或电流。

[0211]

分割字线允许记忆体控制器105存取(例如读取、写入、程序化)子集310中的单个垂直串记忆体单元,而不许存取子集310中的所有垂直串记忆体单元。举例而言,子集310[00]可包括:沿z方向安置的第一垂直串记忆体单元(例如m[0][0][0]_l、m[0][1][0]_l、m[0][f-2][0]_l、m[0][f-1][0]_l),其中第一垂直串中的每一记忆体单元m的栅电极耦接至对应的字线wl[x][z]_l(左);及沿z方向安置的第二垂直串记忆体单元(例如m[0][0][0]_r、m[0][1][0]_r、m[0][f-2][0]_r、m[0][f-1][0]_r),其中第二垂直串中的每一记忆体单元m的栅电极耦接至对应的字线wl[x][z]_r(右)。在此配置中,记忆体控制器105可(1)使用本文所讨论的“耦接”方法经由开关sb、ss选择记忆体单元的子集310[00],且(2)使用本文所讨论的“去耦方法”经由开关sb、ss取消选择记忆体单元的其他子集310。回应于选择/取消选择记忆体单元的子集310,控制器105可经由字线wl[x][y]_l(左)存取第一垂直串记忆体单元,而不许亦存取子集310中的第二垂直串记忆体单元。因此,将字线wl[x][y]分割为两个字线(例如wl[x][y]_l及wl[x][y]_r)可进一步有助于降低字线wl[x][y]上的电容负

载,由此允许以更快的速度及/或更低的电力消耗操作或配置控制器105及/或记忆体单元m。

[0212]

在一些实施例中,记忆体阵列210包括开关sb、ss中的任一者,但可能缺少开关sb、ss中的另一者。举例而言,记忆体阵列210包括如图3a所示的开关sb,其中省去开关ss,局部选择线lsl[x0]、[x1]、[x2]、[x3]连接至对应的全域选择线sl[x]。举例而言,记忆体阵列210包括如图3a所示的开关ss,其中省去开关sb,局部位元线lbl[x0]、[x1]、[x2]、[x3]连接至对应的全域位元线gbl[x]。可配置或操作开关ss或sb以将记忆体单元的子集310选择性电耦接至对应的全域线或与对应的全域线电去耦。在一些实施例中,记忆体阵列210可包括分割字线wl及开关sb、ss中的任一者,但可能缺少开关sb、ss中的另一者。

[0213]

在一配置中,可将记忆体单元的子集310的开关sb的栅电极电耦接至对应的开关ss的栅电极。换言之,开关sb及/或其各别的功能可与开关ss及/或其各别的功能合并。举例而言,图4a为展示根据一实施例的三维记忆体阵列210的一部分的图,三维记忆体阵列210包括布置于底侧上的开关ss、sb,分割字线及用于降低电容负载的合并开关sb、ss。作为另一实例,图4b为展示根据一实施例的三维记忆体阵列210的一部分的图,三维记忆体阵列210包括布置于顶侧上的开关ss、sb,分割字线及用于降低电容负载的合并开关sb、ss。如图4a及图4b所示,当将开关sb、ss的栅电极电耦接在一起(合并)时,可将对应的开关控制线ssl[y]、sbl[y]合并为连接至单一驱动器的单一控制线(在图4b中示为开关合并控制线或sml[0])。因此,可根据来自驱动器的电压、电流或脉冲同时(或几乎同时)启用或禁用连接至sml[0]的开关sb、ss。通过实施同一(单一)驱动器以配置或操作开关sb、ss,可减少若干驱动器以实现面积效率。

[0214]

在一些实施例中,可将图3a、图3b、图4a、图4b中的任一者中描绘的记忆体阵列210中的记忆体单元m及开关sb、ss实施为p型金属氧化物半导体场效晶体管(pmos)。在一些实施例中,可将图3a、图3b、图4a、图4b中的任一者中描绘的记忆体阵列210中的记忆体单元m及开关sb、ss实施为n型金属氧化物半导体场效晶体管(nmos)。

[0215]

图5为展示根据本揭露的实施例的驱动器的图,驱动器驱动一或多个记忆体。图500包括驱动器ds[0]、db[0]、ds[1]、db[1]、dw[0]_l

…

dw[f-1]_l及dw[0]_r

…

dw[f-1]_r。驱动器ds[0]、db[0]、ds[1]、db[1]、dw[0]_l

…

dw[f-1]_l及dw[0]_r

…

dw[f-1]_r可为栅极线控制器114的一部分。在一态样中,将驱动器ds[0]、db[0]、ds[1]、db[1]、dw[0]_l

…

dw[f-1]_l及/或dw[0]_r

…

dw[f-1]_r连接至两个或更多个开关或两个或更多个记忆体单元,以实现面积效率。

[0216]

在一配置中,可经由开关控制线ssl[1]将连接至记忆体单元的子集310[01]的开关ss的栅电极连接至驱动器ds[1]的输出。在一配置中,可经由开关控制线ssl[0]将连接至记忆体单元的子集310[00]的开关ss的栅电极连接至驱动器ds[0]的输出。在一配置中,可经由开关控制线sbl[1]将连接至记忆体单元的子集310[01]的开关sb的栅电极连接至驱动器db[1]的输出。在一配置中,可经由开关控制线sbl[0]将连接至记忆体单元的子集310[00]的开关sb的栅电极连接至驱动器db[0]的输出。

[0217]

在一配置中,经由字线wl将记忆体单元的子集310[00]的每一记忆体单元的栅电极及记忆体单元的子集310[01]的对应记忆体单元的栅电极连接至驱动器dw[x]_l或dw[x]_r的输出。举例而言,经由字线wl[0][0]_l、wl[1][0]_l将位于记忆体单元的子集310

[00]左侧上的第一记忆体单元的栅电极及位于记忆体单元的子集310[01]左侧上的第一记忆体单元的栅电极连接至驱动器dw[0]_l的输出。作为另一实例,经由字线wl[0][0]_r、wl[1][0]_r将位于记忆体单元的子集310[00]右侧上的第一记忆体单元的栅电极及位于记忆体单元的子集310[01]右侧上的第一记忆体单元的栅电极连接至驱动器dw[0]_r的输出。作为另一实例,经由字线wl[0][f-1]_l、wl[1][f-1]_l将位于记忆体单元的子集310[00]左侧上的第f记忆体单元的栅电极及位于记忆体单元的子集310[01]左侧上的第f记忆体单元的栅电极连接至驱动器dw[f-1]_l的输出。作为另一实例,经由字线wl[0][f-1]_r、wl[1][f-1]_r将位于记忆体单元的子集310[00]右侧上的第f记忆体单元的栅电极及位于记忆体单元的子集310[01]右侧上的第f记忆体单元的栅电极连接至驱动器dw[f-1]_r的输出。虽然图5展示记忆体单元的两个子集310[01]、310[00],但可经由字线将每一驱动器(例如dw_l及/或dw_r)的输出连接至其他子集(例如310[02]、310[03])中的其他记忆体单元。

[0218]

在不实施所揭示开关ss、sb且共享驱动器(例如ds、db、dw_l及/或dw_r)的情况下,驱动器的数量可对应于一组记忆体单元中的总记忆体单元的数量。通过共享驱动器(例如ds、db、dw_l及/或dw_r)以驱动记忆体单元的不同子集310中的多个记忆体单元,可减少若干驱动器以实现面积效率。因此,可通过共享驱动器实现面积减小68%。

[0219]

图6为根据一实施例的时序图600,其展示用于操作记忆体阵列120的脉冲p1、p2、p3、p4。在一些实施例中,记忆体控制器105(例如栅极线控制器114)产生脉冲p1、p2、p3、p4。

[0220]

在一方法中,将脉冲p1施加至开关ss、sb(连接至记忆体单元的所选择子集310)的栅电极,将脉冲p3施加至开关ss、sb(连接至记忆体单元的未选择子集310)的栅电极。通过施加具有高电压610的脉冲p1,可启用连接至记忆体单元的所选择子集310的开关ss、sb,以将记忆体单元的所选择子集310电耦接至全域选择线gsl及全域位元线gbl。同时,通过施加具有低电压630的脉冲p3,可禁用连接至记忆体单元的未选择子集310的开关ss、sb,以将记忆体单元的未选择子集310与全域选择线gsl及全域位元线gbl电去耦。因此,全域选择线gsl及全域位元线gbl可具有电容负载,此电容负载对应于记忆体单元的所选择子集而非整组记忆体单元。

[0221]

在一方法中,将脉冲p2施加至所选择记忆体单元的栅电极或字线wl,将脉冲p4施加至未选择记忆体单元的栅电极或字线wl。举例而言,当选择子集310的第一垂直串(例如最左的)时,将脉冲p2施加至wl[x][z]_l,当取消选择子集310的第二垂直串(例如最右的)时,将脉冲p4施加至wl[x][z]_r。作为另一实例,当选择子集310的第二垂直串(例如最右的)时,将脉冲p2施加至wl[x][z]_r,当取消选择子集310的第一垂直串(例如最左的)时,将脉冲p4施加至wl[x][z]_l。

[0222]

在一些实施例中,脉冲p1可具有比脉冲p2的脉宽(脉冲的上升边缘与下降边缘之间的经过时间)宽的脉宽。在一些实施例中,脉冲p1可具有比脉冲p2的脉宽窄的脉宽(脉冲p1的上升边缘与下降边缘之间的经过时间)。在一实施例中,脉冲p1可具有与脉冲p2的脉宽相同的脉宽(脉冲p1的上升边缘与下降边缘之间的经过时间)。

[0223]

在一些实施例中,脉冲p1的上升边缘及/或下降边缘可与脉冲p2的上升边缘及/或下降边缘重合。在一些实施例中,相对于脉冲p2的对应上升边缘及/或对应下降边缘,脉冲p1的上升边缘及/或下降边缘可延迟。在一些实施例中,相对于脉冲p2的对应上升边缘及/或对应下降边缘,脉冲p1的上升边缘及/或下降边缘可提前。

[0224]

通过施加具有高电压620的脉冲p2,所选择的记忆体单元可经程序化或传导对应于程序化数据的电流。同时,通过施加具有低电压640的脉冲p4,可禁止未选择的记忆体单元经格式化或传导电流。因此,可个别地程序化或操作记忆体单元的子集310中的所选择记忆体单元。

[0225]

图7为根据一实施例的图700,其展示由开关ss、sb导致电容负载降低的效应。f可表示记忆体单元子集中沿z方向的若干记忆体单元。s可表示沿x方向的若干组记忆体单元(或一些全域选择线gsl)。在一态样中,如情况710所示,在不实施所揭示的开关ss、sb及/或分割字线的情况下,全域线的电容负载可根据记忆体单元子集的数量增加。举例而言,在没有所揭示的开关ss、sb及/或分割字线的情况下,如记忆体阵列210包括记忆体单元的64个子集,则全域线可具有高电容负载715。通过实施开关sw(例如ss、sb)及/或分割字线,如情况720所示,虽然记忆体单元子集的数量增加,但全域线的电容负载可不增加。举例而言,通过启用连接至记忆体单元的所选择子集310的开关ss、sb及禁用连接至记忆体单元的未选择子集310的开关ss、sb,全域线可具有电容负载,此电容负载对应于记忆体单元的所选择子集310。因此,记忆体单元子集的数量增加不影响全域线的电容负载。

[0226]

图8a为根据一实施例的图,其展示记忆体阵列的例示性实施,此记忆体阵列具有gsl/gbl连接及单侧开关ss、sb。如图8a所示,记忆体阵列800a包括为全域位元线gbl连接而实施的结构802a(例如s/bl连接)。记忆体阵列800a包括为全域选择线gsl连接而实施的结构804a(例如s/bl连接)。记忆体阵列800a亦可包括为开关(ss、sb)而实施的结构806a(例如sl/bl),例如晶体管通道。如所示,开关位于记忆体阵列800a的底侧上。记忆体阵列800a亦可包括为非分割字线而实施的结构808a(例如互连)。记忆体阵列800a亦可包括为位元单元而实施的结构810a(例如wl),例如晶体管。记忆体阵列800a亦可包括对应于铁电(fe)膜的结构820a。记忆体阵列800a亦可包括对应于氧化物(例如sio2)的结构822a。记忆体阵列800a亦可包括为通道而实施的结构824a。在此配置中,记忆体阵列800a可具有对应于以下方程式的单元数:

[0227]

(1)单元数=列数*1/2*行数*层数;

[0228]

其中列数对应于记忆体阵列中列(y方向)的数量,行数对应于记忆体阵列中行(x方向)的数量,层数对应于记忆体阵列中层(z方向)的数量。

[0229]

在一些实施例中,将wl定义为vg的字线。在一些实施例中,z方向上wl的尺寸可为20纳米至120纳米。在一些实施例中,将s/bl定义为第一电力轨道(例如vdd)及第二电力轨道(例如接地)的源极线/位元线。在一些实施例中,将ox定义为用于隔离的氧化物。在一些实施例中,将fe定义为记忆体的铁电膜。在一些实施例中,fe具有5纳米至30纳米的厚度。在一些实施例中,通道对应于记忆体的通道膜。在一些实施例中,通道具有5纳米至30纳米的厚度。在一些实施例中,s/bl对应于互连。

[0230]

图8b为展示根据一实施例的记忆体阵列的例示性实施的图,此记忆体阵列具有gsl/gbl连接及单侧开关ss、sb。如图8b所示,记忆体阵列800b包括为全域位元线gbl连接而实施的结构802b。记忆体阵列800b包括为全域选择线gsl连接而实施的结构804b。记忆体阵列800b亦可包括为开关(ss、sb)而实施的结构806b,例如晶体管通道。如图所示,开关位于记忆体阵列800b的底侧上。记忆体阵列800b亦可包括为分割字线(例如分割为第一字线及第二字线的字线)而实施的结构808b(例如互连)。记忆体阵列800b亦可包括为位元单元而

实施的结构810b(例如wl),例如晶体管。记忆体单元800b亦可包括对应于铁(fe)的结构820b。记忆体单元800b亦可包括对应于氧化物(例如sio2)的结构822b。记忆体单元800b亦可包括为通道而实施的结构824b。在此配置中,记忆体阵列800b可具有对应于以下方程式的单元数:

[0231]

(2)单元数=列数*行数*层数

[0232]

图8c至图8d为展示根据一些实施例的记忆体阵列的例示性实施的图。记忆体阵列800c及800d包括结构811,其可包括铁(fe)。记忆体阵列800c及800d包括结构813,其可对应于通道。记忆体阵列800c及800d包括结构815,其可对应于选择线sl(或全域选择线gsl)及/或位元线bl(或全域位元线gbl)。记忆体阵列800c及800d包括结构817,其可包括氧化物。记忆体阵列800c及800d包括结构819,其可对应于字线wl。

[0233]

在一实施例中,用于制造具有gsl/gbl连接及单侧开关ss、sb的记忆体阵列的制程流程可包括以下操作:堆叠、单元面积干蚀刻、置换氮化硅(sin)、字线wl金属填充、铁(fe)/通道/氧化物沉积、形成全域选择线gsl及全域位元线gnl及触点/通孔。在一实施例中,制程流程可包括以下操作:堆叠、单元面积干蚀刻、置换sin、氧化物填充(用于分割字线wl)、字线wl金属填充、fe/通道/氧化物沉积、形成全域选择线gsl及全域位元线gbl及触点/通孔。在一实施例中,制程流程可包括以下操作:堆叠、单元面积干蚀刻、短长度的置换sin、字线wl金属填充、fe/通道/氧化物沉积、形成全域选择线gsl及全域位元线gbl及触点/通孔。在一实施例中,可修改及/或调整制程流程,在字线wl之前包括额外的氧化物填充,以分割字线wl。在一实施例中,可修改及/或调整制程流程,以包括短长度的置换sin移除。

[0234]

图8e为展示根据一实施例的记忆体阵列的例示性实施的图,此记忆体阵列具有gsl/gbl连接及位于记忆体阵列的顶侧上的单侧开关ss、sb。记忆体阵列800e包括为全域位元线gbl连接而实施的结构802e(例如s/bl连接)。记忆体阵列800e包括为全域选择线gsl连接而实施的结构804e(例如s/bl连接)。记忆体阵列800e亦可包括为开关(ss、sb)而实施的结构806e(例如sl/bl),例如晶体管通道。如图所示,开关位于记忆体阵列800e的顶侧上。记忆体阵列800e亦可包括为分割字线(例如分割为两个字线的字线)而实施的结构808e。记忆体阵列800e亦可包括为位元单元而实施的结构810e,例如晶体管。记忆体单元800e亦可包括对应于铁(fe)的结构820e。记忆体单元800e亦可包括对应于氧化物(例如sio2)的结构822e。记忆体单元800e亦可包括为通道而实施的结构824e。记忆体阵列800e包括选择区域830e及记忆体单元区域832e。

[0235]

图8f至图8g为展示根据一些实施例的记忆体阵列的例示性实施的图,对于不同应用,此记忆体阵列具有与位元单元大小相关的不同大小的开关sb、ss。记忆体阵列800f及800g分别包括为选择闸(例如开关ss、sb)而实施的结构806f(例如sg wl)及806g。记忆体阵列800f及800g亦可包括为位元单元而实施的结构810f及810g(例如cell wl)。

[0236]

如图8f所示,根据一实施例,选择闸(例如开关sb、ss)的结构806f在垂直维度(例如z维)上的尺寸大于位元单元的结构810f在垂直维度上的尺寸。举例而言,选择闸(例如开关sb、ss)的结构806f在垂直维度(例如z维)上的尺寸可为位元单元的结构810f在垂直维度上的尺寸的1.5至3倍。在此配置中,对于hp应用,选择闸可具有较薄的氧化物(例如sio2)及/或变为lk氧化物。在一些实施例中,将hp应用界定为hpc产品,例如ai计算装置,其对于数据储存需要高频宽、高容量。

[0237]

如图8g所示,根据一实施例,选择闸(例如开关sb、ss)的结构806g在垂直维度(例如z维)上的尺寸小于位元单元的结构810g在垂直维度上的尺寸。举例而言,选择闸的结构806g在垂直维度上的尺寸可为位元单元的结构810g在垂直维度上的尺寸的0.5x至0.2x。在此配置中,对于hv应用,选择闸可具有较厚的氧化物(例如sio2)及/或选择闸的材料可变为任何其他材料。在一些实施例中,将hv应用界定为电源供应器、马达控制器。在一些实施例中,选择闸(例如开关sb、ss)可与位元单元具有相同的尺寸。在一些实施例中,hp及/或hv元件的氧化物可为栅极氧化物。在一些实施例中,hp元件将使用较薄的栅极氧化物,hv元件将使用较厚的栅极氧化物。在一些实施例中,hp元件可将氧化物变为lk氧化物,并且亦可改进效能。

[0238]

图8h为展示hp应用、lp应用及hv应用的例示性实施例的表。在一实施例中,hp产品可为hpc或人工智能(ai)计算装置。在一实施例中,选择闸(例如开关sb、ss)的结构806f(例如sg wl)在垂直维度(例如z维)上的尺寸可大于位元单元的结构810f(例如cell wl)在垂直维度上的尺寸。在一实施例中,sg元件可具有较薄的栅极氧化物。在一实施例中,sg元件可将lk用作隔离ox。

[0239]

在一实施例中,lp产品可为一或多个智能电话晶片。在一实施例中,选择闸(例如开关sb、ss)的结构806f(例如sg wl)在垂直维度(例如z维)上的尺寸可小于位元单元的结构810f(例如cell wl)在垂直维度上的尺寸。

[0240]

在一实施例中,hv产品可为hpc或人工智能(ai)计算装置。在一实施例中,sg元件可具有较厚的栅极氧化物。

[0241]

图8i为展示根据一实施例的记忆体阵列的例示性实施的图,此记忆体阵列具有gsl/gbl连接及位于记忆体阵列的顶侧上的单侧开关ss、sb。记忆体阵列800i包括为全域位元线gbl连接而实施的结构802i(例如s/bl连接)。记忆体阵列800i包括为全域选择线gsl连接而实施的结构804i(例如s/bl连接)。记忆体阵列800i亦可包括为开关(ss、sb)而实施的结构806i,例如晶体管通道。记忆体阵列800i亦可包括为非分割字线而实施的结构808i。记忆体阵列800i亦可包括为位元单元而实施的结构810i(例如wl),例如晶体管。在一些实施例中,可根据字线wl的厚度分割或不分割字线wl(例如结构810i)。在一些实施例中,记忆体阵列800i的不同层(例如z方向上的层)可为不同的有效字线wl(例如结构810i)。在一些实施例中,强离子位元(ion bit)单元可使用大的有效宽度。在一些实施例中,低离子位元(ion bit)单元可使用小的有效宽度。在一些实施例中,特殊的位元单元或具有强离子的选择闸sg(例如开关ss、sb)可使用非分割wl(例如结构810i)。

[0242]

图8j至图8k为展示根据一实施例的记忆体阵列的例示性实施的图,此记忆体阵列具有gsl/gbl连接及合并选择闸。记忆体阵列800j包括为记忆体阵列800j的底侧上的合并选择闸(例如开关ss、sb)而实施的结构806j。记忆体阵列800k包括为记忆体阵列800k的顶侧上的合并选择闸(例如开关ss、sb)而实施的结构806k。对于强离子单元可配置合并选择sg以执行位元单元选择。

[0243]

图8l为从四个不同的视角展示根据一实施例的记忆体阵列的例示性实施的图。如图8l所示,记忆体阵列800l包括为全域位元线gbl连接而实施的结构802l(例如s/bl连接)。记忆体阵列800l亦可包括为开关(ss、sb)而实施的结构806l(例如sl/bl),例如晶体管通道。记忆体阵列800l亦可包括为位元单元而实施的结构810l(例如wl),例如晶体管。记忆体

阵列800l亦可包括为通道而实施的结构824l。记忆体阵列800l亦可包括为通孔(有时称为“梯状通孔”)而实施的结构830l。

[0244]

记忆体阵列800l可包括两侧字线wl(例如结构810l)触点以松弛(例如放松)路由节距。记忆体阵列800l可包括第一类型的一或多个结构及/或层,其中包括多晶硅、tin、w、cu或任何导电材料。在一实例中,记忆体阵列800l可包括第二类型的一或多个结构及/或层,其中包括多晶硅、ltps、a-si tft、igzo或任何半导体特性材料。在一实例中,记忆体阵列800l可包括第三类型的一或多个结构及/或层,其中包括钙钛矿、sbt、pzt、hfzro、hfo或任何铁电特性材料。在结构及/或层之间,记忆体阵列800l可包括用于隔离的结构。举例而言,一结构可与其他结构电性隔离或耦接。

[0245]

3.3.实施说明性实施例的方法

[0246]

图9为展示根据一些实施例的存取及/或操作记忆体单元(例如记忆体单元125)及/或记忆体阵列(例如记忆体阵列210)的方法900的流程图。可通过图1中的记忆体控制器105执行方法900。在一些实施例中,通过其他实体执行方法900。在一些实施例中,相比于图9中所示的操作,方法900包括更多或更少或不同的操作。

[0247]

在操作902中,记忆体控制器105在第一时间周期内启用(例如选择)连接至一组(例如3100.…

310[03])记忆体单元的第一子集(例如310[00])的第一开关(例如sb、ss),其中第一子集包括第一串记忆体单元及第二串记忆体单元。通过启用第一开关,记忆体单元(包括其各别的第一串及第二串记忆体单元)的第一子集可电耦接至一或多个全域线。举例而言,可启用连接至记忆体单元的子集310[00]的开关sb、ss,使得在第一时间周期内,记忆体单元的子集310[00]可电耦接至全域位元线gbl[0]及全域选择线gsl[0]。

[0248]

在操作904中,记忆体控制器105在第一时间周期内禁用(例如取消选择)连接至一组(例如3100.…

310[03])记忆体单元的第二子集(例如310[01])的第二开关(例如sb、ss),其中第二子集包括第三串记忆体单元及第四串记忆体单元。通过禁用第二开关,记忆体单元(包括其各别的第三串及第四串记忆体单元)的第二子集可与一或多个全域线电去耦。举例而言,可禁用连接至记忆体单元的子集310[01]的开关sb、ss,使得在第一时间周期内,记忆体单元的子集310[01]可与全域位元线gbl[0]及全域选择线gsl[0]电去耦。在一方法中,记忆体控制器105可禁用连接至此组(例如3100.…

310[03])记忆体单元的其他子集(例如310[02]、310[03])的开关(例如sb、ss),使得全域线(例如gbl[0]、gsl[0])具有电容负载,此电容负载对应于记忆体单元的第一子集(例如310[00])而非整组记忆体单元(例如3100.…

310[03])。

[0249]

在操作906中,记忆体控制器105在第一时间周期内存取(例如配置、程序化、读取、写入)记忆体单元的第一子集(例如310[00])的一或多个记忆体单元。举例而言,记忆体控制器105可经由其各别的分割字线(例如wl[x][y]_l或wl[x][y]_r)对一串记忆体单元施加电压、电流或脉冲,程序化此串记忆体单元,或使此串记忆体单元根据程序化数据传导电流。举例而言,位于所选择子集310[00]左侧上的第一串记忆体单元可耦接至wl[0][0]_l,位于所选择子集310[00]右侧上的第二串记忆体单元可耦接至wl[0][0]_r。记忆体控制器可通过对wl[0][0]_l施加电压、电流或脉冲来存取第一串记忆体单元。由于第二串记忆体单元不耦接至wl[0][0]_l而耦接至wl[0][0]_r,因此记忆体控制器105可在不由第二串记忆体单元产生电容负载的情况下存取第一串记忆体单元。

[0250]

在一方法中,记忆体控制器105可对记忆体单元的未选择子集(例如310[01]

…

310[03])的其他串记忆体单元施加电压、电流或脉冲。然而,由于连接至记忆体单元的未选择子集的开关sb、ss与全域线gbl、gsl电去耦,故虽然施加了电压、电流或脉冲,但未选择子集中的记忆体单元可不经格式化或不传导电流。因此,记忆体控制器105可在不由未选择子集中的其他串记忆体单元产生电容负载的情况下存取记忆体单元的所选择子集(例如310[00]))中的一串记忆体单元。

[0251]

在一方法中,记忆体控制器105可在第一时间周期内启用连接至一组(例如310[10]

…

310[13])记忆体单元的第三子集(例如310[10])的第三开关(例如sb、ss),其中第三子集包括第五串记忆体单元及第六串记忆体单元。记忆体控制器105可在第一时间周期内禁用连接至此组(例如310[10]

…

[13])记忆体单元的第四子集(例如310[11])的第四开关(例如sb、ss),其中第四子集包括第七串记忆体单元及第八串记忆体单元。在第一时间周期内,记忆体控制器105可禁用连接至此组记忆体单元的其他子集(例如310[12]、310[13])的其他开关(例如sb、ss)。通过启用连接至记忆体单元(包括其各别的第五串及第六串记忆体单元)的第三子集(例如310[10])的第三开关及禁用连接至一组记忆体单元(例如310[10]

…

310[13])的其他子集(例如310[11]

…

310[13])的其他开关,全域线(例如gbl[1]、gsl[1])可具有电容负载,此电容负载对应于记忆体单元的第三子集(例如310[10])而非整组(例如310[10]

…

310[13])记忆体单元。此外,可经由各别的分割字线(例如wl[x][y]_l)存取记忆体单元的第三子集(例如310[10])的一串记忆体单元,而在第一时间周期内可经由同一(共享的)字线存取记忆体单元的第一子集(例如310[00])的一串记忆体单元。举例而言,可经由wl[0][0]_l存取位于子集310[10]左侧上的第五串记忆体单元及位于子集310[00]左侧上的第一串记忆体单元。作为另一实例,可经由wl[0][0]_r存取位于子集310[10]右侧上的第六串记忆体单元及位于子集310[00]右侧上的第二串记忆体单元。

[0252]

在操作908中,记忆体控制器105可在第二时间周期内启用连接至一组(例如3100.…

310[03])记忆体单元的第二子集(例如310[01])的第二开关(例如sb、ss)。通过启用第二开关,记忆体单元(包括其各别的第三串及第四串记忆体单元)的第二子集(例如310[01])可电耦接至全域线。举例而言,可启用连接至记忆体单元的子集310[01]的开关sb、ss,使得在第二时间周期内,记忆体单元的子集310[01]可电耦接至全域位元线gbl[0]及全域选择线gsl[0]。

[0253]

在操作910中,记忆体控制器105可在第二时间周期内禁用连接至一组(例如3100.…

310[03])记忆体单元的第一子集(例如310[00])的第一开关(例如sb、ss)。通过禁用第一开关,记忆体单元的第一子集(例如310[00])可与全域线电去耦。举例而言,可禁用连接至记忆体单元的子集310[00]的开关sb、ss,使得记忆体单元(包括其各别的第一串及第二串记忆体单元)的子集310[00]可与全域位元线gbl[0]及全域选择线gsl[0]电去耦。在一方法中,记忆体控制器105可禁用连接至此组(例如3100.…

310[03])记忆体单元的其他子集(例如310[02]、310[03])的开关(例如sb、ss),使得全域线(例如gbl[0]、gsl[0])具有电容负载,此电容负载对应于记忆体单元的第二子集(例如310[01])而非整组记忆体单元(例如3100.…

310[03])。

[0254]

在操作912中,记忆体控制器105在第二时间周期内存取(例如配置、程序化、读取、写入)记忆体单元的第二子集(例如310[01])的一或多个记忆体单元。举例而言,记忆体控

制器105可经由其各别的分割字线(例如wl[x][y]_l或wl[x][y]_r)对一串记忆体单元施加电压、电流或脉冲,程序化此串记忆体单元,或使此串记忆体单元根据程序化数据传导电流。

[0255]

在一方法中,记忆体控制器105可对记忆体单元的未选择子集(例如310[00]、310[02]

…

310[03])的其他串记忆体单元施加电压、电流或脉冲。然而,由于连接至记忆体单元的未选择子集的开关sb、ss与全域线gbl、gsl电去耦,故虽然经由字线施加了电压、电流或脉冲,但未选择子集中的记忆体单元可不经格式化或不传导电流。因此,记忆体控制器105可在不由未选择子集中的其他串记忆体单元产生电容负载的情况下存取记忆体单元的所选择子集(例如310[01]))中的一串记忆体单元。

[0256]

在一方法中,记忆体控制器105可在第二时间周期内启用连接至一组(例如310[10]

…

310[13])记忆体单元的第四子集(例如310[11])的第四开关(例如sb、ss),其中第三子集包括第五串记忆体单元及第六串记忆体单元。记忆体控制器105可在第二时间周期内禁用连接至一组(例如310[10]

…

[13])记忆体单元的第三子集(例如310[10])的第三开关(例如sb、ss),其中第三子集包括第三串记忆体单元及第四串记忆体单元。在第二时间周期内,记忆体控制器105可禁用连接至此组记忆体单元的其他子集(例如310[12]、310[13])的其他开关(例如sb、ss)。通过启用连接至记忆体单元(包括其各别的第七串及第八串记忆体单元)的第四子集(例如310[11])的第四开关及禁用连接至一组记忆体单元(例如310[10]

…

310[13])的其他子集(例如310[10]、310[12]

…

310[13])的其他开关,全域线(例如gbl[1]、gsl[1])可具有电容负载,此电容负载对应于记忆体单元的第四子集(例如310[11])而非整组(例如310[10]

…

310[13])记忆体单元。此外,可存取记忆体单元的第四子集(例如310[11])的一串记忆体单元,而在第二时间周期内经由同一(例如共享的、共用的、耦接的)字线存取记忆体单元的第二子集(例如310[01])的一串记忆体单元。

[0257]

4.4.实施说明性实施例的计算系统

[0258]

图10为根据本揭露的一些实施例的计算系统1000的例示性方块图。电路或布局设计师可在集成电路设计中使用计算系统1000。本文使用的“电路”为用以实施所要功能的诸如电阻器、晶体管、开关、电池、电感器或其他类型半导体元件的电子元件互连。计算系统1000包括与记忆体元件1010关联的主装置1005。主装置1005可用以自一或多个输入装置1015接收输入,且向一或多个输出装置1020提供输出。主装置1005可用以经由适当的接口1025a、1025b及1025c各别地与记忆体元件1010、输入装置1015及输出装置1020通信。可在各种计算装置(诸如计算机(例如桌上型计算机、膝上型计算机、服务器、数据中心等)、平板计算机、个人数字助理、移动装置、其他手持式或可携式装置或适于使用主装置1005进行构想设计及/或布局设计的任何其他计算单元)中实施计算系统1000。

[0259]

输入装置1015可包括诸如键盘、电笔、触控屏幕、鼠标、轨球、小键盘、麦克风、语音辨识、动作辨识、遥控器、输入端口、一或多个按钮、拨盘、摇杆及与主装置1105关联的任何其他输入周边装置,且允许诸如使用者(例如电路或布局设计师)的外源将信息(例如数据)键入至主装置且向主装置发送指令的各种输入技术的任一者。类似地,输出装置1020可包括各种输出技术,诸如外部记忆体、印表机、扬声器、显示器、麦克风、发光二极管、耳机、视频装置及用以从主装置1005接收信息(例如数据)的任何其他输出周边装置。输入至主装置1005及/或自主装置输出的“数据”可包括适于使用计算系统1000处理的各种文本数据、电

路数据、信号数据、半导体元件数据、图形数据、其组合或其他类型的模拟及/或数字数据中的任一者。

[0260]

主装置1005包括诸如中央处理单元(“central processing unit,cpu”)核心1030a-1030n的一或多个处理单元/处理器,或与其关联。cpu核心1030a-1030n可实施为特殊应用集成电路(“application specific integrated circuit,asic”)、现场可程序化门阵列(“field programmable gate array,fpga”)或其他类型的处理单元。cpu核心1030a-1030n中的任一者可用以执行用于运行主装置1005的一或多个应用的指令。在一些实施例中,运行一或多个应用的指令及数据可储存于记忆体元件1010内。主装置1005亦可用以储存运行记忆体元件1010内一或多个应用的结果。由此,主装置1005可用以要求记忆体元件1010执行各个操作。举例而言,主装置1005可要求记忆体元件1010读取数据、写入数据、更新或删除数据及/或执行管理或其他操作。主装置1005可用以运行的一个此类应用可为标准单元应用1035。标准单元应用1035可为计算机辅助设计或电子设计自动化软件套件的一部分,其可由主装置1005的使用者使用以建立或修改电路的标准单元。在一些实施例中,执行或运行标准单元应用1035的指令可储存于记忆体元件1010内。cpu核心1030a-1030n中的一或多者可使用与记忆体元件1010的标准单元应用关联的指令来执行标准单元应用1035。在一实例中,标准单元应用1035允许使用者使用记忆体系统100或记忆体系统100的一部分的预生成的示意性及/或布局设计来辅助集成电路设计。在完成集成电路的布局设计之后,可通过制造设施根据布局设计制造(例如)包括记忆体系统100或记忆体系统100的一部分的多个集成电路。

[0261]

仍参考图10,记忆体元件1010包括记忆体控制器1040,记忆体控制器1040用以自记忆体阵列1045读取数据或将数据写入至记忆体阵列1045。记忆体阵列1045可包括各种挥发性及/或非挥发性记忆体。举例而言,在一些实施例中,记忆体阵列1045可包括nand快闪记忆体核心。在其他实施例中,记忆体阵列1045可包括nor快闪记忆体核心、静态随机存取记忆体(sram)核心、动态随机存取记忆体(dram)核心、磁阻性随机存取记忆体(mram)核心、相变化记忆体(pcm)核心、电阻式随机存取记忆体(reram)核心、3d xpoint记忆体核心、铁电式随机存取记忆体(feram)核心及适合在记忆体阵列中使用的其他类型的记忆体核心。记忆体阵列1045内的记忆体可由记忆体控制器1040单独且独立地控制。换言之,记忆体控制器1040可用以与记忆体阵列1045内的每一记忆体单独且独立地通信。通过与记忆体阵列1045通信,记忆体控制器1040可用以回应于自主装置1005接收的指令自记忆体阵列读取数据或将数据写入至记忆体阵列。虽然展示为记忆体元件1010的一部分,但在一些实施例中,记忆体控制器1040可为主装置1005的一部分或计算系统1000中与记忆体元件关联的另一组件的一部分。记忆体控制器1040可实现为软件、硬件、固件或其组合中的逻辑电路以执行本文描述的功能。举例而言,在一些实施例中,记忆体控制器1040可用以在一从主装置1005接收到要求时即撷取与储存于记忆体元件1010的记忆体阵列1045中的标准单元应用1035关联的指令。

[0262]

应理解图10仅展示并描述计算系统1000的一些组件。然而,计算系统1000可包括诸如各种电池及电源、网络接口、路由器、开关、外部记忆体系统、控制器等的其他组件。总体而言,计算系统1000可包括执行本文描述的功能时所需要或理想的各种硬件、软件及/或固件组件中的任一者。类似地,主装置1005、输入装置1015、输出装置1020及包括记忆体控

制器1040及记忆体阵列1045的记忆体元件1010可包括执行本文描述的功能时所需要或理想的其他硬件、软件及/或固件组件。

[0263]

本说明的一态样是关于记忆体阵列。在一些实施例中,记忆体阵列包括第一组记忆体单元,其包括记忆体单元的第一子集及记忆体单元的第二子集。在一些实施例中,记忆体阵列包括第一开关,每一开关包括:连接至记忆体单元的第一子集的第一电极的第一电极;及连接至第一全域线的第二电极。在一些实施例中,记忆体阵列包括第二开关,每一开关包括:连接至记忆体单元的第二子集的第一电极的多个第一电极;及连接至第一全域线的第二电极。

[0264]

本说明的一态样是关于记忆体系统。在一些实施例中,记忆体系统包括记忆体阵列及控制器。在一些实施例中,记忆体阵列包括第一组记忆体单元、第二组记忆体单元、连接至第一组记忆体单元的第一开关及连接至第二组记忆体单元的第二开关。在一些实施例中,控制器连接至记忆体单元。在一些实施例中,控制器在第一时间周期内启用第一开关,同时禁用第二开关,以将第一组记忆体单元电耦接至第一全域选择线,将第二组记忆体单元与第一全域选择线电去耦。在一些实施例中,控制器在第二时间周期内启用第二开关,同时禁用第一开关,以将第二组记忆体单元电耦接至第一全域选择线,将第一组记忆体单元与第一全域选择线电去耦。

[0265]

本说明的一态样是关于操作记忆体系统的方法。在一些实施例中,方法包括在第一时间周期内启用连接至第一组记忆体单元的第一电极的第一开关,将第一组记忆体单元的第一电极电耦接至第一全域选择线。在一些实施例中,方法包括在第一时间周期内禁用连接至第二组记忆体单元的第一电极的第二开关,将第二组记忆体单元的第一电极与第一全域选择线电去耦。在一些实施例中,方法包括在第一时间周期内启用连接至第一组记忆体单元的第二电极的第三开关,将第一组记忆体单元的第二电极电耦接至第一全域位元线。在一些实施例中,方法包括在第一时间周期内禁用连接至第二组记忆体单元的第二电极的第四开关,将第二组记忆体单元的第二电极与第一全域位元线电去耦。在一些实施例中,方法包括在第一时间周期内配置第一组记忆体单元的一或多个记忆体单元。

[0266]

本揭露的一些实施方式提供一种记忆体阵列,其包含第一组记忆体单元及第一开关。第一组记忆体单元包括第一串记忆体单元及第二串记忆体单元,其各自在记忆体阵列的多个层上延伸,每一层包括:第一串记忆体单元的记忆体单元,其具有耦接至与层关联的第一字线的栅电极;第二组记忆体单元的记忆体单元,其具有耦接至与层关联的第二字线的栅电极。第一开关包括第一电极连接至第一串记忆体单元的多个第一电极及第二串记忆体单元的多个第一电极,及第二电极连接至第一全域位元线。

[0267]

在一些实施例中,记忆体阵列进一步包含:第二开关包括第一电极及第二电极。第一电极连接至第一串记忆体单元的多个第二电极及第二串记忆体单元的多个第二电极。第二电极连接至第一全域选择线。

[0268]

在一些实施例中,记忆体阵列进一步包含:第二组记忆体单元及第三开关。第二组记忆体单元包括第三串记忆体单元及第四串记忆体单元。第三开关包括第一电极连接至第三串记忆体单元的多个第一电极及第四串记忆体单元的多个第一电极,及第二电极连接至第二全域位元线。其中第三串记忆体单元的栅电极连接至第一字线,第四串记忆体单元的栅电极连接至第二字线。

[0269]

在一些实施例中,记忆体阵列进一步包含:第四开关包括第一电极连接至第三串记忆体单元的多个第二电极及第四串记忆体单元的多个第二电极,及第二电极连接至第二全域选择线。

[0270]

在一些实施例中,第一开关的栅电极及第三开关的栅电极连接至第一开关控制线,且其中第二开关的栅电极及第四开关的栅电极连接至第二开关控制线。

[0271]

在一些实施例中,记忆体阵列进一步包含:第二组记忆体单元,其包括第三串记忆体单元及第四串记忆体单元;及第三开关包括第一电极连接至第三串记忆体单元的多个第一电极及第四串记忆体单元的多个第一电极,及第二电极连接至第一全域位元线。其中第三串记忆体单元的多个栅电极连接至第三字线,第四串记忆体单元的多个栅电极连接至第四字线。

[0272]

在一些实施例中,记忆体阵列进一步包含:第四开关包括第一电极连接至第三串记忆体单元的多个第二电极及第四串记忆体单元的多个第二电极,及第二电极连接至第二全域选择线。

[0273]

在一些实施例中,第一开关、第二开关、第三开关及第四开关的栅电极连接至不同的开关控制线。

[0274]

在一些实施例中,第一开关的栅电极及第二开关的栅电极连接至相同的开关控制线。

[0275]

在一些实施例中,第一组记忆体单元及第一开关对应于匹配类型的晶体管,其中该些类型的晶体管包括n型金属氧化物半导体场效晶体管(nmos)或p型金属氧化物半导体场效晶体管(pmos)。

[0276]

本揭露的一些实施方式提供一种记忆体系统,其包含记忆体阵列以及控制器连接至记忆体阵列。记忆体阵列包括第一组记忆体单元以及第一开关,第一组记忆体单元包括:第一串记忆体单元,具有耦接至第一字线的多个栅电极;及第二串记忆体单元,具有耦接至第二字线的多个栅电极。控制器将切换第一开关,将第一全域位元线电耦接至第一串记忆体单元的多个第一电极及第二串记忆体单元的多个第一电极。控制器将回应于切换第一开关而使用第一字线配置第一串记忆体单元。

[0277]

在一些实施例中,记忆体阵列进一步包含第二开关。其中控制器将进一步:切换第二开关,将第一全域选择线电耦接至第一串记忆体单元的多个第二电极及第二串记忆体单元的多个第二电极,及回应于切换第一开关及第二开关而使用第一字线配置第一串记忆体单元。

[0278]

在一些实施例中,记忆体阵列进一步包含第二组记忆体单元、第三开关、及第四开关。第二组记忆体单元包括:第三串记忆体单元,具有耦接至第一字线的多个栅电极;及第四串记忆体单元,具有耦接至第二字线的多个栅电极。第三开关,其中控制器将进一步回应于切换第一开关及第二开关,切换第三开关,将第二全域位元线耦接至第三串记忆体单元的多个第一电极及第四串记忆体单元的多个第一电极。第四开关,其中控制器将进一步回应于切换第一及第二开关,切换第四开关,将第二全域选择线耦接至第三串记忆体单元的多个第二电极及第四串记忆体单元的多个第二电极。

[0279]

在一些实施例中,控制器将进一步回应于切换第一开关及第二开关而使用第二字线配置第二串记忆体单元。

[0280]

在一些实施例中,记忆体阵列进一步包含:第二组记忆体单元及第三开关。第二组记忆体单元包括第三串记忆体单元,具有耦接至第三字线的多个栅电极;及第四串记忆体单元,具有耦接至第四字线的多个栅电极。第三开关,其中控制器将进一步:在切换第一开关及第二开关之前,切换第三开关,将第一全域位元线与第三串记忆体单元的多个第一电极及第四串记忆体单元的多个第一电极去耦。

[0281]

在一些实施例中,记忆体阵列进一步包含第四开关,其中控制器将进一步:在切换第一开关及第二开关之前,切换第三开关,将第一全域选择线与第三串记忆体单元的多个第二电极及第四串记忆体单元的多个第二电极去耦。

[0282]

在一些实施例中,第一开关的栅电极及第二开关的栅电极连接至相同的开关控制线。

[0283]

在一些实施例中,第一组记忆体单元及第一开关对应于匹配类型的晶体管,其中该些类型的晶体管包括n型金属氧化物半导体场效晶体管(nmos)或p型金属氧化物半导体场效晶体管(pmos)。

[0284]

本揭露的一些实施方式提供操作记忆体阵列的方法,其包含:在第一时间周期内将第一组记忆体单元的多个第一电极耦接至第一全域位元线;在第一时间周期内将第一组记忆体单元的多个第二电极耦接至第一全域选择线,其中第一组记忆体单元包括第一串记忆体单元及第二串记忆体单元;在第一时间周期内将第二组记忆体单元的多个第一电极与第一全域选择线去耦;在第一时间周期内将第二组记忆体单元的多个第二电极与第一全域位元线去耦;及在第一时间周期内,在不存取记忆体单元的第一子集的第二串记忆体单元的栅电极的情况下,存取记忆体单元的第一子集的第一串记忆体单元的栅电极。

[0285]

在一些实施例中,方法进一步包含:在第二时间周期内,在不存取记忆体单元的第一组记忆体单元的第一串记忆体单元的栅电极的情况下,存取记忆体单元的第一组记忆体单元的第二串记忆体单元的栅电极。

[0286]

上文概述若干实施例的特征,使得熟悉此项技术者可较佳地理解本揭露的态样。熟悉此项技术者应理解他们可容易地以本揭露为基础来设计或修改其他制程或结构,以达到相同的目的及/或获得本文所介绍的实施例的相同优点。熟悉此项技术者亦应认识到这些等效构造不脱离本揭露的精神及范畴,并且他们可在不脱离本揭露的精神及范畴的情况下作出各种改变、替换及更改。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1