半导体装置及连续读出方法与流程

1.本发明涉及一种半导体装置,尤其涉及半导体装置及与非(nand)型闪速存储器的连续读出方法。

背景技术:

2.在nand型闪速存储器中,有时搭载响应来自外部命令而连续地读出多个页的连续读出功能(突发读出功能(burst read function))。页缓冲器(page buffer)/读出电路例如包括两个锁存器,在进行连续读出动作时,其中一个锁存器保持自阵列读出数据的期间,能够输出另一个锁存器所保持的数据(如专利文献1、专利文献2、专利文献3等)。专利文献4公开了一种实现连续读出的进一步高速化的读出方法。

3.[现有技术文献]

[0004]

[专利文献]

[0005]

[专利文献1]日本专利5323170号公报

[0006]

[专利文献2]日本专利5667143号公报

[0007]

[专利文献3]美国专利申请us2014/0104947a1

[0008]

[专利文献4]日本专利6744950号公报

技术实现要素:

[0009]

图1示出搭载在芯片上(on chip)错误检测校正(error checking and correction,ecc)功能的nand型闪速存储器概略结构。闪速存储器包括:包含nand串(string)的存储单元阵列(memory cell array)10、页缓冲器/读出电路20、数据传送电路30、数据传送电路32、错误检测校正电路(以下称为ecc电路)40、以及输入输出电路50。页缓冲器/读出电路20包括保持读出数据或应编程的输入数据的两个锁存器(latch)l1、l2(一个锁存器例如4kb),锁存器l1、锁存器l2分别包括第一高速缓存(cache)c0以及第二高速缓存c1(一个高速缓存例如2kb)。

[0010]

图2示出专利文献4公开的进行多个页的连续读出时的时序图。首先,进行页p0的阵列读出,将页p0的数据保持于锁存器l1的第一高速缓存c0及第二高速缓存c1(p0c0,p0c1)。接着,锁存器l1的第一高速缓存c0及第二高速缓存c1的数据被传送至锁存器l2的第一高速缓存c0及第二高速缓存c1,第一高速缓存c0及第二高速缓存c1的数据在ecc电路40中进行ecc解码的运算,在检测出错误的情况下,校正锁存器l2的第一高速缓存c0、第二高速缓存c1的数据。

[0011]

在连续读出中,行地址计数器自动递增,并进行下一页p1的读出,所读出的数据被传送至锁存器l1的第一高速缓存c0及第二高速缓存c1。在此期间,锁存器l2的第一高速缓存c0的数据被传送至输入输出电路50,输入输出电路50所保持的数据与自外部供给的外部时钟信号exclk同步地输出。接着,与外部时钟信号exclk同步地自输入输出电路50输出锁存器l2的第二高速缓存c1的数据,在此期间,锁存器l1的第一高速缓存c0的数据被传送至

锁存器l2,且由ecc电路40进行ecc处理。

[0012]

在锁存器l1的第二高速缓存c1的数据被传送至锁存器l2,锁存器l2的第一高速缓存c0的数据自输入输出电路50输出的期间,锁存器l2的第二高速缓存c1的数据经ecc处理,继而,在锁存器l2的第二高速缓存c1的数据自输入输出电路50输出的期间,下一页p2自阵列读出,并被传送至锁存器l1的第一高速缓存c0及第二高速缓存c1,且第一高速缓存c0的数据被传送至锁存器l2,进行ecc处理。

[0013]

利用锁存器l1、锁存器l2的连续读出实质上从页p2的阵列读出开始。页p2的阵列读出开始时机并非页p1的数据从锁存器l1向锁存器l2传送结束的时间点,而是比此早的将锁存器l1的第一高速缓存c0的页p1的数据传送至锁存器l2的时间点。即便提前了页p2的阵列读出的时机,实际上阵列读出也花费一定的时间,因此在将从阵列读出的页p2的数据传送至锁存器l1的时间点,若为了连续读出的高速化而使用高速频率的外部时钟信号exclk,则页p1的数据从锁存器l1向锁存器l2的传送已经完成。

[0014]

阵列读出时间tarray由阵列读出的开始时机与阵列读出的结束时机规定。页p2阵列读出的结束时机是下一页p3阵列读出的开始时机,在连续地读出页p2、页p3、页p4

…

的页时,阵列读出时间tarray也同样地连续。

[0015]

此处,阵列读出根据所确定的时机使用内部时钟信号运行,另一方面,数据输出根据与内部时钟信号非同步的外部时钟信号exclk运行。图2所示的连续读出的制约由式(1)表示。tarray及tecc为一定的时间,tdout由外部时钟信号exclk的频率规定。

[0016]

tarray<tdout(1页)

[0017]

tecc<tdout(1/2页)

…

(1)

[0018]

只要满足如下制约,即输出一页的数据的时间tdout比阵列读出时间tarray大、输出1/2页数据的时间tdout比ecc处理的时间tecc大,则可实现图2所示连续读出的高速化。在图2中例示了以下情况:与页p2阵列读出时间tarray相比,作为输出页p0的第二高速缓存数据的时间和输出页p1的第一高速缓存数据时间的合计输出时间tdout大,页p2阵列读出时间tarray从开始将页p1的第一高速缓存c0数据自锁存器l1向锁存器l2传送的时间点到开始将下一页p2的第一高速缓存c0数据自锁存器l1向锁存器l2传送的时间点为止;与对锁存器l2的第一高速缓存c0数据进行ecc处理的时间tecc相比,输出锁存器l2的第二高速缓存c1的数据的时间tdout大。

[0019]

但是,通过变更阵列读出的开始时机而产生另外的时机制约。假设用户使用了频率慢的外部时钟信号exclk的情况下,将从阵列读出的数据传送至锁存器l1的时间点,锁存器l1由于外部时钟信号exclk的慢频率而保持前一页的数据,则锁存器l1前一页的数据被阵列读出的下一页数据破坏。

[0020]

式(2)表示用于不产生此种数据破坏的制约。

[0021]

tdout(1/2页)<tarray

…

(2)、

[0022]

从式(1)、式(2)导出式(3)。

[0023]

tarray<tdout<tarray

×2…

(3)

[0024]

为了能够使用频率比式(3)规定的最小频率低的外部时钟信号exclk,现有的闪速存储器准备状态寄存器,并根据设定于状态寄存器的值,对如图2所示那样的高速连续读出,或者在保持于锁存器l1的数据被传送至锁存器l2之后进行阵列读出的连续读出进行切

换。图3示出状态寄存器的一例。设定值“1”对应于高速频率的外部时钟信号exclk的使用,并在连续读出中在图2所示的时机开始阵列读出,设定值“0”对应于低速频率的外部时钟信号exclk的使用,并在连续读出时机开始阵列读出。状态寄存器的设定值能够从外部改写,用户可输入来自外部的改写命令及状态寄存器的地址“xxh”,变更状态寄存器的设定值。

[0025]

此种现有的闪速存储器通过使外部时钟信号exclk的频率最大化而可实现连续读出的高速化,另一方面,外部时钟信号exclk的频率的最小值存在制约,为了能够使用此种低速频率,需要用于切换状态寄存器或阵列读出的开始时机的电路。进而,用户必须对状态寄存器进行动作的设定而复杂。

[0026]

另外,在连续读出时,在数据输出中进行阵列读出,当在某动作的时机输入输出(input/output,io)噪声与阵列读出的电流重叠时,会产生大的峰值电流icc。输入输出电路50例如包括连接有m个触发器的并行/串行转换电路,且与外部时钟信号exclk同步地将m位的并行数据转换为串行数据,并将其从外部端子输出。另一方面,在连续读出中,为了对位线进行预充电,流通大的电流,若一页的尺寸变大,则消耗相应大的电流。

[0027]

阵列读出是与由内部时钟发生器生成的内部时钟信号inclk同步地进行,但内部时钟信号inclk与外部时钟信号exclk非同步。两时钟信号的边缘在时间上重叠或接近时,由于与时钟信号同步的动作而产生大的峰值电流icc。大的峰值电流icc使内部的供给电压暂时下降,或者产生噪声,由此电路的动作延迟,或者动作变得不稳定。因此,尽可能减少峰值电流icc。

[0028]

本发明的nand型闪速存储器的页的连续读出方法包括:第一读出步骤,从第一存储单元阵列读出1/2页的第一数据,并将所读出的第一数据保持于第一保持电路;第二读出步骤,以与第一存储单元阵列不同的时机,从第二存储单元阵列读出1/2页的第二数据,并将所读出的第二数据保持于第二保持电路;第一输出步骤,与时钟信号同步地输出第一数据;以及第二输出步骤,在与时钟信号同步地输出第一数据后连续地输出第二数据。

[0029]

连续读出方法还包括:第一传送步骤,将保持于第一保持电路的第一数据传送至第三保持电路;以及第二传送步骤,将保持于第二保持电路的第二数据传送至第四保持电路,在第一传送步骤后,通过第一读出步骤读出的下一页的1/2页的第一数据保持于第一保持电路,在第二传送步骤后,通过第二读出步骤读出的下一页的1/2页的第二数据保持于第二保持电路。连续读出方法还包括:第一ecc步骤,对保持于第三保持电路的第一数据进行错误检测和校正;以及第二ecc步骤,对保持于第四保持电路的第二数据进行错误检测和校正。在通过第一输出步骤输出保持于第三保持电路的第一数据的期间,第二ecc步骤对保持于第四保持电路的下一页的第二数据进行错误检测和校正,在通过第二输出步骤输出保持于第四保持电路的第二数据的期间,第一ecc步骤对保持于第三保持电路的下一页的第一数据进行错误检测和校正。第一读出步骤响应通过第一输出步骤输出了保持于第三保持电路的第一数据而进行前两页的1/2页的第一数据的读出,第二读出步骤响应通过第二输出步骤输出了保持于第四保持电路的第二数据而进行前两页的1/2页的第二数据的读出。第一输出步骤及第二输出步骤从多个外部端子的各者交替地连续输出第一数据与第二数据。

[0030]

本发明的nand型闪速存储器的页的连续读出方法还包括:读出步骤,从存储单元阵列分别独立地进行前1/2页的阵列读出与后1/2页的阵列读出;保持步骤,将第一阵列读出1/2页的第一数据保持于第一保持电路,将第二阵列读出1/2页的第二数据保持于第二保

持电路;以及输出步骤,通过多个页读出来执行读出步骤及保持步骤,并与时钟信号同步地交替输出第一数据与第二数据。

[0031]

本发明的半导体装置包括:第一阵列读出部件,从nand型第一存储单元阵列读出数据;第二阵列读出部件,从nand型第二存储单元阵列读出数据;第一保持部件,保持第一读出部件读出的数据;第二保持部件,保持第二读出部件读出的数据;输出部件,能够与时钟信号同步地输出由第一保持部件及第二保持部件保持的数据;以及控制部件,对读出动作进行控制,在控制部件对页的连续读出进行控制的情况下,第一阵列读出部件读出1/2页的第一数据,第二阵列读出部件读出1/2页的第二数据,输出部件交替地连续输出第一数据与第二数据。

[0032]

在本发明的一实施方式中,第一保持部件包括:第一锁存器,保持由第一阵列读出部件读出的第一数据;以及第二锁存器,保持从第一锁存器传送的第一数据,在第一数据从第一锁存器向第二锁存器的传送后,由第一阵列读出部件读出的下一页的1/2页的第一数据保持于第一锁存器,第二保持部件包括:第一锁存器,保持由第二阵列读出部件读出的第二数据;以及第二锁存器,保持从第一锁存器传送的第二数据,在第二数据从第一锁存器向第二锁存器的传送后,由第二阵列读出部件读出的下一页的1/2页的第二数据保持于第一锁存器。

[0033]

半导体装置还包括进行数据的错误检测,校正错误检测和校正部件,错误检测和校正部件对第一保持部件及第二保持部件的第二锁存器中所保持的第一数据或第二数据进行错误检测和校正。由输出部件输出第一保持部件的第二锁存器中所保持的第一数据的期间,错误检测和校正部件对第二保持部件的第二锁存器中所保持的下一页的第二数据进行错误检测和校正,在输出部件输出第二保持部件的第二锁存器中所保持的第二数据的期间,错误检测和校正部件对第一保持部件的第二锁存器中所保持的下一页的第一数据进行错误检测和校正。第一阵列读出部件响应由输出部件输出第一保持部件的第二锁存器中所保持的第一数据而进行前两页的1/2页的第一数据的读出,第二阵列读出部件响应输出部件输出第二保持部件的第二锁存器中所保持的第二数据而进行前两页的1/2页的第二数据的读出。第一存储单元阵列与第二存储单元阵列可形成于同一芯片上。或者第一存储单元阵列与所述第二存储单元阵列分别形成于不同的芯片上。输出部件从多个外部端子的各者交替地连续输出第一数据与第二数据。

[0034]

本发明的nand型闪速存储器的读出方法包括以下步骤:接收命令;基于命令判别是通常的页读出还是多个页的连续读出;在判别为通常的页读出的情况下,同时访问第一存储单元阵列与第二存储单元阵列,从第一存储单元阵列及第二存储单元阵列读出一页的数据,并将所读出的数据保持于第一保持电路及第二保持电路;以及在判别为多个页的连续读出的情况下,各别地访问第一存储单元阵列及第二存储单元阵列,从第一存储单元阵列读出1/2页的第一数据,并将所读出的第一数据保持于第一保持电路,从第二存储单元阵列读出剩余的1/2页的第二数据,并将所读出的第二数据保持于第二保持电路。

[0035]

本发明的半导体装置还包括:控制部件基于所接收到的命令判别是通常的页读出还是多个页的连续读出,在判别为通常的页读出的情况下,从第一存储单元阵列及第二存储单元阵列同时读出一页的数据,并使第一保持部件及第二保持部件保持所读出的数据,在判别为多个页的连续读出的情况下,从第一存储单元阵列读出1/2页的第一数据,并使第

一保持部件保持所读出的第一数据,然后,从第二存储单元阵列读出剩余的1/2页的第二数据,并使第二保持部件保持所读出的第二数据。

[0036]

根据本发明,由于在进行页的连续读出的情况下,独立地进行从第一存储单元阵列的1/2页的读出与从第二存储单元阵列的1/2页的读出,因此可不受时钟信号的频率的制约地进行页的连续读出。进而通过分成1/2页进行读出,可减少阵列读出时的峰值电流,由此可提高电路动作的可靠性。

附图说明

[0037]

图1是表示现有nand型闪速存储器的概略结构图;

[0038]

图2是现有nand型闪速存储器中进行连续读出时的时序图;

[0039]

图3是表示现有的状态寄存器图;

[0040]

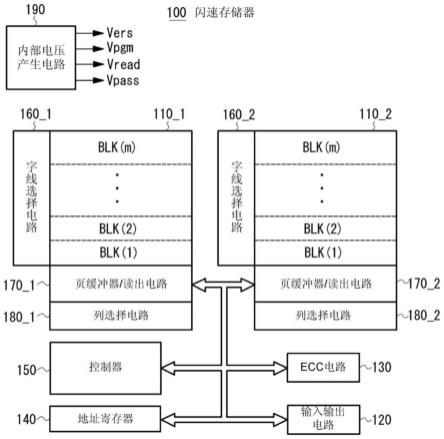

图4是表示本发明实施例的nand型闪速存储器的结构框图;

[0041]

图5是表示本实施例的nand串的电路结构图;

[0042]

图6是表示本实施例的位线选择电路的结构图;

[0043]

图7是表示本实施例的页缓冲器/读出电路的结构图;

[0044]

图8是示意性地说明本实施例的连续读出动作图;

[0045]

图9是在本实施例闪速存储器中进行连续读出动作时的时序图;

[0046]

图10(a)是表示本发明实施例的变形例的闪速存储器的结构图,图10(b)是表示其内部结构的图。

[0047]

[符号的说明]

[0048]

10、110_1、110_2、340_1:存储单元阵列

[0049]

20、170_1、170_2:页缓冲器/读出电路

[0050]

30、32:数据传送电路

[0051]

40、130:ecc电路

[0052]

50、120、370_1、370_2:输入输出电路

[0053]

100、100b:闪速存储器

[0054]

140:地址寄存器

[0055]

150、360_1、360_2:控制器

[0056]

160_1、160_2:字线选择电路

[0057]

180_1、180_2:列选择电路

[0058]

190:内部电压产生电路

[0059]

200_1:位线选择电路

[0060]

210:判定电路

[0061]

220_1、220_2:传送电路

[0062]

300_1、300_2:芯片

[0063]

310_1、320_2:内部焊垫

[0064]

320:内部配线

[0065]

330:外部端子

[0066]

350_1:外围电路

[0067]

380:主计算机

[0068]

blcd1、blcd2、blclamp、blcn、blpre、blse、blso、cache、dtg、eq、reg、reset2、vg:晶体管

[0069]

blk(0)、blk(1)、

…

、blk(m-1):存储块

[0070]

bls、slr1、slr2、sls1、sls2:节点

[0071]

c0:第一高速缓存

[0072]

c1:第二高速缓存

[0073]

exclk:外部时钟信号

[0074]

gble:偶数位线

[0075]

gblo:奇数位线

[0076]

l1、l2:锁存器

[0077]

mc0、mc1、mc2、

…

、mc63:存储单元

[0078]

nu:nand串

[0079]

p0、p1、p2、p3、p4:页

[0080]

sgd、sgs:选择栅极线

[0081]

sl:源极线

[0082]

sns:读出节点

[0083]

tarray:阵列读出时间

[0084]

tdout、tdout:输出时间

[0085]

tecc:进行ecc处理的时间

[0086]

v1、v2:电压供给节点

[0087]

vers:擦除电压

[0088]

virpwr:虚拟电源

[0089]

vpass:通过电压

[0090]

vpgm:写入电压(编程电压)

[0091]

vread:读出通过电压

[0092]

wl0、wl1、wl2、

…

、wl31:字线

具体实施方式

[0093]

图4是表示本发明实施例的nand型闪速存储器的结构图。闪速存储器100包括存储单元阵列110_1、存储单元阵列110_2,呈矩阵状地排列有多个存储单元;输入输出电路120,连接于外部输入输出端子,且响应外部时钟信号exclk,并将读出数据输出至外部,或导入自外部输入的数据;ecc电路130,进行应编程的数据或所读出的数据的错误检测和校正;地址寄存器(address register)140,经由输入输出电路120接收地址数据(address data);控制器(controller)150,基于经由输入输出电路120接收的命令数据或施加至外部端子的控制信号等来对各部进行控制;字线(word line)选择电路160_1、字线选择电路160_2,对来自地址寄存器140的行地址信息ax进行解码(decode),并基于解码结果来进行块的选择或字线的选择等;页缓冲器/读出电路170_1、页缓冲器/读出电路170_2,保持自存储单元阵列110_1、存储单元阵列110_2读出的数据,或者保持要编程至阵列的数据;列选择电路180_

1、列选择电路180_2,对来自地址寄存器140的列地址信息ay进行解码,并基于解码结果来进行页缓冲器/读出电路170_1、页缓冲器/读出电路170_2的位线等的选择;以及内部电压产生电路190,生成数据的读出、编程及擦除等所需的各种电压(写入电压vpgm、通过(pass)电压vpass、读出通过电压vread、擦除电压vers等)。

[0094]

本实施例的闪速存储器100包括能够分别独立地运行的两个存储单元阵列110_1、110_2、两个字线选择电路160_1、160_2、两个页缓冲器/读出电路170_1、170_2、以及两个列选择电路180_1、180_2。控制器150经由字线选择电路160_1、字线选择电路160_2、页缓冲器/读出电路170_1、页缓冲器/读出电路170_2及列选择电路180_1、列选择电路180_2对存储单元阵列110_1、存储单元阵列110_2的读出、编程、擦除等动作各别地进行控制。字线选择电路160_1、字线选择电路160_2、页缓冲器/读出电路170_1、页缓冲器/读出电路170_2及列选择电路180_1、列选择电路180_2。存储单元阵列110_1、存储单元阵列110_2、字线选择电路160_1、字线选择电路160_2、页缓冲器/读出电路170_1、页缓冲器/读出电路170_2及列选择电路180_1、列选择电路180_2的结构为共用,因此在以下的说明中,对其中一者进行说明。

[0095]

存储单元阵列110_1例如具有沿列方向配置的m个存储块blk(0)、blk(1)、

…

、blk(m-1)。在一个存储块形成有多个nand串nu,nand串是将多个存储单元串联连接而成。如图5所示,一个nand串nu包括串联连接的多个存储单元mci(i=0、1、

…

、63)、位线侧选择晶体管、以及源极线侧选择晶体管。位线侧选择晶体管的漏极连接于所对应的一个全局位线gbl,源极线侧选择晶体管的源极连接于共用的源极线sl。存储单元mci的控制栅极连接于字线wli,位线侧选择晶体管及源极线侧选择晶体管的各栅极分别连接于选择栅极线sgd、选择栅极线sgs。字线选择电路160_1基于行地址信息ax经由选择栅极线sgd、选择栅极线sgs驱动位线侧选择晶体管、源极线侧选择晶体管,来选择块或字。

[0096]

nand串nu既可二维地形成于基板表面上,也可三维地形成于基板表面上。另外,nand串nu也可在位线侧选择晶体管与存储单元之间和/或源线侧选择晶体管与存储单元之间包括虚设单元。

[0097]

在图6中示出位线选择电路的结构。图6例示由一个偶数位线gble及一个奇数位线gblo共有的一个页缓冲器/读出电路170_1、以及与其连接的位线选择电路200_1。

[0098]

位线选择电路200_1包括:用于选择偶数位线gble的晶体管blse、用于选择奇数位线gblo的晶体管blso、用于将虚拟电源virpwr连接于偶数位线gble的晶体管yble、用于将虚拟电源virpwr连接于奇数位线gblo的晶体管yblo,在偶数位线gble与源极线sl之间连接有nand串,在奇数位线gblo与源极线sl之间连接有nand串。例如,在读出动作中,进行屏蔽读出,在选择偶数位线gble时,不选择奇数位线gblo,在选择奇数位线gblo时,不选择偶数位线gble。非选择的位线经由虚拟电源virpwr连接于接地(ground,gnd)电平。

[0099]

图7示出图6所示的一个页缓冲器/读出电路170_1的结构。为了方便起见,设为施加至晶体管的栅极的信号表示晶体管。页缓冲器/读出电路170包括两个锁存器l1、l2,在锁存器l1与锁存器l2之间连接有传送栅极(晶体管cache),通过将传送栅极接通而能够进行自锁存器l1向锁存器l2、或者自锁存器l2向锁存器l1的双向的数据传送。

[0100]

锁存器l1包括一对交叉耦合的反相器,锁存器l1的节点slr1连接于晶体管blcd1与晶体管dtg的共用源汲/漏极(s/d),节点sls1连接于判定电路210。判定电路210例如判定

编程验证(program verify)或擦除验证是否合格。当在编程验证中,自电压供给节点v2选择性地将节点slr1充电为vdd,或者将节点slr1选择性地放电至gnd时,晶体管dtg导通。进而,锁存器l1能够通过晶体管eq使节点slr1、节点sls1短路。

[0101]

锁存器l1的节点slr1、节点sls1分别经由晶体管cache连接于锁存器l2的节点sls2、节点slr2。锁存器l2的节点slr2经由晶体管blcd2连接于读出节点sns,节点sls2连接于晶体管reset2。当对锁存器l2进行重置时,晶体管reset2导通。

[0102]

在电压供给节点v2与读出节点sns之间串联连接有晶体管vg及晶体管reg,晶体管vg的栅极连接于晶体管dtg的s/d。电压供给节点v1经由晶体管blpre连接于读出节点sns。在读出节点sns与位线选择电路200的节点bls之间串联连接有晶体管blcn及晶体管blclamp。

[0103]

字线选择电路160_1及列选择电路180_1根据行地址信息ax及列地址信息ay来选择页内的数据的读出开始位置,或者在不使用行地址信息ax及列地址信息ay的情况下自页的开头位置自动地读出数据。进而,字线选择电路160_1及列选择电路180_1可包括响应时钟信号而使行地址信息ax及列地址信息ay递增的行地址计数器及列地址计数器。

[0104]

在输出页缓冲器/读出电路170_1的锁存器l2中所保持的数据时,由列选择电路180_1从保持于锁存器l2的数据中选择n位的数据。所选择的n位的数据作为节点sls2、节点slr2的差动数据输入至n个差动读出放大器,n个差动读出放大器将所读出的n位的数据输出至n位宽度的内部数据总线。

[0105]

从n位宽度的内部数据总线输出的数据经由传送电路被选择性地供给至ecc电路130或输入输出电路120。ecc电路130对经由内部数据总线供给的数据进行错误检测和校正。输入输出电路120例如包括直接连接有多个触发器的并行/串行转换电路,并行/串行转换电路与外部时钟信号exclk同步地将从内部数据总线并行地输入的数据转换为串行,并将经转换的数据供给至外部端子。外部端子例如可为

×

1、

×

2、

×

4、

×

8。

[0106]

在闪速存储器的读出动作中,对位线施加某正电压,对选择字线施加某电压(例如0v),对非选择字线施加通过电压vpass(例如4.5v),对选择栅极线sgd、选择栅极线sgs施加正电压(例如4.5v),使位线侧选择晶体管、源极线侧选择晶体管接通,对共用源极线施加0v。在编程动作中,对选择字线施加高电压的编程电压vpgm(15v~20v),对非选择的字线施加中间电位(例如10v),使位线侧选择晶体管接通,使源极线侧选择晶体管断开,对位线供给与“0”或“1”的数据对应的电位。在擦除动作中,对块内的选择字线施加0v,对p阱施加高电压(例如20v),通过将浮动栅极(floating gate)的电子抽出至基板,以块为单位来擦除数据。

[0107]

在闪速存储器100的通常的读出动作、程序动作及擦除动作中,控制器150以两个存储单元阵列110_1、110_2如同一个存储单元阵列那样控制其动作。当闪速存储器100从主计算机接收通常的页读出命令及地址时,命令由控制器150判别,在控制器150的控制下,字线选择电路160_1、字线选择电路160_1基于行地址信息ax同时选择存储单元阵列110_1、存储单元阵列110_2的同一行的字线。即,存储单元阵列110_1的字线的选择对应于1/2页的数据的读出,存储单元阵列110_2的字线的选择对应于1/2页的数据的读出,结果,利用字线选择电路160_1、字线选择电路160_1进行的字线的选择对应于一页的数据的读出。

[0108]

在进行读出动作时,首先,从页缓冲器/读出电路170_1、页缓冲器/读出电路170_2

的电压供给节点v1经由晶体管blpre对选择位线(例如,偶数位线)进行预充电。接着,选择存储单元阵列110_1、存储单元阵列110_2的字线,根据选择存储单元的存储状态对选择位线的电压进行放电。接着,读出节点sns中产生的电位被传送至锁存器l1,如此,阵列读出结束。

[0109]

接着,对闪速存储器的连续读出动作进行说明。在连续读出动作中,与通常的页读出不同,控制器150对存储单元阵列110_1与存储单元阵列110_2的阵列读出的时机各别地进行控制。

[0110]

当经由输入输出电路120接收到连续读取命令及地址时,控制器150判别命令,并对从开始页到结束页的多个页的连续读出进行控制。连续读出是通过命令结束,或者是在进行了所指定的页的读出时结束。

[0111]

图8是用于说明本实施例连续读出的动作示意图。如图1所示,从存储单元阵列一次性读出一页的数据,并将所读出的数据同时传送至锁存器l1的第一高速缓存c0及第二高速缓存c1,但在闪速存储器100的连续读出中,以不同的时机从存储单元阵列110_1、存储单元阵列110_2读出1/2页的数据,并将所读出的数据以不同的时机传送至锁存器l1的第一高速缓存c0及第二高速缓存c1。

[0112]

具体而言,从存储单元阵列110_1读出某页的前1/2页的数据,所读出的数据被传送至锁存器l1的第一高速缓存c0,并保持于其中。在存储单元阵列110_1的读出后,从存储单元阵列110_2进行某页的后1/2页的读出,所读出的数据被传送至锁存器l1的第二高速缓存c1,并保持于其中。

[0113]

接着,锁存器l1的第一高速缓存c0及第二高速缓存c1中所保持的数据被传送至锁存器l2的第一高速缓存c0及第二高速缓存c1,并保持于其中。锁存器l2的第一高速缓存c0中所保持的数据通过传送电路220_1传送至ecc电路130,在此处,进行数据的错误检测和校正,然后,通过传送电路220_1传送至输入输出电路120,在此处,与外部时钟信号exclk同步地输出。在利用ecc电路130进行处理的期间中,读出下一页的前1/2页的数据,数据保持于锁存器l1的第一高速缓存c0。

[0114]

响应锁存器l2的数据被传送至输入输出电路120而锁存器l1的第一高速缓存c0的数据被传送至锁存器l2的第一高速缓存c0,且从存储单元阵列110_1读出下一页(从所输出的页起的前两页)的前1/2页的数据,数据被传送至锁存器l1的第一高速缓存c0。

[0115]

存储单元阵列110_2的读出是与存储单元阵列110_1的读出同样地进行。控制器150对存储单元阵列110_2的阵列读出的时机进行控制,以使在锁存器l2的第一高速缓存c0的数据与外部时钟信号exclk同步地输出之后,锁存器l2的第二高速缓存c1的数据与外部时钟信号exclk同步地连续输出。

[0116]

图9是基于本实施例连续读出动作的具体时序图。图中的虚线所示的区域表示锁存器l1、锁存器l2释放的状态。即便重写也不会破坏数据。页p0、页p1的读出与通常的页读出相同,页p0、页p1是以相同的时机从存储单元阵列110_1、存储单元阵列110_2读出。连续读出是从页p2开始。当锁存器l2的第一高速缓存c0中所保持的页p0的数据的输出(输入输出电路120)结束时,响应于此,锁存器l1的第一高速缓存c0的页p1的数据被传送至锁存器l2的第一高速缓存c0,且从存储单元阵列110_1读出页p2的前1/2页的数据,此被传送至锁存器l1的第一高速缓存c0,并保持于其中。从锁存器l1向锁存器l2的数据传送时间与阵列

读出所需要的时间相比非常短,因此在将阵列读出的数据传送至锁存器l1的时间点,锁存器l1被释放。

[0117]

接着,在锁存器l2的第二高速缓存c1中所保持的页p0的数据的输出中,对锁存器l2的第一高速缓存c0中所保持的页p1的数据进行ecc处理。当锁存器l2的第二高速缓存c1中所保持的页p0的数据的输出结束时,响应于此,锁存器l1的第二高速缓存c1的页p1的数据被传送至锁存器l2的第二高速缓存c1,且从存储单元阵列110_2读出页p2的后1/2页的数据,此被传送至锁存器l1的第二高速缓存c1,并保持于其中。以后,以同样的方式进行页的连续读出。

[0118]

作为进行连续读出的制约,需要满足式(4)。

[0119]

tecc(1/2页)<tdout(1/2页)

…

(4)

[0120]

tdout由外部时钟信号exclk的频率决定。为了减小tecc,也可设为ecc电路130包括多个ecc电路,通过多个ecc电路并行地进行数据的错误检测和校正。

[0121]

如此,在本实施例的连续读出中,通过以不同的时机从存储单元阵列110_1、存储单元阵列110_2读出1/2页的数据,在锁存器l2的第一高速缓存c0的数据的输出后,从存储单元阵列110_1读出的1/2页的数据被传送至锁存器l1的第一高速缓存c0,在锁存器l2的第二高速缓存c1的数据的输出后,从存储单元阵列110_2读出的1/2页的数据被传送至锁存器l1的第二高速缓存c1,由此,避免在以往的连续读出动作中由于外部时钟信号exclk的频率变慢而保持于锁存器l1的数据被从存储单元阵列读出的数据破坏,可不受外部时钟信号exclk的频率的制约地进行页的连续读出。另外,也不需要如以往那样准备状态寄存器,用户进行阵列读取的时机的切换设定。

[0122]

进而,在本实施例的连续读出中,可减少阵列读出时的峰值电流。在现有的阵列读出中,对一页的位线进行预充电,因此产生大的峰值电流,使存储单元阵列110_1、存储单元阵列110_2以分别的时机运行而对1/2页的位线进行预充电,因此可减小峰值电流。由此,可使芯片内部的供给电压稳定化,提高电路动作的可靠性。

[0123]

接着,对本发明的实施例的变形例进行说明。在之前的实施例中,两阵列以存储单元阵列110_1、存储单元阵列110_2的动作在功能上分离的方式形成于同一芯片上,但在本变形例中,如图10(a)所示,闪速存储器100b以两个存储单元阵列在物理上分离的方式包括两个芯片300_1、300_2。两个芯片300_1、300_2可层叠,也可并行地配置。形成于芯片300_1的多个输入输出用的内部焊垫310_1经由内部配线320而电连接于对应的输入输出用的外部端子330,同样地,形成于芯片300_2的多个输入输出用的内部焊垫320_2经由内部配线320而电连接于对应的输入输出用的外部端子330。

[0124]

图10(b)是表示各芯片的内部结构的框图。芯片300_1包括:存储单元阵列340_1,形成有多个nand串;外围电路350_1,形成有字线选择电路或页缓冲器/读出电路等;控制器360_1,对芯片300_1的动作进行控制;以及输入输出电路370_1,连接于内部焊垫310_1。另一个芯片300_2具有与芯片300_1相同的结构。

[0125]

芯片300_1、芯片300_2经由外部端子330而连接于主计算机380。从主计算机380输出的命令(读出、编程、擦除等)、地址等经由外部端子330以共用的方式输入至芯片300_1、芯片300_2。当从主计算机380输入连续读出的命令及地址时,控制器360_1、控制器360_2如按照图9所示的时序图所示,在各个芯片300_1、芯片300_2中进行连续读出的控制。控制器

360_1进行前1/2页的读出,并使所读出的数据经由输入输出电路370_1从外部端子330输出,控制器360_2进行后1/2页的读出,并使所读出的数据经由输入输出电路370_2从外部端子330输出。如此,从外部端子330输出多个页的连续读出的数据。

[0126]

对本发明的优选实施方式进行了详述,但本发明并不限定于特定的实施方式,能够在权利要求所记载的本发明的主旨的范围内进行各种变形及变更。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1