支持DBI接口的存储器件和存储器件的操作方法与流程

支持dbi接口的存储器件和存储器件的操作方法

1.相关申请的交叉引用

2.本专利申请要求在韩国知识产权局于2020年9月29日提交的第10-2020-0127525号韩国专利申请和于2021年2月9日提交的第10-2021-0018531号韩国专利申请的优先权,这些韩国专利申请的公开内容通过引用全部并入于此。

技术领域

3.发明构思涉及存储器件,并且更具体地涉及支持数据总线反转(dbi)接口的存储器件和存储器件的操作方法。

背景技术:

4.存储系统包括存储控制器和存储器件。存储控制器和存储器件经由多条数据信号线彼此交换数据。存储控制器和存储器件可以使用dbi接口彼此通信以降低功耗。存储控制器和存储器件中的一者可以充当发送器件并且另一者可以充当接收器件。发送器件可以通过使用dbi编码方法生成发送数据,将发送数据发送到接收器件,并且将dbi信号和发送数据一起发送到接收器件。接收器件可以使用dbi信号解码发送数据。

技术实现要素:

5.发明构思的至少一个实施例提供能够提高数据发送效率同时减少数据发送的功耗和存储芯片尺寸的存储器件和存储器件的操作方法。

6.根据发明构思的实施例,提供了一种存储器件,所述存储器件包括存储单元阵列、页面缓冲器、控制逻辑电路、多个输入/输出引脚、数据总线反转(dbi)引脚和接口电路。所述存储单元阵列包括多个存储单元。所述页面缓冲器连接到所述存储单元阵列。所述控制逻辑电路被配置为控制所述存储单元阵列的操作。所述多个输入/输出引脚被配置为从控制器分别接收多个数据信号。所述数据总线反转(dbi)引脚被配置为从所述控制器接收dbi信号。所述接口电路被配置为:对来自所述多个数据信号和所述dbi信号的具有逻辑值1的位的第一数量和具有逻辑值0的位的第二数量进行计数,并且基于所述第一数量和所述第二数量,向所述页面缓冲器或所述控制逻辑电路提供所述多个数据信号。

7.根据发明构思的实施例,提供了一种存储器件,所述存储器件包括多个存储芯片,所述多个存储芯片被配置为从控制器接收包括报头(header)和数据区域的数据包(packet)。每一个所述存储芯片包括:多个输入/输出焊盘;数据总线反转(dbi)焊盘,所述数据总线反转(dbi)焊盘被配置为从所述控制器接收dbi信号;以及接口电路。所述输入/输出焊盘被配置为从所述控制器分别接收多个数据信号。所述dbi焊盘被配置为从所述控制器接收dbi信号。所述接口电路被配置为对来自所述多个数据信号和所述dbi信号的具有逻辑值1的位的第一数量和具有逻辑值0的位的第二数量进行计数,并且基于所述第一数量和所述第二数量将所述多个数据信号确定为所述报头或所述数据区域。

8.根据发明构思的实施例,提供了一种存储器件,所述存储器件包括存储单元阵列、

页面缓冲器、控制逻辑电路、多个输入/输出引脚、数据总线反转(dbi)引脚和接口电路。所述存储器件被配置为从控制器接收包括报头和数据区域的数据包。所述存储单元阵列包括多个存储单元。所述页面缓冲器连接到所述存储单元阵列。所述控制逻辑电路被配置为控制所述存储单元阵列的操作。所述输入/输出引脚被配置为分别从所述控制器接收多个数据信号。所述dbi引脚被配置为从所述控制器接收dbi信号。所述接口电路被配置为:对来自所述多个数据信号和所述dbi信号的具有逻辑值1的位的第一数量和具有逻辑值0的位的第二数量进行计数,基于所述第一数量和所述第二数量将所述多个数据信号确定为所述报头或所述数据区域,基于所述报头中包括的位将所述数据区域确定为数据、命令或地址,向所述页面缓冲器提供所述数据,以及向所述控制逻辑电路提供所述命令或所述地址。

9.根据发明构思的实施例,提供了一种存储器件,所述存储器件包括多个存储芯片。所述多个存储芯片中的每一个存储芯片包括存储单元阵列、多个输入/输出焊盘、数据总线反转(dbi)焊盘和接口电路。所述存储器件被配置为从控制器接收包括报头和数据区域的数据包。所述存储单元阵列包括多个存储单元。所述输入/输出焊盘被配置为分别从所述控制器接收多个数据信号。所述dbi焊盘被配置为从所述控制器接收dbi信号。所述接口电路被配置为:对来自所述多个数据信号和所述dbi信号的具有逻辑值1的位的第一数量和具有逻辑值0的位的第二数量进行计数,基于所述第一数量和所述第二数量将所述多个数据信号确定为所述报头或所述数据区域,基于所述报头中包括的位确定所述存储芯片之中的选择的存储芯片。

附图说明

10.从结合附图进行的以下详细描述,将更清楚地理解发明构思的各实施例,在附图中:

11.图1为示出根据发明构思的实施例的存储系统的框图;

12.图2为示出根据发明构思的实施例的存储系统的示意性框图;

13.图3为示出根据发明构思的实施例的根据dbi接口的数据信号的表;

14.图4为详细示出根据发明构思的实施例的存储器件的框图;

15.图5为示出根据发明构思的实施例的存储系统的框图;

16.图6为示出根据发明构思的实施例的多个数据信号和dbi信号的表;

17.图7为示出根据发明构思的实施例的对应于数据区域的信号和对应于命令/地址区域的信号的表;

18.图8为示出根据发明构思的实施例的存储系统的框图;

19.图9为示出根据发明构思的实施例的多个数据信号和dbi信号的表;

20.图10为示出根据发明构思的实施例的对应于数据区域的信号和对应于命令/地址区域的信号的表;

21.图11为根据发明构思的实施例的存储系统的操作方法的流程图;

22.图12为根据发明构思的实施例的存储系统的操作方法的流程图;

23.图13为示出根据发明构思的实施例的存储系统的框图;

24.图14为示出根据发明构思的实施例的数据包类型通信的示例的图;

25.图15为示出根据发明构思的实施例的命令报头、数据报头和地址报头的表;

26.图16为示出根据发明构思的实施例的数据包类型通信的另一示例的图;

27.图17为示出根据发明构思的实施例的第一存储芯片的框图;

28.图18为根据发明构思的实施例的存储系统的操作方法的流程图;

29.图19为示出根据发明构思的实施例的存储系统的框图;

30.图20为用于描述根据发明构思的实施例的可以应用到存储器件的b-vnand结构的图。

具体实施方式

31.图1为示出根据发明构思的实施例的存储系统ms的框图。

32.参考图1,存储系统ms可以包括存储器件11和存储控制器12(例如,控制电路)。存储系统ms可以支持多个信道(channel)ch1至chm,并且存储控制器12可以经由信道ch1至chm连接到存储器件11。例如,存储系统ms可以实施为类似固态硬盘(ssd)的存储设备(storage device)。在本说明书中,术语“控制器”可以表示“存储控制器”。

33.存储器件11可以包括多个非易失性存储器nvm11至nvmmn。非易失性存储器nvm11至nvmmn可以经由对应路(way)各自连接到信道ch1至chm之一。例如,非易失性存储器nvm11至nvm1n可以经由路w11至w1n连接到第一信道ch1,非易失性存储器nvm21至nvm2n可以经由路w21至w2n连接到第二信道ch2。在示例实施例中,非易失性存储器nvm11至nvmmn可以各自实施为能够根据来自存储控制器200的单独命令操作的任意存储器单元(memory unit)。例如,非易失性存储器nvm11至nvmmn可以各自实施为芯片或裸片,但是发明构思不限于此。

34.存储控制器12可以经由信道ch1至chm与存储器件11交换信号。例如,存储控制器12可以经由信道ch1至chm将命令cmda至cmdm、地址addra至addrm以及数据dataa至datam发送到存储器件11,或者从存储器件11接收数据dataa至datam。

35.经由每一个信道,存储控制器12可以从连接到对应信道的非易失性存储器nvm11至nvmmn之中选择非易失性存储器,并且与选择的非易失性存储器进行信号发送和接收。例如,存储控制器12可以从连接到第一信道ch1的非易失性存储器nvm11至nvm1n之中选择非易失性存储器nvm11。存储控制器12可以经由第一信道ch1将命令cmda、地址addra和数据dataa发送到选择的非易失性存储器nvm11,或者从选择的非易失性存储器nvm11接收数据dataa。

36.存储控制器12可以经由不同信道并行地将信号发送到存储器件11以及从存储器件11接收信号。例如,在命令cmda正在经由第一信道ch1发送到存储器件11时,存储控制器12可以经由第二信道ch2将命令cmdb发送到存储器件11。例如,在数据dataa正在经由第一信道ch1从存储器件11被接收时,存储控制器12可以经由第二信道ch2从存储器件11接收数据datab。

37.存储控制器12可以控制存储器件11的整体操作。存储控制器12可以通过经由信道ch1至chm发送信号,控制连接到信道ch1至chm的非易失性存储器nvm11至nvmmn中的每一者。例如,存储控制器12可以通过经由第一信道ch1发送命令cmda和地址addra,控制从非易失性存储器nvm11至nvm1n之中选择的非易失性存储器。

38.非易失性存储器nvm11至nvmmn可以各自在存储控制器12的控制下操作。例如,非易失性存储器nvm11可以根据经由第一信道ch1提供的命令cmda和地址addra对数据dataa

编程。例如,非易失性存储器nvm21可以根据经由第二信道ch2提供的命令cmdb和地址addrb读取数据datab并且将读取数据datab发送到存储控制器12。

39.尽管图1示出存储器件11经由m个信道与存储控制器12通信并且存储器件11包括与每一个信道对应的n个非易失性存储器,但是信道的数目以及连接到一个信道的非易失性存储器的数目可以变化。

40.例如,在对非易失性存储器nvm11执行读取操作的情况下,当存储控制器12经由第一信道ch1发送页面读取命令时,非易失性存储器nvm11在读取时间tr期间生成读取数据。接着,当存储控制器12经由第一信道ch1发送随机读取命令时,非易失性存储器nvm11经由第一信道ch1将读取数据发送到存储控制器12。在这时,随机读取命令的发送时间可以定义为tcmd,并且读取数据的发送时间可以定义为tdma。

41.在实施例中,可以执行路交织(way interleaving)操作以改善输入/输出(i/o)效率。例如,存储控制器12可以将页面读取命令顺序地发送到连接到第一信道ch1的非易失性存储器nvm11至nvm1n,由此使非易失性存储器nvm11至nvm1n的读取数据生成时间交叠。当非易失性存储器nvm11至nvm1n之中的第一非易失性存储器的读取数据生成操作结束时,存储控制器12可以经由第一信道ch1发送随机读取命令并且从第一非易失性存储器接收读取数据。接着,存储控制器12可以经由第一信道ch1发送随机读取命令并且从下一个非易失性存储器接收读取数据。在这时,在n个非易失性存储器的数据读取操作的情况下,i/o效率可以表示为下面的等式1。

[0042][0043]

尽管tdma随着存储控制器12和存储器件11之间的带宽增加而减小,但是由于在命令发送的时间的时间参数或者在地址发送的时间的时间参数导致的命令开销,所以tcmd的减小比较不显著。结果,尽管带宽增加,但是i/o效率可能退化。因此,将在下文描述根据发明构思的通过降低tcmd改善i/o效率的各种实施例以及通过tcmd和tdma的交叠改善i/o效率的各种实施例。

[0044]

为了降低存储器件11和存储控制器12之间的数据发送/接收的功耗,存储器件11和存储控制器12可以通过使用利用dbi信号的dbi接口来发送和接收数据。例如,存储控制器12可以通过使用dbi编码方法选择性地反转数据的至少一些位来生成发送数据,并且将表示数据的至少一些位被反转的dbi信号与发送数据一起发送到存储器件11。当存储系统ms支持信道ch1至chm时,存储控制器12可以生成分别对应于信道ch1至chm的多个dbi信号。类似地,存储器件11可以通过使用dbi编码方法选择性地反转数据的至少一些位来生成发送数据,并且将表示数据的至少一些位被反转的dbi信号与发送数据一起发送到存储控制器12。

[0045]

根据发明构思的实施例,数据区域和命令区域均通过使用dbi接口中的dbi信号被定义,因而可以通过降低命令开销而降低tcmd。此外,根据发明构思的至少一个实施例,当在dbi接口中执行数据包类型通信时,报头/报尾(trailer)和数据区域可以通过使用dbi信号来区分,并且通过使用报头中包括的信息,数据区域可以被确定为命令、地址或数据,因而tcmd和tdma可以被交叠。报尾也可以被称为尾部(tail)。

[0046]

图2为示出根据发明构思的实施例的存储系统10的示意性框图。

[0047]

参考图2,存储系统10包括存储器件100和存储控制器200。存储器件100可以对应于非易失性存储器nvm11至nvmmn之中的使用图1的信道ch1至chm之一与存储控制器12通信的非易失性存储器。存储控制器200可以对应于图1的存储控制器12。

[0048]

存储器件100可以包括第一引脚p11至第四引脚p14、接口(i/f)电路110、页面缓冲器120、存储单元阵列130和控制逻辑电路140。在本说明书中,页面缓冲器120和存储单元阵列130可以被称为数据路径块dpb。在一些实施例中,数据路径块dpb还可以包括数据i/o电路。然而,发明构思的各实施例不限于此。例如,在一些实施例中,数据i/o电路可以包括在i/f电路110中。

[0049]

i/f电路110可以经由第一引脚p11从存储控制器200接收多个数据信号dq或者将数据信号dq发送到存储控制器200。命令cmd、地址addr和数据data可以经由数据信号dq被发送。例如,数据信号dq可以分别经由多条数据信号线被发送,并且多条数据信号线可以构成图1的信道ch1至chm中的一个信道。根据各实施例,数据信号dq可以被称为多个数据输入/输出信号dq或多个输入/输出信号dq。在下文中,将基于第一引脚p11的数量为8的实施例给出描述。然而,发明构思的各实施例不限于此。例如,第一引脚p11的数量可以根据各实施例变化。

[0050]

i/f电路110可以经由第二引脚p12从存储控制器200接收dbi信号dbi或者将dbi信号dbi发送到存储控制器200。例如,dbi信号dbi可以是1位信号。然而,发明构思的各实施例不限于此。例如,dbi信号dbi可以是多位信号。在这种情况下,第二引脚p12可以由多个引脚实施。在存储器件100的输入数据data的操作期间,i/f电路110可以经由第一引脚p11接收多个数据信号dq并且经由第二引脚p12接收dbi信号dbi。在存储器件100的输出数据data的操作期间,i/f电路110可以经由第一引脚p11发送多个数据信号dq并且经由第二引脚p12发送dbi信号dbi。稍后将参考图3给出dbi信号dbi和数据信号dq的发送和接收的详细描述。

[0051]

i/f电路110可以经由第三引脚p13从存储控制器200接收数据选通信号dqs或者将数据选通信号dqs发送到存储控制器200。i/f电路110可以经由第四引脚p14从存储控制器200接收读取使能信号nre。

[0052]

在存储器件100的输出数据data的操作期间,i/f电路110可以在输出数据data之前经由第四引脚p14接收切换(toggle)的读取使能信号nre。i/f电路110可以生成基于读取使能信号nre的切换而切换的数据选通信号dqs。例如,i/f电路110可以生成这样的数据选通信号dqs:该数据选通信号dqs在基于读取使能信号nre的切换开始时间的预定延迟(例如,tdqsre)之后开始切换。i/f电路110可以基于数据选通信号dqs的切换时序,发送包括数据data的多个数据信号dq。因此,数据data可以被对齐到数据选通信号dqs的切换时序并且被发送到存储控制器200。

[0053]

在存储器件100的输入数据data的操作期间,当包括数据data的多个数据信号dq从存储控制器200被接收时,i/f电路110可以从存储控制器200与数据data一起接收切换的数据选通信号dqs。i/f电路110可以基于数据选通信号dqs的切换时序从数据信号dq获得数据data。例如,i/f电路110可以通过在数据选通信号dqs的上升沿和下降沿对数据信号dq采样来获得数据data。

[0054]

在一些实施例中,存储器件100还可以包括用于从存储控制器200接收芯片使能信号nce的引脚。i/f电路110可以根据芯片使能信号nce经由第一引脚p11至第四引脚p14与存

储控制器200交换信号。例如,当芯片使能信号nce处于启用状态(例如,低电平)时,i/f电路110可以经由第一引脚p11至第四引脚p14与存储控制器200交换信号。

[0055]

在一些实施例中,存储器件100还可以包括输出就绪/忙碌输出信号nr/b的引脚。i/f电路110可以经由就绪/忙碌输出信号nr/b将关于存储器件100的状态信息发送到存储控制器200。当存储器件100处于忙碌状态时(即,当存储器件100的内部操作正被执行时),i/f电路110可以将指示忙碌状态的就绪/忙碌输出信号nr/b发送到存储控制器200。当存储器件100处于就绪状态时(即,当存储器件100的内部操作不被执行或者被完成时),i/f电路110可以将指示就绪状态的就绪/忙碌输出信号nr/b发送到存储控制器200。例如,在存储器件100响应于页面读取命令正在从存储单元阵列130读取数据data时,i/f电路110可以将指示忙碌状态(例如,低电平)的就绪/忙碌输出信号nr/b发送到存储控制器200。例如,在存储器件100响应于编程命令将数据data编程到存储单元阵列130的时,i/f电路110可以将指示忙碌状态的就绪/忙碌输出信号nr/b发送到存储控制器200。

[0056]

控制逻辑电路140可以控制存储器件100的各种操作。控制逻辑电路140可以接收从i/f电路110获得的命令cmd和地址addr。控制逻辑电路140可以根据命令cmd和地址addr生成用于控制存储器件100的其它组件的控制信号。例如,控制逻辑电路140可以生成各种控制信号,以将数据data编程到存储单元阵列130或者从存储单元阵列130读取数据data。

[0057]

页面缓冲器120可以从i/f电路110接收数据data。页面缓冲器120可以被用作用于在控制逻辑电路140的控制下将数据写入到存储单元阵列130的写入驱动器。此外,页面缓冲器120可以被用作用于在控制逻辑电路140的控制下从存储单元阵列130接收数据的感测放大器。存储单元阵列130可以在控制逻辑电路140的控制下存储从页面缓冲器120获得的数据data。存储单元阵列130可以将在控制逻辑电路140的控制下存储的数据data输出到页面缓冲器120。

[0058]

存储单元阵列130可以包括多个存储单元。例如,存储单元可以是闪存单元。然而,发明构思的各实施例不限于此。例如,存储单元可以包括电阻随机存取存储(rram)单元、铁电随机存取存储(fram)单元、相变随机存取存储(pram)单元、晶闸管随机存取存储(tram)单元或磁随机存取存储(mram)单元。在下文中,将基于存储单元是nand闪存单元的各实施例描述发明构思的各实施例。

[0059]

在实施例中,i/f电路110对经由第一引脚p11接收的多个数据信号dq和经由第二引脚p12接收的dbi信号之中的具有逻辑值1的位的第一数量和具有逻辑值0的位的第二数量进行计数,并且基于计数的第一数量和计数的第二数量将数据信号dq提供到数据路径块dpb或控制逻辑电路140。例如,当第一数量小于或等于第二数量时,i/f电路110可以确定数据信号dq包括数据data并且将数据信号dq提供到数据路径块dpb。例如,当第一数量大于第二数量时,i/f电路110可以确定数据信号dq包括命令cmd或地址addr并且将数据信号dq提供到控制逻辑电路140。

[0060]

根据本实施例,基于数据信号dq和dbi信号bdi中包括的具有逻辑值1的位的第一数量和具有逻辑值0的位的第二数量,支持dbi接口的存储器件100将多个数据信号dq确定为命令cmd、地址addr或数据data。因此,由于存储器件100不需要从存储控制器200接收指示数据信号dq是命令cmd的标志信号(例如,命令锁存使能信号cle),所以存储器件100不需要包括用于接收命令锁存使能信号cle的引脚。此外,由于存储器件100不需要从存储控制

器200接收指示数据信号dq是地址addr的标志信号(例如,地址锁存使能信号ale),所以存储器件100不需要包括用于接收地址锁存使能信号ale的引脚或焊盘。另外,由于存储器件100不需要接收用于区分命令cmd、地址addr和数据data的时钟信号(例如,写入使能信号nwe),所以存储器件100不需要包括用于接收写入使能信号nwe的引脚或焊盘。结果,由于存储器件100可以包括更少的引脚或焊盘,所以芯片尺寸可以降低。

[0061]

此外,由于存储器件100可以不接收命令锁存使能信号cle和地址锁存使能信号ale而将经由第一引脚p11接收的多个数据信号dq确定为命令、地址或数据,所以在命令锁存使能信号cle的启用阶段中出现的开销以及在地址锁存使能信号ale的启用阶段中出现的开销可以被消除,并且在地址锁存使能信号ale过渡到禁用阶段之后出现的开销也可以被消除。结果,由于存储器件100与已有的存储器件相比可以降低tcmd,所以i/o效率可以显著改善。

[0062]

在实施例中,存储器件100和存储控制器200彼此交换包括报头、数据区域和报尾的数据包。i/f电路110可以对来自经由第一引脚p11接收的多个数据信号dq和经由第二引脚p12接收的dbi信号的具有逻辑值1的位的第一数量和具有逻辑值0的位的第二数量进行计数,并且基于计数的第一数量和计数的第二数量将数据信号dq确定为报头、数据区域或报尾。稍后将参考图13至图19给出其更详细描述。

[0063]

存储控制器200可以包括第一引脚p21至第四引脚p24和i/f电路210。第一引脚p21至第四引脚p24可以分别对应于存储器件100的第一引脚p11至第四引脚p14。i/f电路210可以经由第一引脚p21将数据信号dq发送到存储器件100或者从存储器件100接收数据信号dq。i/f电路210可以经由第二引脚p22将dbi信号dbi发送到存储器件100或者从存储器件100接收dbi信号dbi。i/f电路210可以经由第三引脚p23从存储器件100接收数据选通信号dqs或者将数据选通信号dqs发送到存储器件100。i/f电路210可以经由第四引脚p24将读取使能信号nre发送到存储器件100。

[0064]

在存储器件100的输出数据data的操作期间,i/f电路210可以生成切换的读取使能信号nre并且将读取使能信号nre发送到存储器件100。例如,i/f电路210可以在数据data被输出之前生成从固定状态(例如,高电平或低电平)改变到切换状态的读取使能信号nre。因此,可以在存储器件100中生成基于读取使能信号nre切换的数据选通信号dqs。i/f电路210可以从存储器件100接收包括数据data的数据信号dq以及切换的数据选通信号dqs。i/f电路210可以基于数据选通信号dqs的切换时序从数据信号dq获得数据data。

[0065]

在存储器件100的输入数据data的操作期间,i/f电路210可以生成切换的数据选通信号dqs。例如,i/f电路210可以在数据data被发送之前生成从固定状态(例如,高电平或低电平)改变到切换状态的数据选通信号dqs。i/f电路210可以基于数据选通信号dqs的切换时序将包括数据data的数据信号dq发送到存储器件100。

[0066]

在一些实施例中,存储控制器200还可以包括用于将芯片使能信号nce发送到存储器件100的引脚。i/f电路210可以经由第一引脚p21至第四引脚p24与由芯片使能信号nce选择的存储器件100交换信号。在一些实施例中,存储控制器200还可以包括用于从存储器件100接收就绪/忙碌输出信号nr/b的引脚。i/f电路210可以基于就绪/忙碌输出信号nr/b确定关于存储器件100的状态信息。

[0067]

图3为示出根据发明构思的实施例的根据dbi接口的数据信号的表。

[0068]

一起参考图2和图3,例如,第一引脚p11的数量可以是8并且第二引脚p12的数量可以是1。然而,发明构思的各实施例不限于此。例如,第一引脚p11的数量可以变化并且第二引脚p12的数量也可以变化。存储控制器200可以将8位数据信号dq[7:0]和1位dbi信号dbi发送到存储器件100。此外,存储器件100可以将8位数据信号dq[7:0]和1位dbi信号dbi发送到存储控制器200。

[0069]

一个信道可以包括多条信号线,例如,8条数据信号线。当对应于位1的数据信号经由数据信号线被发送时,直流(dc)电流可以比较大。当对应于位0的数据信号经由数据信号线被发送时,dc电流可以比较小。因此,为了降低信道的dc电流,在经由多条信号线分别发送的数据信号中具有逻辑值1的位的数量可以小于具有逻辑值0的位的数量。

[0070]

当原始数据信号中具有逻辑值1的位的数量不大于具有逻辑值0的位的数量时,dbi信号dbi可以被生成为禁用(disable)电平信号,即,位0。在这种情况下,原始数据信号中包括的位不被转换,并且原始数据信号经由数据信号线被发送。例如,当原始数据信号为00000001时,dbi信号dbi被生成为位0,作为dbi编码的结果而生成的转换数据信号与原始数据信号相同,并且转换数据信号00000001和dbi信号dbi被发送。在这种情况下,数据信号和dbi信号dbi中包括的具有逻辑值1的位的总数量为1,并且在dbi编码之前和之后具有逻辑值1的位的总数量相同。

[0071]

另一方面,当原始数据信号中具有逻辑值1的位的数量大于具有逻辑值0的位的数量时,dbi信号dbi可以被生成为启用(enable)电平信号,即,位1。在这种情况下,原始数据信号中包括的位被转换或反转以生成转换数据信号,并且转换数据信号经由数据信号线被发送。例如,当原始数据信号为00011111时,dbi信号dbi被生成为位1,作为dbi编码的结果生成转换数据信号11100000,并且转换数据信号11100000和dbi信号dbi被发送。在这种情况下,数据信号和dbi信号dbi中包括的具有逻辑值1的位的总数量为4,并且与在dbi编码之前具有逻辑值1的位的总数量相比,具有逻辑值1的位的总数量减小。因此,用于数据发送的功耗可以降低。

[0072]

图4为详细示出根据发明构思的实施例的存储器件100的框图。

[0073]

一起参考图2和图4,存储器件100包括i/f电路110、页面缓冲器120、存储单元阵列130、控制逻辑电路140、电压生成器150和行译码器160(例如,译码器电路)。i/f电路110可以经由第一引脚p11从存储控制器200分别接收多个数据信号dq,并且可以经由第二引脚p12从存储控制器200接收dbi信号dbi。i/f电路110可以包括解码器111(例如,解码器电路),并且解码器111可以包括数据信号解码器1111和dbi解码器1112。

[0074]

数据信号解码器1111可以对来自数据信号dq和dbi信号dbi的具有逻辑值1的位的第一数量和具有逻辑值0的位的第二数量进行计数,并且基于计数的第一数量和计数的第二数量确定数据信号dq的发送路径。例如,当数据信号解码器1111确定数据信号dq包括命令cmd或地址addr时,数据信号解码器1111可以将命令cmd或地址addr提供到控制逻辑电路140。例如,当数据信号解码器1111确定数据信号dq包括数据data时,数据信号解码器1111可以将数据data提供到dbi解码器1112或页面缓冲器120。

[0075]

dbi解码器1112可以通过基于dbi信号dbi对数据信号dq执行dbi解码来生成解码的数据信号。例如,dbi解码器1112可以通过基于dbi信号dbi对数据信号dq中包括的数据执行dbi解码,生成解码的数据data,并且将解码的数据data提供到页面缓冲器120。

[0076]

控制逻辑电路140可以控制存储器件100内部的各种操作。控制逻辑电路140可以响应于来自i/f电路110的命令cmd和/或地址addr输出各种控制信号。例如,控制逻辑电路140可以输出电压控制信号ctrl_vol、行地址x-addr和列地址y-addr。

[0077]

存储单元阵列130可以经由位线bl连接到页面缓冲器120,并且可以经由字线wl、串选择线ssl和接地选择线gsl连接到行译码器160。在示例实施例中,存储单元阵列130可以包括三维存储单元阵列,并且三维存储单元阵列可以包括多个nand串。每一个nand串可以包括分别连接到垂直地堆叠在衬底上的字线的存储单元。第7,679,133号美国专利申请公开、第8,553,466号美国专利申请公开、第8,654,587号美国专利申请公开、第8,559,235号美国专利申请公开和第2011/0233648号美国专利申请公开通过引用被并入于此。在示例实施例中,存储单元阵列130可以包括二维存储单元阵列,并且二维存储单元阵列可以包括沿行方向和列方向布置的多个nand串。

[0078]

页面缓冲器120可以响应于列地址y_addr从位线bl之中选择至少一条位线。页面缓冲器120可以依据操作模式作为写入驱动器或感测放大器来操作。例如,在编程操作期间,页面缓冲器120可以将对应于要被编程的数据的位线电压施加到选择的位线。在读取操作期间,页面缓冲器120可以通过感测选择的位线的电流或电压来感测存储单元中存储的数据。

[0079]

电压生成器150可以基于电压控制信号ctrl_vol生成用于执行编程操作、读取操作和擦除操作的各种类型的电压。例如,电压生成器150可以将编程电压、读取电压、编程验证电压或擦除电压生成为字线电压vwl。行译码器160可以响应于行地址x_addr从字线wl之中选择一条字线wl并且可以从串选择线ssl之中选择一条串选择线ssl。例如,行译码器160可以在编程操作期间将编程电压和编程验证电压施加到选择的字线并且可以在读取操作期间将读取电压施加到选择的字线。

[0080]

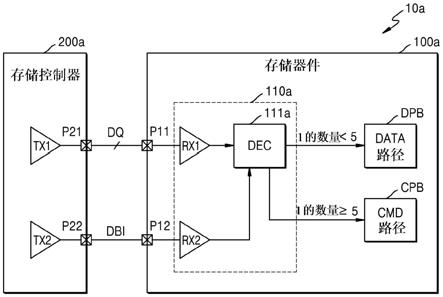

图5为示出根据发明构思的实施例的存储系统10a的框图。

[0081]

参考图5,存储系统10a包括存储器件100a和存储控制器200a。存储器件100a可以对应于图2的存储器件100的实施示例,并且存储控制器200a可以对应于图2的存储控制器200的实施示例。参考图2至图5在上面给出的描述可以应用到本实施例。

[0082]

存储控制器200a包括第一引脚p21、第二引脚p22、数据信号发送器tx1和dbi信号发送器tx2。存储器件100a包括第一引脚p11、第二引脚p12、i/f电路110a、数据路径块dpb和命令路径块cpb。例如,数据路径块dpb可以对应于图2的页面缓冲器120和存储单元阵列130,并且命令路径块cpb可以对应于图2的控制逻辑电路140。

[0083]

i/f电路110a对应于图2的i/f电路110的实施例,并且可以包括数据信号接收器rx1、dbi信号接收器rx2和解码器(dec)111a。数据信号接收器rx1可以将从第一引脚p11分别接收的数据信号dq提供到解码器111a。dbi信号接收器rx2可以将从第二引脚p12接收的dbi信号dbi提供到解码器111a。然而,发明构思的各实施例不限于此。例如,dbi信号接收器rx2可以将dbi信号dbi提供到数据路径块dpb。例如,数据信号接收器rx1和dbi信号接收器rx2可以实施为输入缓冲器。在实施例中,数据信号接收器rx1和dbi信号接收器rx2可以使用运算放大器实施。

[0084]

图6为示出根据发明构思的实施例的多个数据信号和dbi信号的表。

[0085]

参考图6,在应用dbi编码之前,无论多个数据信号dq[7:0]中包括的具有逻辑值0

的位的数量或者具有逻辑值1的位的数量如何,dbi信号dbi都可以具有禁用电平,即,具有逻辑值0的位。在dbi编码被应用之前多个数据信号dq[7:0]和dbi信号dbi可以划分为第一区域61和第二区域62,在第一区域61中具有逻辑值1的位的总数量小于具有逻辑值0的位的总数量,在第二区域62中具有逻辑值1的位的总数量大于具有逻辑值0的位的总数量。

[0086]

在dbi编码被应用之后,dbi信号dbi可以根据数据信号dq[7:0]中包括的具有逻辑值0的位的数量或者具有逻辑值1的位的数量被选择性地启用。因此,在应用dbi编码之后数据信号dq[7:0]和dbi信号dbi可以划分为第三区域63和第四区域64,在第三区域63中dbi信号处于禁用电平(即,具有逻辑值0的位),在第四区域64中dbi信号处于启用电平(即,具有逻辑值1的位)。就此而言,通过应用dbi编码,第一区域61可以被转换为第三区域63并且第二区域62可以被转换为第四区域64。

[0087]

图7为示出根据发明构思的实施例的对应于数据区域的信号和对应于命令/地址区域的信号的表。

[0088]

一起参考图5至图7,在应用dbi编码之后第三区域63和第四区域64可以被用作数据区域。因此,i/f电路110a可以对来自数据信号dq[7:0]和dbi信号dbi的具有逻辑值1的位的第一数量和具有逻辑值0的位的第二数量进行计数,当具有逻辑值1的位的第一数量小于或等于具有逻辑值0的位的第二数量时确定数据信号dq[7:0]对应于数据data,并且将数据data提供到数据路径块dpb。

[0089]

在实施例中,在应用dbi编码之前第二区域62可以被用作命令区域。在实施例中,在应用dbi编码之前第二区域62可以被用作地址区域。在实施例中,在应用dbi编码之前第二区域62可以被用作命令/地址区域。因此,i/f电路110a可以对来自数据信号dq[7:0]和dbi信号dbi的具有逻辑值1的位的第一数量和具有逻辑值0的位的第二数量进行计数,当具有逻辑值1的位的第一数量大于具有逻辑值0的位的第二数量时确定数据信号dq[7:0]对应于命令cmd或地址addr,并且将命令cmd或地址addr提供到命令路径块cpb。

[0090]

在实施例中,第五区域65可以被用作命令区域。在实施例中,第五区域65可以被用作地址区域。在实施例中,第五区域65可以被用作命令/地址区域。因此,i/f电路110a可以对来自数据信号dq[7:0]和dbi信号dbi的具有逻辑值1的位的第一数量和具有逻辑值0的位的第二数量进行计数,当具有逻辑值1的位的第一数量大于具有逻辑值0的位的第二数量时确定数据信号dq[7:0]对应于命令cmd或地址addr,并且将命令cmd或地址addr提供到命令路径块cpb。

[0091]

例如,当第一引脚p11的数量为8并且第二引脚p12的数量为1时,解码器111a可以将具有逻辑值1的位的第一数量与参考数量5进行比较。作为比较的结果,当具有逻辑值1的位的第一数量小于5时,可以认为数据信号dq[7:0]对应于包括第三区域63和第四区域64的数据区域,因此解码器111a可以向数据路径块dpb提供数据信号dq[7:0]。另一方面,作为比较的结果,当具有逻辑值1的位的第一数量不小于5时,可以认为数据信号dq[7:0]对应于包括第二区域62和第五区域65的命令/地址区域,因此解码器111a可以将数据信号dq[7:0]提供到命令路径块cpb。在实施例中,当存储控制器200a向存储器件100a发送命令或地址时,存储控制器200a发送具有第二区域62或第五区域65的格式的数据信号dq[7:0],当存储控制器200a向存储器件100a发送数据时,存储控制器200a发送具有第三区域63或第四区域64的格式的数据信号dq[7:0]。

[0092]

如上所述,i/f电路110a可以对来自数据信号dq[7:0]和dbi信号dbi的具有逻辑值1的位的第一数量和具有逻辑值0的位的第二数量进行计数。然而,发明构思的各实施例不限于此。在一些实施例中,i/f电路110a可以对来自数据信号dq[7:0]的具有逻辑值1的位的第一数量和具有逻辑值0的位的第二数量进行计数,并且基于计数的第一数量和计数的第二数量确定数据信号dq的发送路径。

[0093]

如上所述,当具有逻辑值1的位的第一数量小于或等于阈值(例如,具有逻辑值0的位的第二数量)时,i/f电路110a可以确定数据信号dq[7:0]对应于数据data,并且将数据data提供到数据路径块dpb。然而,发明构思的各实施例不限于此。根据一些实施例,i/f电路110a的端接逻辑(termination logic)可以对应于各种配置之一。例如,i/f电路110a的端接电阻器可以连接到电源电压端或接地电压端。因此,在一些实施例中,当具有逻辑值0的位的第二数量小于或等于阈值(例如,具有逻辑值1的位的第一数量)时,i/f电路110a可以确定数据信号dq[7:0]对应于数据data,并且将数据data提供到数据路径块dpb。

[0094]

如上所述,当具有逻辑值1的位的第一数量大于阈值(例如,具有逻辑值0的位的第二数量)时,i/f电路110a可以确定数据信号dq[7:0]对应于命令cmd或地址addr,并且将命令cmd或地址addr提供到命令路径块cpb。然而,发明构思的各实施例不限于此。根据一些实施例,i/f电路110a的端接逻辑可以对应于各种配置之一。例如,i/f电路110a的端接电阻器可以连接到电源电压端或接地电压端。因此,在一些实施例中,当具有逻辑值0的位的第二数量大于阈值(例如,具有逻辑值1的位的第一数量)时,i/f电路110a可以确定数据信号dq[7:0]对应于命令cmd或地址add,并且将命令cmd或地址addr提供到命令路径块cpb。

[0095]

图8为示出根据发明构思的实施例的存储系统10b的框图。

[0096]

参考图8,存储系统10b包括存储器件100b和存储控制器200b。存储器件100b可以对应于图2的存储器件100的实施示例,并且存储控制器200b可以对应于图2的存储控制器200的实施示例。参考图2至图5在上面给出的描述可以应用到本实施例。

[0097]

存储控制器200b包括第一引脚p21、第二引脚p22、数据信号发送器tx1和dbi信号发送器tx2。存储器件100b包括第一引脚p11、第二引脚p12、i/f电路110b、数据路径块dpb和命令路径块cpb。例如,数据路径块dpb可以对应于图2的页面缓冲器120和存储单元阵列130,并且命令路径块cpb可以对应于图2的控制逻辑电路140。

[0098]

i/f电路110b对应于图2的i/f电路110的实施例并且可以包括数据信号接收器rx1、dbi信号接收器rx2和解码器111b。数据信号接收器rx1可以将从第一引脚p11分别接收的多个数据信号dq提供到解码器111b。dbi信号接收器rx2可以将从第二引脚p12接收的dbi信号dbi提供到解码器111b。然而,发明构思的各实施例不限于此。例如,dbi信号接收器rx2也可以将dbi信号dbi提供到数据路径块dpb。例如,数据信号接收器rx1和dbi信号接收器rx2可以实施为输入缓冲器。在实施例中,输入缓冲器使用运算放大器实施。

[0099]

图9为示出根据发明构思的实施例的多个数据信号和dbi信号的表。

[0100]

参考图9,即使当存储器件100包括用于接收dbi信号dbi的第二引脚p12时,用户也可以不利用dbi编码并且将dbi信号dbi被禁用的dbi禁用模式设置为默认模式。在这种情况下,无论多个数据信号dq[7:0]中包括的具有逻辑值0的位的数量或者具有逻辑值1的位的数量如何,dbi信号dbi都可以具有禁用电平,即,具有逻辑值0的位。在dbi信号dbi处于禁用电平的dbi禁用模式中,数据信号dq[7:0]和dbi信号dbi可以划分为第一区域91和第二区域

92,在第一区域91中数据信号dq[7:0]中包括的具有逻辑值1的位的数量不大于具有逻辑值0的位的数量,在第二区域92中具有逻辑值1的位的数量大于具有逻辑值0的位的数量,并且第一区域91和第二区域92可以被用作数据区域。

[0101]

另一方面,在dbi信号dbi根据数据信号dq[7:0]被选择性地启用的dbi启用模式中,数据信号dq[7:0]和dbi信号dbi可以划分为第三区域93和第四区域94,在第三区域93中dbi信号dbi具有值0,在第四区域94中dbi信号dbi具有值1。在这种情况下,存储控制器200b可以通过启用用于第二区域92的dbi信号dbi来生成第四区域94,以定义命令区域或地址区域。

[0102]

图10为示出根据发明构思的实施例的对应于数据区域的信号和对应于命令/地址区域的信号的表。

[0103]

一起参考图8至图10,第一区域91和第二区域92在dbi禁用模式中可以被用作数据区域,在dbi禁用模式中无论数据信号dq[7:0]中包括的具有逻辑值1的位的数量和具有逻辑值0的位的数量如何,dbi信号dbi都被设置为禁用电平。因此,当dbi信号dbi处于禁用电平时,i/f电路110b可以确定数据信号dq[7:0]对应于数据data并且将数据data提供到数据路径块dpb。

[0104]

在实施例中,dbi信号具有启用电平的第四区域94可以被用作命令区域。在实施例中,dbi信号具有启用电平的第四区域94可以被用作地址区域。在实施例中,dbi信号具有启用电平的第四区域94可以被用作命令/地址区域。因此,当dbi信号dbi处于启用电平时,i/f电路110b可以确定数据信号dq[7:0]对应于命令cmd或地址addr并且将命令cmd或地址addr提供到命令路径块cpb。

[0105]

此外,在实施例中,dbi信号具有启用电平的第五区域95可以被用作命令区域。在实施例中,dbi信号具有启用电平的第五区域95可以被用作地址区域。在实施例中,dbi信号具有启用电平的第五区域95可以被用作命令/地址区域。因此,当dbi信号具有启用电平时,i/f电路110a可以确定数据信号dq[7:0]对应于命令cmd或地址addr,并且将命令cmd或地址addr提供到命令路径块cpb。

[0106]

图11为根据发明构思的实施例的存储系统的操作方法的流程图。参考图11,根据本实施例的存储器件的操作方法为使用dbi编码方案发送/接收数据的方法,并且可以例如由图2的存储器件100执行。在下文中,将一起参考图2和图11给出描述。

[0107]

在操作s110中,存储器件100从存储控制器200接收数据信号dq和dbi信号dbi。在操作s120中,存储器件100对数据信号dq和dbi信号dbi中的具有逻辑值1的位的第一数量和具有逻辑值0的位的第二数量进行计数。在操作s130中,存储器件100确定第一数量是否小于或等于第二数量。作为确定的结果,当第一数量小于或等于第二数量时,在操作s150中,存储器件100将数据信号dq提供到页面缓冲器120。作为确定的结果,当第一数量大于第二数量时,在操作s160中,存储器件100将数据信号dq提供到控制逻辑电路140。

[0108]

然而,发明构思的各实施例不限于此。根据一些实施例,存储器件100确定第二数量是否小于或等于第一数量。作为数量的结果,当第二数量小于或等于第一数量时,存储器件100将数据信号dq提供到页面缓冲器120。作为确定的结果,当第二数量大于或等于第一数量时,存储器件100将数据信号dq提供到控制逻辑电路140。

[0109]

图12为根据发明构思的实施例的存储系统的操作方法的流程图。参考图12,根据

本实施例的存储器件的操作方法可以对应于图11的操作方法的实施示例。因此,参考图11在上面给出的描述也可以应用到本实施例,并且与参考图11在上面给出的描述相同的描述将被省略。

[0110]

在操作s140中,存储器件100将数据信号dq确定为数据data并且基于dbi信号dbi执行数据data的dbi解码以生成解码的数据。例如,当具有逻辑值1的位的数量小于或等于具有逻辑值0的位的数量时,存储器件100可以确定数据信号是数据。dbi解码可以包括基于dbi信号dbi的值选择性地反转数据信号。在操作s150a中,存储器件100将解码的数据提供到页面缓冲器120。在操作s160a中,存储器件100将数据信号dq确定为命令cmd或地址addr并且将命令cmd或地址addr提供到控制逻辑电路140。例如,当具有逻辑值1的位的数量大于具有逻辑值0的位的数量时,存储器件100可以确定数据信号是命令cmd或地址addr。

[0111]

然而,发明构思的各实施例不限于此。根据一些实施例,当具有逻辑值0的位的数量小于或等于具有逻辑值1的位的数量时,存储器件100可以确定数据信号是数据。dbi解码可以包括基于dbi信号dbi的值选择性地反转数据信号,并且当具有逻辑值0的位的数量大于具有逻辑值1的位的数量时,存储器件100可以确定数据信号是命令cmd或地址addr。

[0112]

图13为示出根据发明构思的实施例的存储系统20的框图。

[0113]

参考图13,存储系统20包括存储器件300和存储控制器400。存储器件300和存储控制器400可以经由信道ch彼此连接。存储器件300可以包括第一存储芯片nvm1 310至第四存储芯片nvm4 340。存储器件300可以对应于图1的存储器件11,存储控制器400可以对应于图1的存储控制器12,并且信道ch可以对应于信道ch1至chm之中的一个信道。例如,信道ch可以对应于第一信道ch1,并且第一存储芯片310至第四存储芯片340可以对应于非易失性存储器nvm11至nvm1n。

[0114]

存储器件300和存储控制器400可以执行数据包类型通信并且可以支持使用dbi信号的dbi接口。在实施例中,存储器件300和存储控制器400可以发送和接收包括报头、数据区域和报尾的数据包。稍后将参考图14和图15给出其详细描述。在一个实施例中,存储器件300和存储控制器400可以发送和接收包括报头和数据区域的数据包。稍后将参考图16给出其详细描述。

[0115]

第一存储芯片310至第四存储芯片340均可以包括i/f电路i/f、数据路径块dpb和命令路径块cpb。i/f电路i/f对来自经由信道ch从存储控制器400接收的多个数据信号和dbi信号的具有逻辑值1的位的第一数量和具有逻辑值0的位的第二数量进行计数,并且基于计数的第一数量和计数的第二数量确定数据信号是对应于报头、报尾还是数据区域。此外,i/f电路i/f可以根据对应于报头的多个数据信号确定对应于数据区域的多个数据信号是包括命令、地址还是数据。此外,i/f电路i/f可以根据对应于报头的多个数据信号确定选择的存储芯片。

[0116]

根据实施例,存储控制器400可以以相同的速率将对应于命令的数据包、对应于地址的数据包和对应于数据的数据包发送到存储器件300。此外,存储控制器400可以将命令和数据划分为时分信号并且将它们连续地发送到存储器件300。在这时,通过使用路交织方案,可以通过使一个存储芯片的命令开销与另一存储芯片的数据发送时间交叠来降低命令开销。

[0117]

根据本实施例,用于区分数据区域的信息被包括在数据包的报头中,并且命令、地

址或数据可以被包括在数据包的数据区域中。因此,由于存储器件300可以通过解码报头确定后续数据区域是包括命令、地址还是数据,所以存储器件300不需要从存储控制器400接收命令锁存使能信号cle、地址锁存使能信号ale或写入使能信号nwe。因此,存储器件300不需要包括用于接收命令锁存使能信号cle、地址锁存使能信号ale和写入使能信号nwe的引脚。相应地,由存储器件300占用的面积可以降低。此外,由于由命令锁存使能信号cle导致的开销或由地址锁存使能信号ale导致的开销可以降低,所以tcmd可以降低,因而i/o效率可以改善。

[0118]

图14为示出根据发明构思的实施例的数据包类型通信的示例的图。

[0119]

一起参考图13和图14,存储控制器400可以经由信道ch将包括第一数据包141至第六数据包146的多个数据包依次发送到存储器件300。第一数据包141至第六数据包146均可以包括报头、数据区域和报尾。例如,第一数据包141、第二数据包142、第三数据包143和第五数据包145可以被发送到第一存储芯片nvm1 310,并且第四数据包144和第六数据包146可以被发送到第二存储芯片nvm2 320。在这种情况下,关于选择的存储芯片的信息可以被包括在第一数据包141至第六数据包146中的每一者的报头中。例如,第一数据包141的报头可以指示第一存储芯片nvm1 310是选择的存储芯片并且第四数据包144的报头可以指示第二存储芯片nvm2 320是选择的存储芯片。第一数据包141包括报头141a、数据区域141b和报尾141c。第二数据包142包括报头142a、数据区域142b和报尾142c。第三数据包143包括报头143a、数据区域143b和报尾143c。第四数据包144包括报头144a、数据区域144b和报尾144c。第五数据包145包括报头145a、数据区域145b和报尾145c。第六数据包146包括报头146a、数据区域146b和报尾146c。

[0120]

在第二存储芯片nvm2 320的情况下,在对应于命令cmd的第四数据包144和对应于数据data的第六数据包146之间可能发生命令开销cmd o/h。然而,根据本实施例,对应于第一存储芯片nvm1 310的数据的第五数据包145的发送时间和第二存储芯片nvm2 320的命令开销cmd o/h可以交叠。在这时,由于第五数据包145的发送时间被包括在tdma中并且第二存储芯片nvm2 320的命令开销cmd o/h被包括在tcmd中,所以tcmd和tdma可以交叠。结果,存储器件300的i/o效率可以改善。

[0121]

在实施例中,对应于数据区域的数据信号可以对应于dbi编码被应用到的数据信号,并且对应于报头和报尾的数据信号可以对应于dbi编码未被应用到的数据信号。例如,对应于报头和报尾的多个数据信号可以对应于图6和图7的第二区域62,并且对应于数据区域的多个数据信号可以对应于图6和图7的第三区域63和第四区域64。

[0122]

因此,i/f电路i/f可以对来自数据信号和dbi信号的具有逻辑值1的位的第一数量和具有逻辑值0的位的第二数量进行计数,并且基于计数的第一数量和计数的第二数量,可以确定数据信号是否对应于报头或报尾,或者数据信号是否对应于数据区域。例如,当数据信号中具有逻辑值1的位的第一数量等于或大于参考数量5时,i/f电路(i/f)可以确定数据信号对应于报头或报尾。例如,当数据信号中具有逻辑值1的位的第一数量小于参考数量5时,i/f电路(i/f)可以确定数据信号对应于数据区域。

[0123]

在实施例中,对应于数据区域的数据信号可以对应于dbi禁用数据信号,并且对应于报头和报尾的数据信号可以对应于dbi启用数据信号。例如,对应于报头和报尾的多个数据信号可以对应于图9和图10的第四区域94,并且对应于数据区域的多个数据信号可以对

应于图9和图10的第一区域91和第二区域92。

[0124]

因此,i/f电路i/f可以基于dbi信号和数据信号来确定数据信号是否对应于报头或报尾,或者数据信号是否对应于数据区域。例如,当dbi信号处于启用电平并且数据信号中具有逻辑值1的位的第一数量小于具有逻辑值0的位的第二数量时,接口电路i/f可以确定数据信号对应于报头或报尾。然而,发明构思的各实施例不限于此。根据一些实施例,当dbi信号处于启用电平并且数据信号中的具有逻辑值0的位的第二数量小于具有逻辑值1的位的第一数量时,接口电路i/f可以确定数据信号对应于报头或报尾。例如,当dbi信号处于禁用电平时,i/f电路i/f可以确定数据信号对应于数据区域。

[0125]

图15为示出根据发明构思的实施例的命令报头、数据报头和地址报头的表。

[0126]

一起参考图14和图15,报头可以划分为第一区域和第二区域。例如,报头的第一区域可以对应于数据信号dq[7:2],并且报头的第二区域可以对应于数据信号dq[1:0]。在实施例中,第一区域的大小大于第二区域的大小。对应于第一区域的数据信号dq[7:2]可以是指示后续数据区域中包括的信息的数据区域确定区域。对应于第二区域的数据信号dq[1:0]可以是指示多个存储芯片之中的选择的存储芯片的芯片地址区域。

[0127]

例如,对应于每一个命令报头141a和144a的第一区域的数据信号dq[7:2]可以是111111,对应于每一个数据报头143a、145a和146a的第一区域的数据信号dq[7:2]可以是101111,并且对应于地址报头142a的第一区域的数据信号dq[7:2]可以是011111。然而,发明构思的各实施例不限于此。例如,对应于第一区域的数据信号的数量和配置可以根据各实施例变化。

[0128]

对应于报头的第二区域的数据信号的数量可以根据存储器件300中连接到信道ch的存储芯片的数量被确定。在实施例中,当存储器件300包括连接到信道ch的第一存储芯片310至第四存储芯片340时,对应于报头的第二区域的数据信号可以是dq[1:0]。例如,报头的两个位可以被用于区分选择的存储芯片。在实施例中,当存储器件300包括连接到信道ch的8个存储芯片时,对应于报头的第二区域的数据信号可以是dq[2:0]。例如,报头的三个位可以被用于区分选择的存储芯片。如上所述,对应于报头的第二区域的数据信号的数量可以根据各实施例变化。

[0129]

例如,当对应于报头的第二区域的数据信号dq[1:0]为00时,选择的存储芯片可以对应于第一存储芯片310;当对应于报头的第二区域的数据信号dq[1:0]为01时,选择的存储芯片可以对应于第二存储芯片320;当对应于报头的第二区域的数据信号dq[1:0]为10时,选择的存储芯片可以对应于第三存储芯片330;并且当对应于报头的第二区域的数据信号dq[1:0]为11时,选择的存储芯片可以对应于第四存储芯片340。

[0130]

图16为示出根据发明构思的实施例的数据包类型通信的另一示例的图。

[0131]

一起参考图13和图16,存储控制器400可以经由信道ch将包括第一数据包141'至第六数据包146'的多个数据包依次发送到存储器件300。第一数据包141'至第六数据包146'均可以包括报头和数据区域。例如,第一数据包141'、第二数据包142'、第三数据包143'和第五数据包145'可以被发送到第一存储芯片nvm1 310,并且第四数据包144'和第六数据包146'可以被发送到第二存储芯片nvm2 320。由于第一数据包141'至第六数据包146'不包括报尾,所以它们不同于图14的第一数据包141至第六数据包146,并且参考图14和图5在上面给出的描述也可以应用到本实施例。

[0132]

图17为示出根据发明构思的实施例的第一存储芯片310的框图。

[0133]

参考图13和图17,第一存储芯片310包括数据信号焊盘pd11、dbi信号焊盘pd12、i/f电路311、页面缓冲器120、存储单元阵列130和控制逻辑电路140。第二存储芯片320至第四存储芯片340也可以类似地实施为第一存储芯片310。

[0134]

尽管未示出,但是第一存储芯片310可以包括类似于图2的存储器件100的第一引脚p11至第四引脚p14,并且第一引脚p11至第四引脚p14可以共同地连接到第一存储芯片310至第四存储芯片340。第一存储芯片310至第四存储芯片340均可以包括分别连接到第一引脚p11至第四引脚p14的焊盘。

[0135]

数据信号焊盘pd11可以分别连接到第一引脚p11。i/f电路311可以经由数据信号焊盘pd11从存储控制器400分别接收多个数据信号dq。i/f电路311可以经由dbi信号焊盘pd12从存储控制器400接收dbi信号dbi。

[0136]

i/f电路311可以包括解码器311a、报头解码器311b和芯片选择解码器311c。在实施例中,解码器311a可以接收多个数据信号dq和dbi信号dbi。例如,解码器311a可以类似于图4的解码器111被实施,因而解码器311a可以包括数据信号解码器和dbi解码器。参考图4在上面给出的描述可以应用到本实施例。

[0137]

在实施例中,基于数据信号dq中包括的具有逻辑值1的位的第一数量和具有逻辑值0的位的第二数量,解码器311a可以确定多个数据信号dq是对应于报头、报尾还是数据区域。例如,如图14中所示,当每一个数据包包括报头、数据区域和报尾时,当数据信号dq中包括的具有逻辑值1的位的第一数量小于或等于具有逻辑值0的位的第二数量时,解码器311a可以确定数据信号dq对应于数据区域。当数据信号dq中包括的具有逻辑值1的位的第一数量大于具有逻辑值0的位的第二数量时,解码器311a可以确定数据信号dq对应于报头或报尾。然而,发明构思的各实施例不限于此。根据一些实施例,当数据信号dq中包括的具有逻辑值0的位的第二数量小于或等于具有逻辑值1的位的第一数量时,解码器311a可以确定数据信号dq对应于数据区域。当数据信号dq中包括的具有逻辑值0的位的第二数量大于具有逻辑值1的位的第一数量时,解码器311a可以确定数据信号dq对应于报头或报尾。例如,如图16中所示,当每一个数据包包括报头和数据区域时,当数据信号dq中包括的具有逻辑值1的位的第一数量小于或等于具有逻辑值0的位的第二数量时,解码器311a可以确定数据信号dq对应于数据区域,并且当数据信号dq中包括的具有逻辑值1的位的第一数量大于具有逻辑值0的位的第二数量时,解码器311a可以确定数据信号dq对应于报头。然而,发明构思的各实施例不限于此。根据一些实施例,当数据信号dq中包括的具有逻辑值0的位的第二数量小于或等于具有逻辑值1的位的第一数量时,解码器311a可以确定数据信号dq对应于数据区域,并且当数据信号dq中包括的具有逻辑值0的位的第二数量大于具有逻辑值1的位的第一数量时,解码器311a可以确定数据信号dq对应于报头。

[0138]

基于对应于报头的第一区域的多个数据信号(例如,图15中的dq[7:2]),报头解码器311b可以确定后续数据区域中包括的信息。基于对应于报头的第二区域的多个数据信号(例如,图15中的dq[1:0]),芯片选择解码器311c可以确定多个存储芯片之中的选择的存储芯片。例如,基于数据信号的较低的位,芯片选择解码器311c可以确定选择的存储芯片。

[0139]

例如,作为芯片选择解码器311c的确定的结果,第一存储芯片310可以是选择的存储芯片。在这种情况下,当报头解码器311b确定后续数据区域对应于数据data时,i/f电路

311可以将数据data提供到数据路径块dpb。另一方面,当报头解码器311b确定后续数据区域对应于命令cmd或地址addr时,i/f电路311可以将命令cmd或地址addr提供到控制逻辑电路140。

[0140]

例如,当芯片选择解码器311c确定第一存储芯片310不是选择的存储芯片时,i/f电路311不将后续数据区域提供到数据路径块dpb和控制逻辑电路140。例如,当芯片选择解码器311c确定第一存储芯片310不是选择的存储芯片时,i/f电路311可以禁用解码器311a和/或报头解码器311b。

[0141]

图18为根据发明构思的实施例的存储系统的操作方法的流程图。参考图11,根据本实施例的存储器件的操作方法为使用dbi编码方案的发送/接收数据包类型数据的方法,并且可以例如由图13的存储器件300或图17的第一存储芯片310执行。在下文中,将一起参考图13、图17和图18给出描述。

[0142]

在操作s210中,第一存储芯片310从存储控制器400接收数据信号dq和dbi信号dbi。在操作s220中,第一存储芯片310对来自数据信号dq和dbi信号dbi的具有逻辑值1的位的第一数量和具有逻辑值0的位的第二数量进行计数。在操作s230中,第一存储芯片310确定第一数量是否大于第二数量。当确定第一数量大于第二数量时,在操作s240中,第一存储芯片310将数据信号dq确定为报头或报尾。另一方面,当确定第一数量不大于第二数量时,在操作s250中,第一存储芯片310将数据信号dq确定为数据区域。

[0143]

然而,发明构思的实施例不限于此。根据一些实施例,当确定第二数量大于第一数量时,第一存储芯片310可以将数据信号dq确定为报头或报尾。另一方面,当确定第二数量不大于第一数量时,第一存储芯片310可以将数据信号dq确定为数据区域。

[0144]

在操作s260中,第一存储芯片310通过对报头的第一区域中包括的位进行解码来确定后续数据区域中包括的信息。在操作s270中,第一存储芯片310通过对报头的第二区域中包括的位进行解码来确定多个存储芯片之中的选择的存储芯片。在操作s280中,第一存储芯片310根据命令cmd、地址addr和数据data执行存储操作。可以对选择的存储芯片执行存储操作。

[0145]

图19为示出根据发明构思的实施例的存储系统20a的框图。

[0146]

参考图19,存储系统20a包括存储器件300a和存储控制器400。根据本实施例的存储系统20a可以对应于图13的存储系统20的改进示例。详细地,与图13的存储器件300相比,存储器件300a还包括缓冲器芯片350。缓冲器芯片350可以连接在存储控制器400和第一存储芯片310至第四存储芯片340之间,并且可以经由信道ch连接到存储控制器400。缓冲器芯片350也可以被称为频率提升接口(fbi)电路。在实施例中,第一存储芯片310至第四存储芯片340和缓冲器芯片350可以实施在单个封装中。然而,发明构思的各实施例不限于此。例如,第一存储芯片310至第四存储芯片340和缓冲器芯片350可以实施在不同封装中。

[0147]

在实施例中,存储控制器400和存储器件300a可以根据dbi编码方案发送和接收数据信号。例如,存储控制器400可以将与在图6和图7中示出的第三区域63和第四区域64对应的数据信号发送到存储器件300a。在这种情况下,缓冲器芯片350可以将从存储控制器400接收的数据信号发送到第一存储芯片310至第四存储芯片340。

[0148]

在实施例中,存储控制器400和存储器件300a可以经由dbi接口发送和接收数据包类型数据。在实施例中,通过确定来自数据信号的具有逻辑值1的位的第一数量和具有逻辑

值0的位的第二数量,缓冲器芯片350确定从存储控制器400接收的多个数据信号是对应于报头、报尾还是数据区域。例如,缓冲器芯片350可以包括与图17的解码器311a相同的配置。此外,缓冲器芯片350可以通过对对应于报头的多个数据信号进行解码来确定第一存储芯片310至第四存储芯片340之中的选择的存储芯片,并且将多个数据信号发送到选择的存储芯片。例如,缓冲器芯片350可以包括与图17的芯片选择解码器311c相同的配置。

[0149]

在实施例中,存储控制器400可以为存储器件300a生成多个数据信号(在下文中被称为“控制器信号”),并且缓冲器芯片350可以为第一存储芯片310至第四存储芯片340生成多个信号(在下文中被称为“缓冲器芯片信号”)。例如,缓冲器芯片信号可以对应于指示第一存储芯片310至第四存储芯片340的训练操作的训练命令。

[0150]

例如,控制器信号可以对应于根据dbi编码方案编码的信号(例如,图6和图7的第三区域63和第四区域64),并且缓冲器芯片信号可以对应于不根据dbi编码方案编码的信号(例如,图6和图7的第二区域62)。通过对数据信号和dbi信号进行解码,第一存储芯片310至第四存储芯片340可以确定接收的数据信号是控制器信号还是缓冲器芯片信号。

[0151]

图20为用于描述根据发明构思的实施例的可以应用到存储器件的接合垂直nand(b-vnand)结构的图。当存储器件中包括的非易失性存储器被实施为b-vnand类型闪存时,非易失性存储器可以具有在图20中示出的结构。

[0152]

参考图20,存储器件500的单元区域cell可以对应于第一半导体层l1,并且外围电路区域peri可以对应于第二半导体层l2。存储器件500的外围电路区域peri和单元区域cell均可以包括外部焊盘接合区域pa、字线接合区域wlba和位线接合区域blba。

[0153]

外围电路区域peri可以包括:第一衬底610,层间绝缘层615,形成在第一衬底610上的多个电路元件620a、620b和620c,分别连接到多个电路元件620a、620b和620c的第一金属层630a、630b和630c,以及形成在第一金属层630a、630b和630c上的第二金属层640a、640b和640c。在示例实施例中,第一金属层630a、630b和630c可以由具有较高电阻率的钨形成,并且第二金属层640a、640b和640c可以由具有较低电阻率的铜形成。

[0154]

在示例实施例中,尽管仅仅第一金属层630a、630b和630c以及第二金属层640a、640b和640c被示出和描述,但是示例实施例不限于此,并且一个或更多个附加金属层还可以形成在第二金属层640a、640b和640c上。形成在第二金属层640a、640b和640c上的一个或更多个附加金属层的至少部分可以由电阻率低于形成第二金属层640a、640b和640c的铜的电阻率的铝等形成。

[0155]

层间绝缘层615可以布置在第一衬底610上并且覆盖多个电路元件620a、620b和620c,第一金属层630a、630b和630c以及第二金属层640a、640b和640c。层间绝缘层615可以包括诸如氧化硅、氮化硅等的绝缘材料。

[0156]

下接合金属671b和672b可以在字线接合区域wlba中形成在第二金属层640b上。在字线接合区域wlba中,外围电路区域peri中的下接合金属671b和672b可以电接合到单元区域cell的上接合金属571b和572b。下接合金属671b和672b以及上接合金属571b和572b可以由铝、铜、钨等形成。另外,单元区域cell中的上接合金属571b和572b可以被称为第一金属焊盘并且外围电路区域peri中的下接合金属671b和672b可以被称为第二金属焊盘。

[0157]

单元区域cell可以包括至少一个存储块。单元区域cell可以包括第二衬底510和公共源极线520。在第二衬底510上,多条字线531至538(即,530)可以在垂直于第二衬底510

输出接触插塞503连接到布置在外围电路区域peri中的多个电路元件620a、620b和620c中的至少一个。例如,第二输入-输出焊盘505可以通过第二输入-输出接触插塞503经由金属图案672a电连接到电路元件620a。

[0165]

根据各实施例,第二衬底510和公共源极线520可以不布置在布置有第二输入-输出接触插塞503的区域中。此外,第二输入-输出焊盘505在第三方向(第三方向d3)上可以不与字线530交叠。第二输入-输出接触插塞503可以在平行于第二衬底510的上表面的方向上与第二衬底510分开,并且可以穿过单元区域cell的层间绝缘层连接到第二输入-输出焊盘505。

[0166]

根据各实施例,可以选择性地形成第一输入-输出焊盘605和第二输入-输出焊盘505。例如,存储器件400可以仅仅包括布置在第一衬底610上的第一输入-输出焊盘605或者布置在第二衬底510上的第二输入-输出焊盘505。可选择地,存储器件400可以包括第一输入-输出焊盘605和第二输入-输出焊盘505二者。

[0167]

在单元区域cell和外围电路区域peri中的每一者中包括的外部焊盘接合区域pa和位线接合区域blba中的每个区域中,设置在最上金属层上的金属图案可以设置为虚设图案,或者最上金属层可以不存在。

[0168]

在外部焊盘接合区域pa中,存储器件500可以包括位于外围电路区域peri的最上金属层中的下金属图案673a,下金属图案673a对应于形成在单元区域cell的最上金属层中的上金属图案572a,并且下金属图案673a与单元区域cell的上金属图案572a具有相同的截面形状从而彼此连接。在外围电路区域peri中,形成在外围电路区域peri的最上金属层中的下金属图案673a可以不连接到接触。上金属图案572a可以通过接触571a连接到第二金属层560a。类似地,在外部焊盘接合区域pa中,上金属图案可以形成在单元区域cell的最上金属层中,该上金属图案对应于形成在外围电路区域peri的最上金属层中的下金属图案,并且该上金属图案与外围电路区域peri的下金属图案具有相同的形状。

[0169]

下接合金属671b和672b可以形成在字线接合区域wlba中的第二金属层640b上。在字线接合区域wlba中,外围电路区域peri的下接合金属671b和672b可以通过cu-cu接合电连接到单元区域cell的上接合金属571b和572b。

[0170]

另外,在位线接合区域blba中,上金属图案592可以形成在单元区域cell的最上金属层中,上金属图案592对应于形成在外围电路区域peri的最上金属层中的下金属图案652,并且上金属图案592与下金属图案652具有相同的截面形状。在形成在单元区域cell的最上金属层中的上金属图案592上可以不形成接触。

[0171]

在示例实施例中,图4的存储单元阵列130可以布置在单元区域cell中,并且图4的i/f电路110、页面缓冲器120、控制逻辑电路140、电压生成器150和/或行译码器160可以布置在外围电路区域peri中。例如,参考图2、图4、图5和图8描述的i/f电路110、110a和110b以及控制逻辑电路140可以布置在外围电路区域peri中。例如,参考图13和图19描述的i/f电路i/f和命令路径块cpb可以布置在外围电路区域peri中。例如,参考图17描述的i/f电路311、页面缓冲器120和控制逻辑电路140可以布置在外围电路区域peri中。

[0172]

尽管已经参考发明构思的实施例具体示出和描述了发明构思,但是将理解的是,可以在发明构思的实施例中进行形式和细节中的各种改变而不背离所附权利要求的精神和范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1