存储器芯片及存储器装置的制作方法

1.本揭示内容是关于一种存储器芯片及存储器装置。

背景技术:

2.一般而言,在包括存储器芯片的电子设备中,通常须设置控制器芯片以管理或控制存储器芯片,然而,由于控制器芯片与存储器芯片是分别独立设置,从而会增加制造电子设备的成本,例如封装成本,此外,由于电子设备包含多个芯片,亦不利于小型化存储器装置。然而,近年来,电子设备的发展趋势是往高集成、小型化及高速化的方向发展。

3.鉴于上述,需要提供一种新的存储器芯片以克服上述问题。

技术实现要素:

4.本揭示内容提供一种存储器芯片,其包括存储器单元电路(memory cell circuit)、周边电路(periphery circuit)、互连结构(interconnect structure)及控制逻辑电路(control logic circuit)。周边电路位于存储器单元电路之下,电性连接存储器单元电路。互连结构位于存储器单元电路的侧面。控制逻辑电路位于互连结构之下,控制逻辑电路电性连接互连结构及周边电路,且包括动态随机存取存储器(dynamic random

‑

access memory,dram)。

5.在一些实施方式中,动态随机存取存储器包括电容器数组,电容器数组包括多个电容器,各电容器包括导电柱、绝缘层及导电接点,绝缘层覆盖导电柱的侧面及下表面,导电接点位于绝缘层之下。

6.在一些实施方式中,控制逻辑电路包括精简指令集核心(reduced instruction set computer core,risc core)及存储器控制器(memory controller),精简指令集核心连接存储器控制器及动态随机存取存储器,存储器控制器电性连接周边电路。

7.在一些实施方式中,控制逻辑电路还包括只读存储器(read

‑

only memory,rom),只读存储器连接精简指令集核心。

8.在一些实施方式中,控制逻辑电路还包括修正错误电路(error correction circuit,ecc),修正错误电路连接存储器控制器。

9.在一些实施方式中,控制逻辑电路还包括接口电路(interface circuit)及电源管理电路(power management circuit),接口电路连接电源管理电路及精简指令集核心,且连接互连结构。

10.在一些实施方式中,周边电路包括逻辑控制器(logic control)、暂存器(register)、解码器(decoder)及输入及输出控制器(i/o control),暂存器连接逻辑控制器与i/o控制器,解码器连接逻辑控制器与i/o控制器。

11.在一些实施方式中,存储器芯片,还包括电源管理电路,逻辑控制器连接至电源管理电路。

12.在一些实施方式中,存储器单元电路为非挥发性存储器(non

‑

volatile memory,

nvm)单元电路。

13.本揭示内容提供一种存储器装置,包括至少二个前述任一实施方式所述的存储器芯片及至少一接合线。这些存储器芯片堆叠设置。至少一接合线将这些存储器芯片中的这些互连结构相互电性连接。

14.应该理解的是,前述的一般性描述和下列具体说明仅仅是示例性和解释性的,并旨在提供所要求的本揭示内容的进一步说明。

附图说明

15.本揭示内容上述和其他态样、特征及其他优点参照说明书内容并配合附加图式得到更清楚的了解,其中:

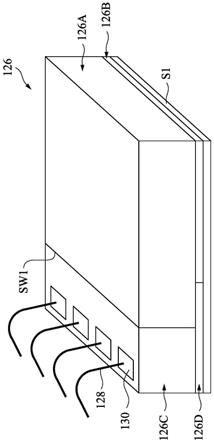

16.图1是根据本揭示内容各种实施方式的电子设备的示意图。

17.图2是根据本揭示内容各种实施方式的存储器芯片的示意图。

18.图3是根据本揭示内容各种实施方式的存储器芯片的剖面示意图。

19.图4及图5是根据本揭示内容各种实施方式的电子设备内的元件示意图。

20.图6是根据本揭示内容各种实施方式的存储器芯片的示意图。

21.图7及图8是根据本揭示内容各种实施方式的电子设备的示意图。

22.图9是根据本揭示内容各种实施方式的存储器装置的示意图。

具体实施方式

23.为了使本揭示内容的叙述更加详尽与完备,可参照所附的图式及以下所述各种实施例,图式中相同的号码代表相同或相似的元件。

24.以下将以图式揭露本揭示内容的复数个实施方式,为明确说明起见,许多实务上的细节将在以下叙述中一并说明。然而,应了解到,这些实务上的细节不应用以限制本揭示内容。也就是说,在本揭示内容部分实施方式中,这些实务上的细节是非必要的。此外,为简化图式起见,一些现有惯用的结构与元件在图式中将以简单示意的方式绘示。

25.本揭示内容提供了一种包含存储器芯片的电子设备。图1是根据本揭示内容各种实施方式的电子设备的示意图。图2是根据本揭示内容各种实施方式的存储器芯片的示意图。

26.如图1所示,电子设备100包括主机(host)110及存储器装置120。主机110具有第一连接器112。存储器装置120包括电路板124、第二连接器122、存储器芯片126及接合线128。第二连接器122及存储器芯片126设置于电路板124上。存储器芯片126借由接合线128连接至第二连接器122。当第一连接器112与第二连接器122连接,主机110可读取存储器芯片126的信息或是或写入信息到存储器芯片126中。主机110包括处理器。在一些实施方式中,存储器芯片126为与非门存储器芯片(nand flash memory chip)。在一些实施方式中,存储器装置120可应用于安全数字卡(secure digital memory card,sd card)或固态硬盘(solid

‑

state drive或solid

‑

state disk,ssd)。在一些实施方式中,第一连接器112及第二连接器122为通用串行总线(universal serial bus,usb)。

27.如图2所示,存储器芯片126包括半导体基板s1、存储器单元电路(memory cell circuit)126a、周边电路(periphery circuit)126b、互连结构(interconnect strcuture)

126c及控制逻辑电路(control logic circuit)126d。周边电路126b及控制逻辑电路126d位于半导体基板s1上。换句话说,在同一半导体基板s1上制造和设计周边电路126b及控制逻辑电路126d。因此,有利于简化制作如图1的电子设备100流程,并且,由于控制逻辑电路126d整合于存储器芯片126中,设置于存储器单元电路126a之下,控制逻辑电路126d可管理或控制存储器单元电路126a,控制逻辑电路126d可接受来自主机110的指令、地址及数据,储存这些信息且传输至存储器单元电路126a。因此,如图1的电子设备100中无须设置控制器芯片(controller chip),换句话说,电子设备100不含有控制器芯片,因此,能够降低制造电子设备100的成本,并且利于小型化电子设备100的体积。节省出来的空间则可以设置更多的存储器芯片,可进一步增加存储器的储存空间。并且,相较于主机和存储器芯片间是透过控制器芯片传输的结构,由于本揭示内容的控制逻辑电路126d与周边电路126b之间的传输路径更短,电子设备100可达到更快的传输速度。

28.请继续参照图2,周边电路126b位于存储器单元电路126a之下,电性连接存储器单元电路126a。互连结构126c位于存储器单元电路126a的侧面sw1。控制逻辑电路126d位于互连结构126c之下,控制逻辑电路126d电性连接互连结构126c及周边电路126b。接合线128自互连结构126c顶部的接合垫130延伸出去。在一些实施方式中,存储器单元电路126a为非挥发性存储器(non

‑

volatile memory,nvm)单元电路,例如存储器单元电路。在一些实施方式中,存储器单元电路126a为三维nand存储器(3d nand flash memory)单元电路。本揭示内容所述的“三维nand存储器”是指在水平方向放置的基板上具有垂直方向串联的存储器单元的晶体管的半导体元件,或称为存储器串,例如nand串,使得存储器串相对于基板在垂直方向上延伸,“垂直”是指垂直于基板的水平表面。在一些实施方式中,半导体基板s1为包括硅、硅锗、碳化硅、硅覆绝缘、锗覆绝缘、玻璃、氮化镓、砷化镓以及/或其它适合的iii

‑

v族化合物。在一些实施方式中,半导体基板s1为硅基板,包括单晶硅、多晶硅或非晶硅。

29.如图2所示,控制逻辑电路126d位于互连结构126c及存储器单元电路126a之下,周边电路126b仅位于存储器单元电路126a之下,控制逻辑电路126d与周边电路126b间的接口并无对准存储器单元电路126a及互连结构126c间的接口。在另一些实施方式中,周边电路126b位于互连结构126c及存储器单元电路126a之下,控制逻辑电路126d仅位于互连结构126c之下。

30.图3是根据本揭示内容各种实施方式的存储器芯片126的剖面示意图。在一些实施方式中,控制逻辑电路126d包括动态随机存取存储器(dynamic random

‑

access memory,dram)。在一些实施方式中,动态随机存取存储器包括电容器数组,电容器数组包括多个电容器。为了简化图示,图3仅绘示出动态随机存取存储器内的其中一个电容器c。可根据设计需求,在动态随机存取存储器中设置所需数量的电容器c。电容器c包括导电柱c1、绝缘层i及导电接点c2,绝缘层i覆盖导电柱c1的侧面及下表面,导电接点c2位于绝缘层之下i。在一些实施方式中,导电柱c1的上表面实质上与绝缘层i的上表面共平面。在一些实施方式中,绝缘层i包覆导电柱c1的所有侧面。然而,本揭示内容的电容器结构不限于上述。此外,控制逻辑电路126d包括多个晶体管f1,例如金属氧化物半导体场效应晶体管(metal

‑

oxide

‑

semiconductor field

‑

effect transistor,mosfet)。举例来说,mosfet为低电压mosfet或高电压mosfet。周边电路126b包括多个晶体管f2、f3。晶体管f2、f3例如为mosfet。举例来说,晶体管f2为高电压mosfet,晶体管f3为低电压mosfet。在一些实施方式中,晶体管f1、

f2、f3的源极和汲极为n+或p+。

31.存储器单元电路126a包括多个金属层310、多个绝缘层320、半导体通道330、多个栅极绝缘层340及多个接触通孔350。多个金属层310及多个绝缘层320交替堆叠。栅极绝缘层340环绕半导体通道330。在存储器芯片126中,设置存储器单元电路126a的区域称为存储器单元。在一些实施方式中,本揭示内容的存储器单元为nand单元。在一些实施方式中,半导体通道330为硅通道。半导体通道330会进一步与源极区及汲极区相连,以控制存储器单元电路126a的操作,例如读取、写入或抹除。

32.在一些实施方式中,控制逻辑电路126d可进一步包括其他元件,例如精简指令集核心、存储器控制器、只读存储器等,这些其他元件并未绘示于图3中,将在接下来的图4内进一步描述。

33.图4是根据本揭示内容各种实施方式的电子设备400内的元件示意图。存储器芯片126包括半导体基板s1、存储器单元电路126a、周边电路126b、互连结构126c及控制逻辑电路126d。

34.控制逻辑电路126d包括动态随机存取存储器410、精简指令集核心(reduced instruction set computer core,risc core)420及存储器控制器(memory controller)422,精简指令集核心420连接存储器控制器422及动态随机存取存储器410,存储器控制器422电性连接周边电路126b。在一些实施方式中,动态随机存取存储器410包括电容器数组,电容器数组包括多个电容器,电容器的结构例如为图3的电容器c所示。在一些实施方式中,存储器控制器422为nand控制器。

35.在一些实施方式中,控制逻辑电路126d还包括只读存储器(read

‑

only memory,rom)430,只读存储器430连接精简指令集核心420。

36.在一些实施方式中,控制逻辑电路126d还包括修正错误电路(error correction circuit,ecc)432,修正错误电路432连接存储器控制器422。

37.在一些实施方式中,控制逻辑电路126d还包括接口电路(interface circuit)ic1及电源管理电路(power management circuit)440,接口电路ic1连接电源管理电路440及精简指令集核心420,且连接互连结构126c。在一些实施方式中,控制逻辑电路126d借由电源管理电路440电性连接周边电路126b。在一些实施方式中,控制逻辑电路126d借由接口电路ic1电性连接互连结构126c。在一些实施方式中,控制逻辑电路126d还包括接口电路ic2。接口电路ic2连接存储器控制器422。控制逻辑电路126d借由接口电路ic2电性连接周边电路126b。

38.在一些实施方式中,如图4所示,周边电路126b包括逻辑控制器(logic control)450、暂存器(register)460、解码器(decoder)470及i/o控制器(i/ocontrol)480,暂存器460连接逻辑控制器450与i/o控制器480,解码器470连接逻辑控制器450与i/o控制器480。在一些实施方式中,逻辑控制器450连接至电源管理电路440。

39.在一些实施方式中,周边电路126b还包括接口电路ic3,周边电路126b借由接口电路ic3电性连接控制逻辑电路126d。举例来说,周边电路126b借由接口电路ic3连接接口电路ic2以与控制逻辑电路126d电性连接。

40.在一些实施方式中,电子设备400还包括互连结构ic4,周边电路126b借由互连结构ic4电性连接存储器单元电路126a。

41.在一些实施方式中,主机110包括接口电路114。主机110借由接口电路114连接互连结构126c的接口电路ic1。

42.图5是根据本揭示内容各种实施方式的电子设备500内的元件示意图。图5和图4的差异在于在图4的电源管理电路440设置于控制逻辑电路126d中,图5的电源管理电路540设置于控制逻辑电路126d及周边电路126b之间。图4的电源管理电路440距离控制逻辑电路126d中的其他元件较近,在传输速度上比电源管理电路540来的更快。

43.图6是根据本揭示内容各种实施方式的存储器芯片626的示意图。如图6所示,控制逻辑电路626d位于互连结构126c之下,周边电路626b位于存储器单元电路126a之下,控制逻辑电路626d与周边电路626b间的接口实质上对准存储器单元电路126a及互连结构126c间的接口。图6与图2的差异之处仅在于周边电路及控制逻辑电路的配置。

44.图7是根据本揭示内容各种实施方式的电子设备700的示意图。电子设备700包括主机110及存储器装置720。主机110具有第一连接器112。存储器装置720包括电路板124、第二连接器122、第一存储器芯片726a、第二存储器芯片726b及接合线728。第一存储器芯片726a及第二存储器芯片726b的实施方式可参前述的存储器芯片126的实施方式,在此不再赘述。图7与图1的差异之处在于图1的电子设备100的第二连接器122连接至一个存储器芯片126,而图7的电子设备700的第二连接器122连接至两个存储器芯片,亦即第一存储器芯片726a及第二存储器芯片726b。然而,本揭示内容不限于此,可根据设计需求,调整连接至第二连接器122的存储器芯片数量,例如三、四、五、六等。

45.图8是根据本揭示内容各种实施方式的电子设备800的示意图。电子设备800包括主机810、电路板824、存储器芯片826及接合线828。主机810借由接合线828连接至存储器芯片826。主机810可读取存储器芯片826的信息或是或写入信息到存储器芯片826中。主机810包括处理器。

46.图9是根据本揭示内容各种实施方式的存储器装置900的示意图。存储器装置900包括至少两个存储器芯片及至少一接合线。这些存储器芯片堆叠设置。至少一接合线将这些存储器芯片中的这些互连结构相互电性连接。这些存储器芯片例如为存储器芯片910及存储器芯片920,存储器芯片910及存储器芯片920堆叠设置。至少一接合线例如为接合线930。接合线930将存储器芯片910及存储器芯片920相互电性连接。可根据设计需求,调整堆叠的存储器芯片的数量及接合线的数量。存储器芯片的数量例如为二、三、四、五或六等。

47.存储器芯片910包括包括半导体基板s2、存储器单元电路910a、周边电路910b、互连结构910c及控制逻辑电路910d。周边电路910b及控制逻辑电路910d位于半导体基板s2上。互连结构910c位于控制逻辑电路910d上。存储器单元电路910a位于周边电路910b上。存储器芯片920包括包括半导体基板s3、存储器单元电路920a、周边电路920b、互连结构920c及控制逻辑电路920d。周边电路920b及控制逻辑电路920d位于半导体基板s3上。互连结构920c位于控制逻辑电路920d上。存储器单元电路920a位于周边电路920b上。接合线930自互连结构910c顶部的接合垫940延伸出去,连接至互连结构920c顶部的接合垫950,使互连结构910c及920c相互电性连接。存储器芯片910及存储器芯片920中配置的实施方式可参照前述存储器芯片126的实施方式,在此不再赘述。

48.请同时参照图8及图9,在一些实施方式中,电子设备800中的存储器芯片826可置换为存储器装置900。存储器装置900的存储器芯片920借由接合线828连接至主机810。在存

储器装置900中,由于在同一半导体基板s2上制造和设计周边电路910b及控制逻辑电路910d,在同一半导体基板s3上制造和设计周边电路920b及控制逻辑电路920d,有利于简化制作电子设备800的流程。控制逻辑电路910d整合于存储器芯片910中,可管理或控制存储器单元电路910a。控制逻辑电路910d可接受来自主机810的指令、地址及数据,储存这些信息且传输至存储器单元电路910a。控制逻辑电路920d整合于存储器芯片920中,可管理或控制存储器单元电路920a。控制逻辑电路920d可接受来自主机810的指令、地址及数据,储存这些信息且传输至存储器单元电路920a。因此,电子设备800中无须设置控制器芯片,换句话说,电子设备800不含有控制器芯片,因此,能够降低制造成本,并且利于小型化电子设备800的体积。节省出来的空间则可以设置更多的存储器芯片,可进一步增加存储器的储存空间。并且,相较于主机和存储器芯片间是透过控制器芯片传输的结构,由于本揭示内容的控制逻辑电路910d与周边电路910b之间的传输路径更短,且控制逻辑电路920d与周边电路920b之间的传输路径更短,电子设备800可达到更快的传输速度。

49.综上所述,本揭示内容提供一种存储器芯片及一种存储器装置。控制逻辑电路整合于存储器芯片中,因此,存储器装置不须设置控制器芯片,从而可降低存储器装置的制造成本且提升信号传输速度,可有利于小型化存储器装置的体积,此外,由于不须设置控制器芯片,节省出来的空间则可以设置更多的存储器芯片,提升存储器装置的储存空间,因此有利于含有此存储器芯片的电子设备往高集成、小型化及高速化的方向发展。

50.尽管已经参考某些实施方式相当详细地描述了本揭示内容,但是亦可能有其他实施方式。因此,所附权利要求书的精神和范围不应限于此处包含的实施方式的描述。

51.对于所属技术领域人员来说,显而易见的是,在不脱离本揭示内容的范围或精神的情况下,可以对本揭示内容的结构进行各种修改和变化。鉴于前述内容,本揭示内容意图涵盖落入所附权利要求范围内的本揭示内容的修改和变化。

52.【符号说明】

53.100,400,500,700,800:电子设备

54.110,810:主机

55.112:第一连接器

56.114,ic1,ic2,ic3:接口电路

57.120:存储器装置

58.122:第二连接器

59.124,824:电路板

60.126,626,826,910:存储器芯片

61.126a,910a,920a:存储器单元电路

62.126b,626b,910b,920b:周边电路

63.126c,910c,920c:互连结构

64.126d,626d,910d,920d:控制逻辑电路

65.128,728,828,930:接合线

66.130,940,950:接合垫

67.310:金属层

68.320:绝缘层

69.330:半导体通道

70.340:栅极绝缘层

71.350:接触通孔

72.410:动态随机存取存储器

73.420:精简指令集核心

74.422:存储器控制器

75.430:只读存储器

76.432:修正错误电路

77.440,540:电源管理电路

78.450:逻辑控制器

79.460:暂存器

80.470:解码器

81.480:输入及输出(i/o)控制器

82.720:存储器装置

83.726a:第一存储器芯片

84.726b:第二存储器芯片

85.900:存储器装置

86.c:电容器

87.c1:导电柱

88.c2:导电接点

89.f1,f2,f3:

90.i:绝缘层

91.ic4:互连结构

92.s1,s2,s3:半导体基板

93.sw1:侧面。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1