闪存器、闪存擦写计数方法、电子设备及计算机存储介质与流程

1.本技术涉及计算机技术领域,更具体地说,涉及一种闪存器、闪存擦写计数方法、电子设备及计算机存储介质。

背景技术:

2.非易失性存储例如nand flash(闪存)用于长久地保存数据,其生命周期通常是以p/e cycle(编程和擦除周期)的次数来计算,当实际p/e cycle在超出最大值后,非易失性存储就变得不再可靠,保存在其中的数据容易被破坏。

3.在相关技术中,依赖上层应用或者文件系统来统计闪存的p/e cycle。例如,上层应用或者文件系统基于ubi(unsorted block image)管理系统对闪存块进行管理时,ubi管理系统在其管理的闪存块的主存储区中创建一个用于记录闪存的p/e cycle的字段。但是,不是所有的闪存块都是通过ubi管理系统进行管理的,导致上层应用或者文件系统无法获取这些闪存块的p/e cycle次数。

4.因此,如何实现上层应用获取任意闪存块的擦写次数是本领域技术人员需要解决的技术问题。

技术实现要素:

5.本技术的目的在于提供一种闪存器、闪存擦写计数方法、电子设备及计算机存储介质,实现了上层应用获取任意闪存块的擦写次数。

6.为实现上述目的,本技术提供了一种闪存器,包括多个闪存块,每一闪存块包括多个闪存页,每一闪存页包括主存储区和备用存储区,在所述闪存块的目标闪存页的备用存储区中定义一个擦写计数字段,用于保存闪存块的擦写次数。

7.其中,所述擦写计数字段至少包括三个字节。

8.其中,所述目标闪存页的备用存储区具体为包含坏块信息字段的闪存页的备用存储区。

9.其中,所述闪存器包括nand-flash存储器。

10.为实现上述目的,本技术提供了一种闪存擦写计数方法,用于对上述的闪存器中的目标闪存块进行擦写计数,包括:

11.通过调用闪存驱动程序完成擦写动作后,判断是否擦写成功;

12.若是,则将所述目标闪存块的擦写计数字段的数值增加一。

13.其中,还包括:

14.若擦写失败,则判定所述目标闪存块为坏块。

15.其中,所述判定所述目标闪存块为坏块之后,还包括:

16.将所述目标闪存块的坏块信息字段置零。

17.其中,还包括:

18.从所述目标闪存块的目标闪存页的备用存储区读取擦写计数字段,以获取所述目

nand flash)包括多个存储块,对于其中的一个闪存块(one block)来说,包括多个闪存页,每个闪存页(one page)包括主存储区(main area)和备用存储区(spare area)。在图1中,主存储区的大小为2kb,其中包含4个512b的子区域,备用存储区的大小为64b,其中包含4个16b的子区域。备用存储区的一个子区域包含16个字节,其中,bi(bad block information)为坏块信息字段,reserved为预留字段,lsn(logical sector number)为逻辑扇区号,ecc(ecc code for main area data)为主存储区数据的ecc代码,s_ecc(ecc code for lsn data)为lsn数据的ecc代码。

32.在本实施例中,在每个闪存块的目标闪存页的备用存储区定义一个擦写计数字段,用于保存该闪存块的擦写次数,上层应用或文件系统可以通过读取每个闪存块的擦写计数字段获取该闪存块的擦写次数。擦写计数字段不仅不会影响现有的onfi(open nand flash interface)定义,其还可以被包含在将来的onfi定义中。优选的,所述目标闪存页的备用存储区具体为包含坏块信息字段的闪存页的备用存储区,擦写计数字段至少包括三个字节,例如,在图1中,可以将第14、15和16字节的预留字段设置为擦除次数字段(ec,erase counter)。

33.在本技术实施例中,基于基本的闪存块操作,在每个闪存块的目标闪存页的备用存储区中定义用于记录擦写次数的擦写计数字段,通过调用闪存驱动程序即可记录擦写次数,不依赖任何上层应用或文件系统。对于任意闪存块,上层应用或文件系统均可以通过读取擦写计数字段获取闪存块的擦写次数。

34.本技术实施例公开了一种闪存擦写计数方法,实现了上层应用获取任意闪存块的擦写次数。

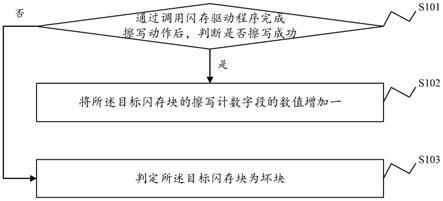

35.参见图2,根据一示例性实施例示出的一种闪存擦写计数方法的流程图,如图2所示,包括:

36.s101:通过调用闪存驱动程序完成擦写动作后,判断是否擦写成功;若是,则进入s102;若否,则进入s103;

37.s102:将所述目标闪存块的擦写计数字段的数值增加一;

38.s103:判定所述目标闪存块为坏块。

39.本实施例的目的在于记录上一实施例介绍的闪存器中目标闪存块的擦写次数。本实施例中的闪存驱动程序与现有技术中的闪存驱动程序具有不同的功能,现有技术中的闪存驱动程序只用于对闪存块进行擦写,而本实施例中的闪存驱动程序除了用于对闪存块进行擦写,还用于记录闪存块的擦写次数。在具体实施中,电子设备通过调用闪存驱动程序在每次完成擦写动作后,紧接着判断是否擦写成功;若是,则将擦写计数字段的数值增加一;若否,则判定目标闪存块为坏块,优选的,将所述目标闪存块中的坏块信息字段置零,即将图1中bi字段置零,表示该目标闪存块为坏块。

40.上层应用或文件系统获取目标闪存块的擦写次数的过程为:从所述目标闪存块的目标闪存页的备用存储区读取擦写计数字段,以获取所述目标闪存块的当前擦写次数。在具体实施中,上层应用或文件系统可以通过读取目标闪存块的目标闪存页的备用存储区中的擦写计数字段,获取该目标闪存块的当前擦写次数,进而根据该目标闪存块的当前擦写次数决定写入数据时的负载均衡算法,或者统计所有闪存块的使用强度,或者推断是否有频繁的闪存擦写动作。需要说明的是,记录闪存块擦写次数的电子设备与获取闪存块擦写

次数的电子设备可以为相同的电子设备,也可以为不同的电子设备。

41.本技术实施例提供闪存擦写计数方法,基于基本的闪存块操作,在目标闪存块的目标闪存页的备用存储区中定义用于记录擦写次数的擦写计数字段,通过调用闪存驱动程序即可记录擦写次数,不依赖任何上层应用或文件系统。对于任意闪存块,上层应用或文件系统均可以通过读取擦写计数字段获取闪存块的擦写次数。

42.基于上述程序模块的硬件实现,且为了实现本技术实施例的方法,本技术实施例还提供了一种电子设备,图3为根据一示例性实施例示出的一种电子设备的结构图,如图3所示,电子设备包括:

43.通信接口1,能够与其它设备比如网络设备等进行信息交互;

44.处理器2,与通信接口1连接,以实现与其它设备进行信息交互,用于运行计算机程序时,执行上述一个或多个技术方案提供的闪存擦写计数方法。而所述计算机程序存储在存储器3上。

45.当然,实际应用时,电子设备中的各个组件通过总线系统4耦合在一起。可理解,总线系统4用于实现这些组件之间的连接通信。总线系统4除包括数据总线之外,还包括电源总线、控制总线和状态信号总线。但是为了清楚说明起见,在图3中将各种总线都标为总线系统4。

46.本技术实施例中的存储器3用于存储各种类型的数据以支持电子设备的操作。这些数据的示例包括:用于在电子设备上操作的任何计算机程序。

47.可以理解,存储器3可以是易失性存储器或非易失性存储器,也可包括易失性和非易失性存储器两者。其中,非易失性存储器可以是只读存储器(rom,read only memory)、可编程只读存储器(prom,programmable read-only memory)、可擦除可编程只读存储器(eprom,erasable programmable read-only memory)、电可擦除可编程只读存储器(eeprom,electrically erasable programmable read-only memory)、磁性随机存取存储器(fram,ferromagnetic random access memory)、快闪存储器(flash memory)、磁表面存储器、光盘、或只读光盘(cd-rom,compact disc read-only memory);磁表面存储器可以是磁盘存储器或磁带存储器。易失性存储器可以是随机存取存储器(ram,random access memory),其用作外部高速缓存。通过示例性但不是限制性说明,许多形式的ram可用,例如静态随机存取存储器(sram,static random access memory)、同步静态随机存取存储器(ssram,synchronous static random access memory)、动态随机存取存储器(dram,dynamic random access memory)、同步动态随机存取存储器(sdram,synchronous dynamic random access memory)、双倍数据速率同步动态随机存取存储器(ddrsdram,double data rate synchronous dynamic random access memory)、增强型同步动态随机存取存储器(esdram,enhanced synchronous dynamic random access memory)、同步连接动态随机存取存储器(sldram,synclink dynamic random access memory)、直接内存总线随机存取存储器(drram,direct rambus random access memory)。本技术实施例描述的存储器3旨在包括但不限于这些和任意其它适合类型的存储器。

48.上述本技术实施例揭示的方法可以应用于处理器2中,或者由处理器2实现。处理器2可能是一种集成电路芯片,具有信号的处理能力。在实现过程中,上述方法的各步骤可以通过处理器2中的硬件的集成逻辑电路或者软件形式的指令完成。上述的处理器2可以是

通用处理器、dsp,或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件等。处理器2可以实现或者执行本技术实施例中的公开的各方法、步骤及逻辑框图。通用处理器可以是微处理器或者任何常规的处理器等。结合本技术实施例所公开的方法的步骤,可以直接体现为硬件译码处理器执行完成,或者用译码处理器中的硬件及软件模块组合执行完成。软件模块可以位于存储介质中,该存储介质位于存储器3,处理器2读取存储器3中的程序,结合其硬件完成前述方法的步骤。

49.处理器2执行所述程序时实现本技术实施例的各个方法中的相应流程,为了简洁,在此不再赘述。

50.在示例性实施例中,本技术实施例还提供了一种存储介质,即计算机存储介质,具体为计算机可读存储介质,例如包括存储计算机程序的存储器3,上述计算机程序可由处理器2执行,以完成前述方法所述步骤。计算机可读存储介质可以是fram、rom、prom、eprom、eeprom、flash memory、磁表面存储器、光盘、或cd-rom等存储器。

51.本领域普通技术人员可以理解:实现上述方法实施例的全部或部分步骤可以通过程序指令相关的硬件来完成,前述的程序可以存储于一计算机可读取存储介质中,该程序在执行时,执行包括上述方法实施例的步骤;而前述的存储介质包括:移动存储设备、rom、ram、磁碟或者光盘等各种可以存储程序代码的介质。

52.或者,本技术上述集成的单元如果以软件功能模块的形式实现并作为独立的产品销售或使用时,也可以存储在一个计算机可读取存储介质中。基于这样的理解,本技术实施例的技术方案本质上或者说对现有技术做出贡献的部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质中,包括若干指令用以使得一台电子设备(可以是个人计算机、服务器、或者网络设备等)执行本技术各个实施例所述方法的全部或部分。而前述的存储介质包括:移动存储设备、rom、ram、磁碟或者光盘等各种可以存储程序代码的介质。

53.以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1