感测放大电路以及数据读出方法与流程

本申请涉及集成电路,特别是涉及一种感测放大电路数据读出方法。

背景技术:

1、在对存储器件的存储单元进行读取操作时,通常通过感测放大器读出并放大位线与互补位线之间的电压差。感测放大器通常通过两个n型晶体管与两个p型晶体管构成锁存放大电路结构,从而对其两端连接的位线与补偿位线上的信号进行放大。但是,当前工艺条件下形成的n型晶体管和p型晶体管的导通能力通常存在差异,从而可能会导致读取失败。

2、相关技术中,有在打开字线而读取存储单元内的数据之前对各个晶体管进行偏移消除的方式,从而防止读取错误。然而,目前的偏移消除方式通常会产生较大能耗。

技术实现思路

1、基于此,本申请实施例提供一种感测放大电路,以降低存储器件的能耗。

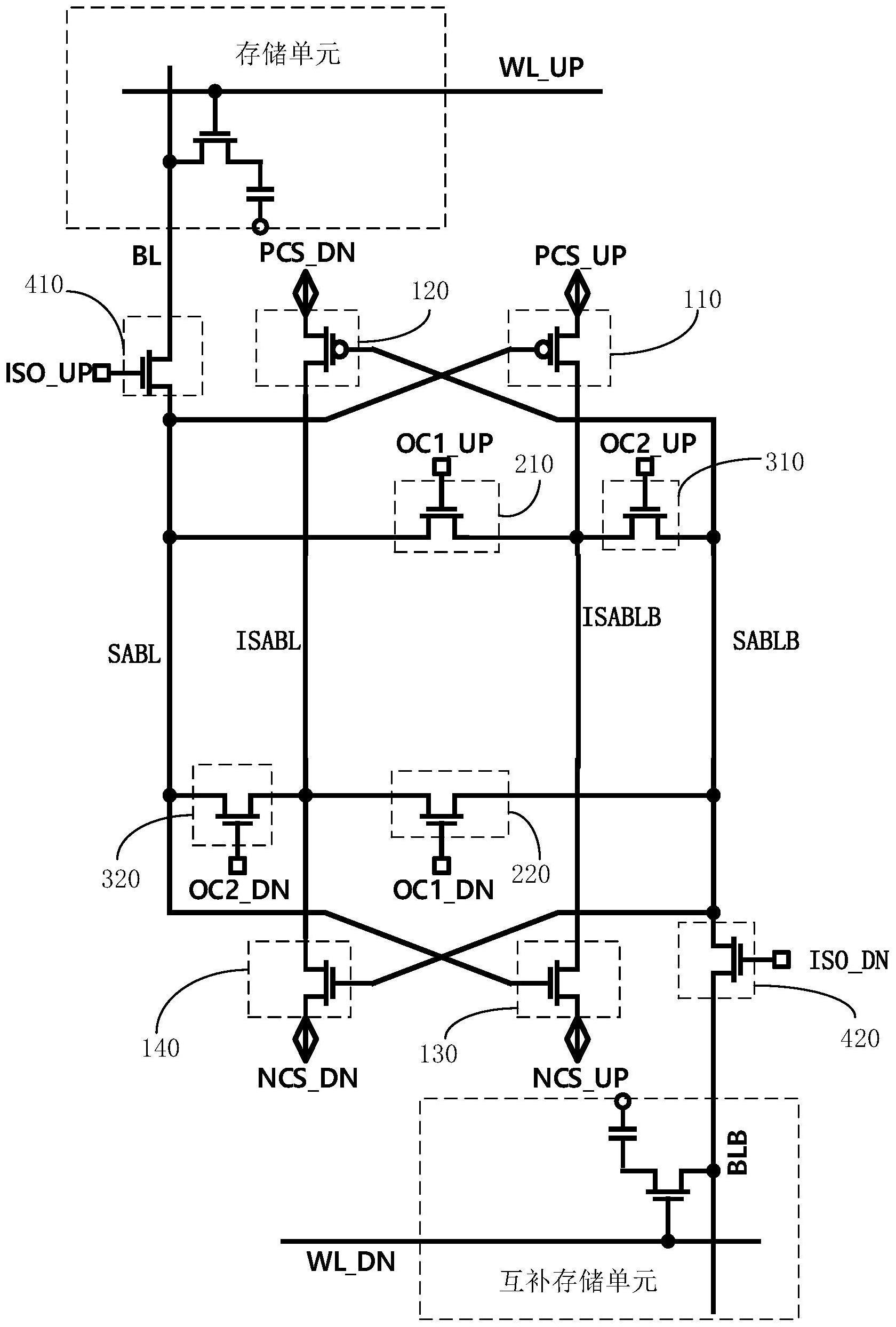

2、一种感测放大电路,包括:

3、第一p型晶体管,其连接在第一信号端和第二互补读出位线之间,并且具有连接到第一读出位线的控制端子,所述第一读出位线与位线连接;

4、第二p型晶体管,其连接在第二信号端和第二读出位线之间,并且具有连接到第一互补读出位线的控制端子,所述第一互补读出位线与互补位线连接;

5、第一n型晶体管,其连接在第三信号端和所述第二互补读出位线之间,并且具有连接到所述第一读出位线的控制端子;

6、第二n型晶体管,其连接在第四信号端和所述第二读出位线之间,并且具有连接到所述第一互补读出位线的控制端子;

7、第一偏移消除单元,其被构造为响应于第一偏移消除信号将所述第一读出位线连接到所述第二互补读出位线;

8、第二偏移消除单元,其被构造为响应于第二偏移消除信号将所述第一互补读出位线连接到所述第二读出位线;

9、第一回写单元,其被构造为响应于第一回写信号将所述第一互补读出位线连接到所述第二互补读出位线。

10、一种数据读出方法,应用于上述的感测放大电路,包括:

11、预充阶段,对位线、第一读出位线、互补位线、第一互补读出位线进行预充;

12、偏移消除阶段,为第一信号端与第三信号端分别提供高电平信号与低电平信号,同时打开第一偏移消除单元,从而将所述第一读出位线连接到所述第二互补读出位线;

13、电荷共享阶段,关断第一偏移消除单元,打开存储单元,且打开第一回写单元,从而将第一互补读出位线连接到所述第二互补读出位线;

14、放大阶段,为所述第一信号端和第二信号端提供高电平信号,为所述第三信号端和第四信号端低电平信号,同时打开第二回写单元,从而将第一读出位线连接到所述第二读出位线。

15、上述感测放大电路以及数据读出方法,第二p型晶体管连接的第三信号端独立于第一p型晶体管连接的第一信号端,第二n型晶体管连接的第四信号端独立于第一n型晶体管连接的第二信号端,且第一偏移消除单元与第二偏移消除单元分别响应于不同的偏移消除信号。因此,在偏移消除阶段,可以只对第一p型晶体管与第一n型晶体管或第二p型晶体管与第二n型晶体管进行偏移消除,从而既可以有效地消除p型晶体管与n型晶体管导通能力不同造成的偏移噪声,又可以有效降低偏移消除功耗。

技术特征:

1.一种感测放大电路,其特征在于,包括:

2.根据权利要求1所述的感测放大电路,其特征在于,所述感测放大电路还包括:

3.根据权利要求2所述的感测放大电路,其特征在于,所述感测放大电路的布局中,所述第一p型晶体管和所述第一n型晶体管位于第一器件区,所述第二p型晶体管和所述第二n型晶体管位于第二器件区;其中

4.根据权利要求3所述的感测放大电路,其特征在于,所述感测放大电路的布局中,所述第一隔离单元位于第三器件区,所述第二隔离单元位于第四器件区:其中

5.根据权利要求4所述的感测放大电路,其特征在于,

6.根据权利要求4所述的感测放大电路,其特征在于,

7.根据权利要求4所述的感测放大电路,其特征在于,所述感测放大电路的布局中,所述第二偏移消除单元、所述第一偏移消除单元、所述第一回写单元和所述第二回写单元位于第五器件区:其中

8.根据权利要求2-7任一项所述的感测放大电路,其特征在于,所述第一隔离单元包括至少一个第一隔离晶体管,所述第二隔离单元包括至少一个第二隔离晶体管。

9.根据权利要求2至4任一项所述的感测放大电路,其特征在于,所述感测放大电路还包括:

10.根据权利要求9所述的感测放大电路,其特征在于,所述第一预充单元包括至少一个第一预充晶体管,所述第二预充单元包括至少一个第二预充晶体管,所述平衡单元包括至少一个平衡晶体管。

11.根据权利要求10所述的感测放大电路,其特征在于,所述第一预充晶体管的栅极、所述第二预充晶体管的栅极以及所述平衡晶体管的栅极连接至同一控制端。

12.根据权利要求2至4任一项所述的感测放大电路,其特征在于,所述感测放大电路还包括:

13.根据权利要求12所述的感测放大电路,其特征在于,所述第三预充单元包括至少一个第三预充晶体管,所述平衡单元包括至少一个平衡晶体管。

14.根据权利要求13所述的感测放大电路,其特征在于,所述第三预充晶体管的栅极与所述平衡晶体管的栅极连接至同一控制端。

15.根据权利要求1所述的感测放大电路,其特征在于,所述第一偏移消除单元包括至少一个第一偏移消除晶体管,所述第二偏移消除单元包括至少一个第二偏移消除晶体管,所述第一回写单元包括至少一个第一回写晶体管,所述第二回写单元包括至少一个第二回写晶体管。

16.一种数据读出方法,其特征在于,应用于权利要求1-15任一项所述的感测放大电路,包括:

技术总结

本发明涉及一种感测放大电路及数据读出方法。其中,感测放大电路,包括:第一P型晶体管,其连接在第一信号端;第二P型晶体管,其连接在第二信号端;第一N型晶体管,其连接在第三信号端;第二N型晶体管,其连接在第四信号端;第一偏移消除单元,其被构造为响应于第一偏移消除信号将第一读出位线连接到第二互补读出位线;第二偏移消除单元,其被构造为响应于第二偏移消除信号将第一互补读出位线连接到第二读出位线;第一回写单元,其被构造为响应于第一回写信号将第一互补读出位线连接到第二互补读出位线;第二回写单元,其被构造为响应于第二回写信号将第一读出位线连接到第二读出位线。本申请可以有效降低偏移消除而产生的能耗。

技术研发人员:杨桂芬,池性洙

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!