写入辅助电路的制作方法

1.本发明涉及一种半导体集成电路,特别涉及一种写入辅助电路。

背景技术:

2.静态随机存储器(sram)的存储单元包括一对互锁的cmos反相器以及对于的选择管,通常采用的6t型sram存储单元中,包括了6个mos晶体管,其中,各cmos反相器都包括一个由pmos组成的上拉管(pu)以及一个由nmos组成的下拉管(pd);两个选择管则采用nmos组成,通常采用pg表示选择管。如图1所示,是现有6t型sram存储单元101的电路图;其中由pu1和pd1组成一个cmos反相器,由pu2和pd2组成另一个cmos反相器,两个存储节点分别为q和qb,节点q和qb的信号互为反相。节点q和qb分别通过选择管pg1和pg2连接到一对位线bl和blb,选择管pg1和pg2的栅极都连接到字线wl。

3.如图2所示,是现有采用了写入辅助电路的sram的电路图;在sram的存储阵列102中,各存储单元101排列成行和列的结构,同一行的各存储单元101的选择管pg1和pg2的栅极都连接到字线wl,故同一行的各存储单元101的两个存储节点q和qb分别连接到一对位线bl和blb。图2中显示了m行,各行字线则分别对应于wl[0]至wl[m];显示了n列,各列位线bl和blb分别对应于bl[0]至bl[n]和blb[0]至blb[n]。

[0004]

在对各存储单元101进行写入过程中,会在一对位线bl和blb上加入所需要写入的一对互为反相的数据,之后,字线wl选择对应的行,之后,位线上的数据会写入到行和列对应的存储单元101中。

[0005]

由图2所示可知,数据信号din输入到写操作控制模块104之后,写操作控制模块104通过两条路径形成一对互为反相的信号,也即在反相器105a和105b的输出端会形成一对互为反相的信号。

[0006]

写操作控制模块104输出的互为反相的信号会在选择模块103的选择下输入到对应的列的位线bl和blb中。

[0007]

对于sram存储单元101,对beta ratio和上拉管的idsat即饱和漏电流的要求时有冲突的,beta ratio为下拉管和选择管之间的idsat即饱和漏电流的比值,故需要对sram存储单元101的读裕度(read margin)和写裕度(write margin)进行平衡。

[0008]

随着工艺的不断发展,器件的尺寸不断等比例缩小,会采用finfet来形成sram,finfet能进一步提升sram存储单元101的密度,这会使写裕度变差。这时,finfet sram中需要采用写入辅助电路(write assist circuit),以使存储单元容易写入。

[0009]

如图2所示,是现有采用了写入辅助电路的sram的电路图;sram中还包括了写入辅助电路201,写入辅助电路201的输入端连接位线控制信号rbl,输出端输出第一负电压nvss。

[0010]

第一负电压nvss会加入接入到反相器105a和105b的接地端。本领域技术人员应当明白,反相器具有上拉管和下拉管,根据输入信号,输出信号要么通过上拉管连接到正电压,要么通过下拉管接地。图2中,第一负电压nvss会接到反相器105a和105b的接地端后,如

果反相器105a和105b的下拉管导通,则反相器105a和105b的输出端将会直接下拉到第一负电压nvss,而不是下拉到地,这样就能为位线bl和blb中的一根提供位线负电压,另一根则依然为位线正电压,这样就能是位线bl和blb的电压差增加,从而能增加写裕度,降低写难度。

[0011]

如图3a所示,是现有第一种写入辅助电路301的电路图;现有第一种写入辅助电路301中包括了延迟路径302以及多个反相器303组成的延迟路径;其中,延迟路径302能包括逻辑电路和反相器,输入端连接位线控制信号rbl,还能连接数字控制信号tsel[1:0],控制信号tsel[1:0]能调节延迟路径302的延迟时间。在反相器303的路径中,从节点en_nbl处取出一个信号连接到nmos管n301。

[0012]

电容c301的第一端连接最后一个反相器303的输出端,电容c301的第二端和nmos管n301的漏极相连且输出第一负电压nvss。nmos管n301的源极接地。

[0013]

当位线控制信号rbl为高电平时,nmos管n301导通,电容c301的第二端接地,电容c301的第一端充电到正电压;当位线控制信号rbl为低电平时,nmos管n301截止,电容c301的第二端不接地,电容c301的第一端接地,这会使得电容c301的第二端的输出第一负电压nvss。

[0014]

现有第一种写入辅助电路301的缺点是第一负电压nvss的值容易拉的比较大,从而产生电应力。在高温操作使用寿命测试(htol)过程中,写辅助电路将产生极高的电压(x1.8vdd),会使可靠性测试结果恶化。一旦没有额外的可靠性设计(dfr)插入,产品良率和可靠性之间很难平衡。

[0015]

如图3b所示,是现有第二种写入辅助电路401的电路图;现有第二种写入辅助电路401中包括了多个反相器402组成的延迟路径;在反相器402的路径中,从节点en_nbl处取出一个信号连接到nmos管n401。

[0016]

节点enb_nbl的信号经过一个反相器402的反相后再经过一个nmos的反相后得到节点nbl_fire的信号。

[0017]

节点nbl_fire和工作电压之间还连接由一个pmos,pmos的栅极连接时钟信号clkw。

[0018]

电容c401的第一端连节点nbl_fire,第二端连接nmos管n401的漏极并输出第一负电压nvss。

[0019]

节点nbl_fire和地之间连接有耦合电压抑制模块(coupling voltage suppressing block)403,耦合电压抑制模块403包括多个二极管连接的nmos,最顶部的一个nmos的栅极连接时钟信号clkw。耦合电压抑制模块403能使第一负电压nvss的最大值即绝对值的最大值得到抑制,实现电压钳位的效果,这样能避免图3a所示的现有第一种写入辅助电路301所产生的第一负电压nvss下拉过大的技术问题。

[0020]

但是图3b所示现有第二种写入辅助电路401的耦合电压抑制模块403会带来漏电路径,从而不利于降低能源效率。

技术实现要素:

[0021]

本发明所要解决的技术问题是提供一种写入辅助电路,能提供负电压并能防止负电压过低从而防止出现极端电应力,同时还能避免采用钳位电路从而能避免由钳位电路产

生的漏电路径,从而能提高能源效率。

[0022]

为解决上述技术问题,本发明提供的写入辅助电路包括:

[0023]

延迟电路,输入端连接位线控制信号;所述延迟电路具有第一输出端和第二输出端,所述第一输出端输出第一延迟信号,所述第二输出端输出第二延迟信号。

[0024]

负压产生模块,所述第二延迟信号用于为所述负压产生模块提供正输入电压,所述第一延迟信号为所述负压产生模块提供控制信号。

[0025]

在所述第一延迟信号的控制下,所述负压产生模块将所述第二延迟信号转换为写入所需要的第一负电压。

[0026]

至少所述第一延迟信号的第一延迟时间具有工作电压依赖性,且随着所述工作电压增加时,所述第一延迟时间会变小,所述第一延迟时间的减小使所述负压产生模块提前进行正负电压切换,以避免所述第一负电压过低而产生电应力。

[0027]

进一步的改进是,所述第二延迟信号的第二延迟时间也具有工作电压依赖性,且所述第二延迟时间的工作电压依赖性和所述第一延迟时间的工作电压依赖性相同。

[0028]

进一步的改进是,所述延迟电路分成第一延迟路径、第二延迟路径和第三延迟路径。

[0029]

所述第一延迟路径的输入端连接所述位线控制信号,所述第一延迟路径的输出端输出中间延迟信号。

[0030]

所述第二延迟路径的输入端连接所述中间延迟信号,所述第二延迟路径的输出端输出所述第一延迟信号。

[0031]

所述第三延迟路径的输入端连接所述第一延迟信号,所述第三延迟路径的输出端输出所述第二延迟信号。

[0032]

所述第一延迟路径具有工作电压依赖性电路结构使所述中间延迟信号的延迟时间具有工作电压依赖性,所述第一延迟时间和所述第二延迟时间的工作电压依然性都由所述中间延迟信号的延迟时间的工作电压依赖性确定。

[0033]

进一步的改进是,所述第一延迟路径由多个第一反相器连接而成。

[0034]

进一步的改进是,所述第一延迟路径的工作电压依赖性电路结构包括:

[0035]

在各所述第一反相器的电源输入端和工作电压之间设置有第一电阻,所述第一电阻为电压相关电阻,所述第一电阻使所述第一反相器的rc延迟时间随工作电压的增加而降低;

[0036]

或者,在各所述第一反相器的接地端和地之间设置有第二电阻,所述第二电阻为电压相关电阻,所述第二电阻使所述第二反相器的rc延迟时间随工作电压的增加而降低。

[0037]

进一步的改进是,所述第一电阻由第一pmos连接而成,所述第一pmos的源极连接所述工作电压,所述第一pmos的漏极连接所述第一反相器的电源输入端,所述第一pmos的栅极接地。

[0038]

进一步的改进是,所述第二电阻由第一nmos连接而成,所述第一nmos的源极接地,所述第一nmos的漏极连接所述第一反相器的接地端,所述第一nmos的栅极接所述工作电压。

[0039]

进一步的改进是,所述第一延迟路径的工作电压依赖性电路结构包括:

[0040]

分压电路,用于对所述工作电压进行分压并得到第一分压信号;

[0041]

第一逻辑电路,所述第一逻辑电路的输入端连接所述第一分压信号,所述第一逻辑电路的输出端输出选择信号;

[0042]

所述第一延迟路径上设置有多个输出端或多个短路路径;所述第一延迟路径的各输出端输出的所述中间延迟信号的延迟时间不同,所述第一延迟路径的各所述短路路径导通和断开状态下对应的输出端输出的所述中间延迟信号的延迟时间不同;

[0043]

第二选择电路,根据输出的所述选择信号选择所述第一延迟路径上的输出端或短路路径,使得所述中间延迟信号的延迟时间具有工作电压依赖性。

[0044]

进一步的改进是,所述分压电路包括多个二极管连接的mos晶体管的串联结构。

[0045]

进一步的改进是,所述分压电路中的二极管管连接的mos晶体管为第二nmos,所述第二nmos管的栅极和漏极连接。

[0046]

进一步的改进是,在所述工作电压和各所述mos晶体管的串联结构之间还连接有第二pmos,所述第二pmos的栅极连接时钟信号。

[0047]

进一步的改进是,所述第二选择电路包括由第一mos开关管组成的开关电路。

[0048]

进一步的改进是,所述第二选择电路采用多路选择器。

[0049]

进一步的改进是,所述第一负电压输出到sram的写操作控制模块;

[0050]

所述写操作控制模块的输入端连接需要写入的数据信号;

[0051]

所述写操作控制模块根据所述数据信号将所述第一负电压转换为位线所需要的位线负电压。

[0052]

进一步的改进是,所述sram的存储单元阵列中,同一列的各所述存储单元共用一对由互补的第一位线和第二位线组成的位线对;

[0053]

所述写操作控制模块还根据所述数据信号将外部正电压转换为位线所需要的位线正电压;

[0054]

在对所述存储单元进行写入时,互为反相的所述位线负电压和所述位线正电压根据所述数据信号传输到对应的所述第一位线和所述第二位线上。

[0055]

进一步的改进是,所述负压产生模块包括第二mos开关管以及第一电容;

[0056]

所述第二mos开关管的栅极连接所述第一延迟信号;

[0057]

所述第一电容的第一端连接所述第二延迟信号;

[0058]

所述第一电容的第二端输出所述第一负电压;

[0059]

所述第二mos开关管的源漏极连接在所述第一电容的第二端和地之间。

[0060]

进一步的改进是,所述第二mos开关管为nmos。

[0061]

本发明在写入辅助电路的延迟电路至少设置了使第一延迟信号的第一延迟时间具有工作电压依赖性的结构,这样,能在工作电压增加时,使第一延迟信号提前控制负压产生模块,从而负压产生模块会提前将已经积累的负电荷释放至位线,由于负压产生模块最终产生的负电压与工作电压以及释放负电荷至位线的时间有关,提前释放负电荷至位线能在保证工作电压满足要求的条件下防止第一负电压过低也即防止第一负电压的绝对值过大,从而能避免第一负电压过低而产生的电应力;所以,本发明能提供负电压并能防止负电压过低从而防止出现极端电应力,从而也能实现可靠性设计(design for reliability,dfr)目标。

[0062]

另外,本发明避免第一负电压过低是不需要采用钳位电路实现,故本发明还能同

时避免采用钳位电路从而能避免由钳位电路产生的漏电路径,从而能提高能源效率。

附图说明

[0063]

下面结合附图和具体实施方式对本发明作进一步详细的说明:

[0064]

图1是现有6t型sram存储单元的电路图;

[0065]

图2是现有采用了写入辅助电路的sram的电路图;

[0066]

图3a是现有第一种写入辅助电路的电路图;

[0067]

图3b是现有第二种写入辅助电路的电路图;

[0068]

图4是本发明实施例写入辅助电路的电路图;

[0069]

图5是图4中的各信号的波形图;

[0070]

图6是本发明实施例写入辅助电路中第一延迟路径的第一种结构的电路图;

[0071]

图7是本发明实施例写入辅助电路中第一延迟路径的第二种结构的电路图;

[0072]

图8是本发明实施例写入辅助电路中第一延迟路径的第三种结构的电路图。

具体实施方式

[0073]

如图4所示,是本发明实施例写入辅助电路501的电路图;本发明实施例写入辅助电路501包括:

[0074]

延迟电路,输入端连接位线控制信号rbl;所述延迟电路具有第一输出端和第二输出端,所述第一输出端输出第一延迟信号,所述第二输出端输出第二延迟信号。

[0075]

负压产生模块,所述第二延迟信号用于为所述负压产生模块提供正输入电压,所述第一延迟信号为所述负压产生模块提供控制信号。

[0076]

在所述第一延迟信号的控制下,所述负压产生模块将所述第二延迟信号转换为写入所需要的第一负电压nvss。

[0077]

至少所述第一延迟信号的第一延迟时间具有工作电压依赖性,且随着所述工作电压增加时,所述第一延迟时间会变小,所述第一延迟时间的减小使所述负压产生模块提前进行正负电压切换,以避免所述第一负电压nvss过低而产生电应力。

[0078]

本发明实施例中,所述第二延迟信号的第二延迟时间也具有工作电压依赖性,且所述第二延迟时间的工作电压依赖性和所述第一延迟时间的工作电压依赖性相同。

[0079]

所述延迟电路分成第一延迟路径502、第二延迟路径和第三延迟路径。

[0080]

所述第一延迟路径502的输入端连接所述位线控制信号rbl,所述第一延迟路径502的输出端输出中间延迟信号。

[0081]

所述第二延迟路径的输入端连接所述中间延迟信号,所述第二延迟路径的输出端输出所述第一延迟信号。

[0082]

所述第三延迟路径的输入端连接所述第一延迟信号,所述第三延迟路径的输出端输出所述第二延迟信号。

[0083]

所述第一延迟路径502具有工作电压依赖性电路结构使所述中间延迟信号的延迟时间具有工作电压依赖性,所述第一延迟时间和所述第二延迟时间的工作电压依然性都由所述中间延迟信号的延迟时间的工作电压依赖性确定。

[0084]

在图4对应的实施例中,所述第一延迟路径502由多个第一反相器503连接而成。

[0085]

所述第二延迟路径和所述第三延迟路径也都由多个第一反相器503连接而成。

[0086]

图4中,所述延迟电路的第一输出端对应于节点en_nbl。所述延迟电路的第二输出端对应于最后一个反相器503的输出端。

[0087]

所述负压产生模块包括第二mos开关管n501以及第一电容c501;

[0088]

所述第二mos开关管n501的栅极连接所述第一延迟信号。

[0089]

所述第一电容c501的第一端连接所述第二延迟信号。

[0090]

所述第一电容c501的第二端输出所述第一负电压nvss;

[0091]

所述第二mos开关管n501的源漏极连接在所述第一电容c501的第二端和地之间。所述第二mos开关管n501为nmos。

[0092]

在一些实施例中,所述第一延迟路径502的工作电压依赖性电路结构包括:

[0093]

在各所述第一反相器503的电源输入端和工作电压之间设置有第一电阻,所述第一电阻为电压相关电阻,所述第一电阻使所述第一反相器503的rc延迟时间随工作电压的增加而降低。

[0094]

或者,在各所述第一反相器503的接地端和地之间设置有第二电阻,所述第二电阻为电压相关电阻,所述第二电阻使所述第二反相器的rc延迟时间随工作电压的增加而降低。

[0095]

如图6所示,是本发明实施例写入辅助电路中第一延迟路径的第一种结构的电路图;第一种结构502a中,所述第一反相器单独采用标记503a标出。所述第一电阻由第一pmos504连接而成,所述第一pmos504的源极连接所述工作电压,所述第一pmos504的漏极连接所述第一反相器503的电源输入端,所述第一pmos504的栅极接地。

[0096]

所述第二电阻由第一nmos505连接而成,所述第一nmos505的源极接地,所述第一nmos505的漏极连接所述第一反相器503的接地端,所述第一nmos505的栅极接所述工作电压。

[0097]

在一些实施例中,所述第一延迟路径502的工作电压依赖性电路结构包括:

[0098]

分压电路,用于对所述工作电压进行分压并得到第一分压信号;

[0099]

第一逻辑电路,所述第一逻辑电路的输入端连接所述第一分压信号,所述第一逻辑电路的输出端输出选择信号;

[0100]

所述第一延迟路径502上设置有多个输出端或多个短路路径;所述第一延迟路径502的各输出端输出的所述中间延迟信号的延迟时间不同,所述第一延迟路径502的各所述短路路径导通和断开状态下对应的输出端输出的所述中间延迟信号的延迟时间不同;

[0101]

第二选择电路,根据输出的所述选择信号选择所述第一延迟路径502上的输出端或短路路径,使得所述中间延迟信号的延迟时间具有工作电压依赖性。

[0102]

在一些实施例中采用图7所示的本发明实施例写入辅助电路中第一延迟路径的第二种结构502b;第二种结构502b中,所述分压电路506包括多个二极管连接的mos晶体管的串联结构。较佳为,所述分压电路中的二极管管连接的mos晶体管为第二nmos,所述第二nmos管的栅极和漏极连接。在所述工作电压和各所述mos晶体管的串联结构之间还连接有第二pmos,所述第二pmos的栅极连接时钟信号。

[0103]

所述第二选择电路包括由第一mos开关管组成的开关电路508。

[0104]

图7中,不需设置所述第一逻辑电路。分压信号直接通过两个反相器组成的延迟路

径507后连接到开关电路508的第一mos开关管的栅极。开关电路508的第一mos开关导通时会使得第一延迟路径的第一反相器502b的串联路径中的部分第一反相器502b短路,从而实现所述中间延迟信号的延迟时间的调节。

[0105]

在一些实施例中采用图8所示的本发明实施例写入辅助电路中第一延迟路径的第三种结构502c;所述第三种结构502c中,所述第二选择电路采用多路选择器508a。

[0106]

所述分压电路506a和图7中的所述分压电路506相同,但单独用标记506a标出。

[0107]

图8中还设置有所述第一逻辑电路507a。

[0108]

所述第一延迟路径上的第一反相器503c连接成具有多个输出端的结构,各输出端对应于不同的延时。

[0109]

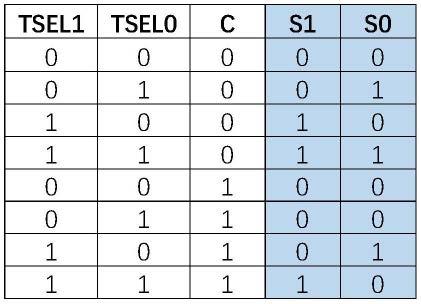

所述第一逻辑电路507a的输入信号和输出信号的逻辑关系请参考表一所示。

[0110]

表一

[0111][0112]

如图2所示,所述第一负电压nvss输出到sram的写操作控制模块104。

[0113]

所述写操作控制模块104的输入端连接需要写入的数据信号din。

[0114]

所述写操作控制模块104根据所述数据信号din将所述第一负电压nvss转换为位线bl或blb所需要的位线负电压。

[0115]

所述sram的存储单元阵列中,同一列的各所述存储单元共用一对由互补的第一位线bl和第二位线blb组成的位线对;

[0116]

所述写操作控制模块104还根据所述数据信号din将外部正电压转换为位线所需要的位线正电压;

[0117]

在对所述存储单元进行写入时,互为反相的所述位线负电压和所述位线正电压根据所述数据信号din传输到对应的所述第一位线bl和第二位线blb上。

[0118]

如图5所示,是图4中的各信号的波形图;图5中包括了3个信号线的波形,分别为位线控制信号rbl、节点en_nbl的信号和所述第一负电压nvss的波形。

[0119]

在采用图3a所示的现有第一种写入辅助电路时,位线控制信号rbl会经过t

d1

的延迟得到节点en_nbl的信号,图5中显示了位线控制信号rbl的下降沿经过t

d1

后,节点en_nbl的信号也会产生下降沿,会使所述第一负电压nvss产生较大负压值。

[0120]

但是在采用本发明实施例写入辅助电路之后,在工作电压升高时,节点en_nbl的信号和位线控制信号rbl之间的延迟会变短为t

d2

,图5中显示了位线控制信号rbl的下降沿经过t

d2

后,节点en_nbl的信号也会产生下降沿,比较t

d1

和t

d2

处的所述第一负电压nvss的值可以看出,t

d2

处对应的所述第一负电压nvss的值会变小,二者差值用δv标出。所以,本发明实施例能实现降低所述第一负电压nvss的值。

[0121]

本发明实施例在写入辅助电路501的延迟电路至少设置了使第一延迟信号的第一延迟时间具有工作电压依赖性的结构,这样,能在工作电压增加时,使第一延迟信号提前控制负压产生模块,从而负压产生模块会提前进行正负电压切换,而提前进行正负电压切换能在保证工作电压满足要求的条件下防止第一负电压nvss过低,从而能避免第一负电压nvss过低而产生的电应力;所以,本发明实施例能提供负电压并能防止负电压过低从而防止出现极端电应力,从而也能实现可靠性设计目标。

[0122]

另外,本发明实施例避免第一负电压nvss过低是不需要采用钳位电路实现,故本发明实施例还能同时避免采用钳位电路从而能避免由钳位电路产生的漏电路径,从而能提高能源效率。

[0123]

以上通过具体实施例对本发明进行了详细的说明,但这些并非构成对本发明的限制。在不脱离本发明原理的情况下,本领域的技术人员还可做出许多变形和改进,这些也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1