存储控制器及闪存芯片的制作方法

本发明涉及存储,具体涉及一种存储控制器及闪存芯片。

背景技术:

1、传统技术方案中的存储控制器通过在控制芯片中植入对应的读擦写算法即可实现对应的存储功能,这种运行模式虽然简化了基础的硬件架构,但是却需要相对繁杂或者冗长的软件程序来实现对应的读擦写算法,而且构成该读擦写算法的指令也需要较长的运行时间,这严重降低了存储芯片的工作效率。

2、需要注意的是,上述关于背景技术的介绍仅仅是为了便于清楚、完整地理解本发明的技术方案。因此,不能仅仅由于其出现在本发明的背景技术中,而认为上述所涉及到的技术方案为本领域所属技术人员所公知。

技术实现思路

1、本发明提供一种存储控制器及闪存芯片,以缓解基于芯片构建的读擦写算法导致工作效率较低的技术问题。

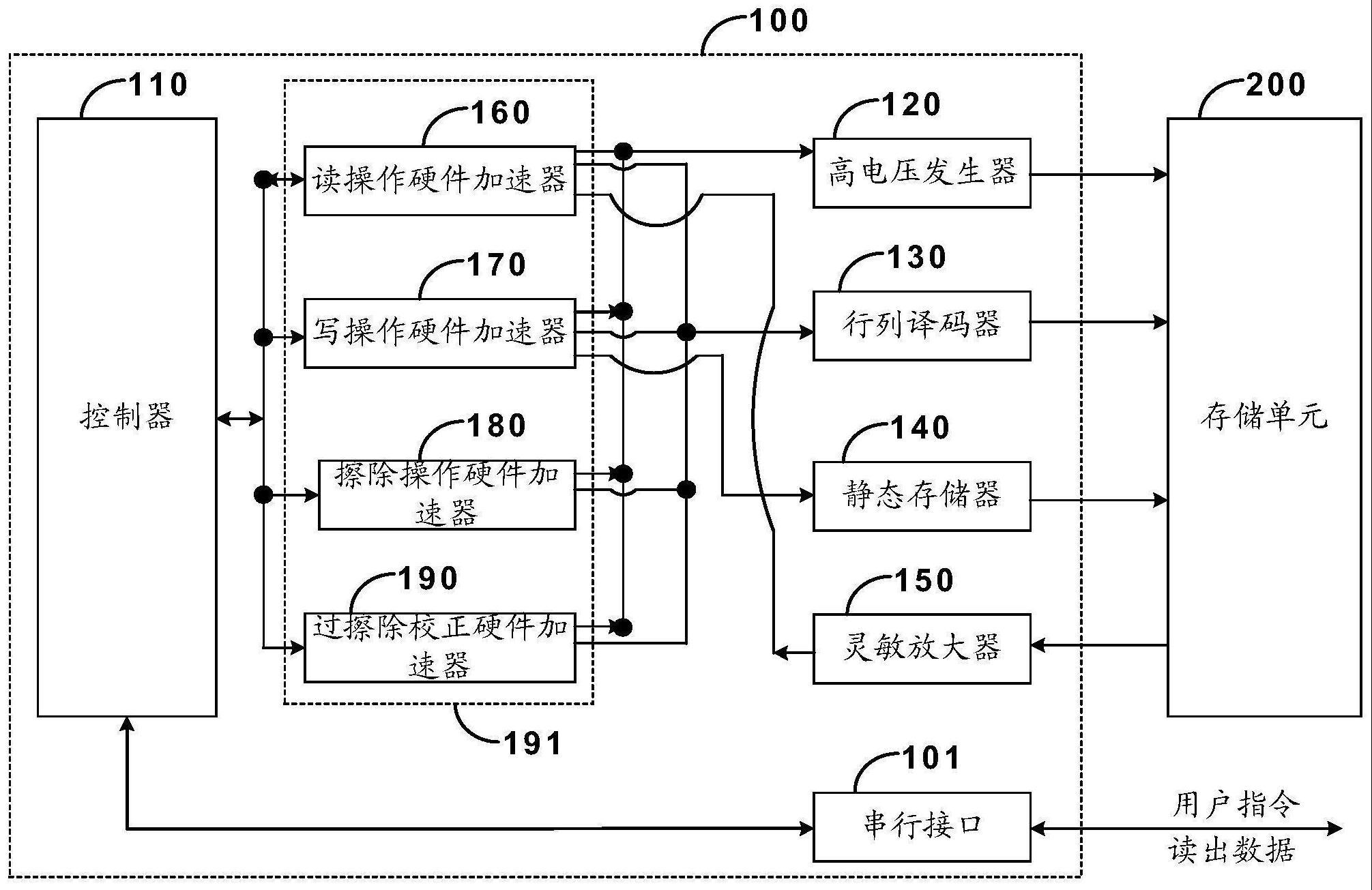

2、第一方面,本发明提供一种存储控制器,其包括加速模块和控制器,控制器与加速模块电性连接,控制器设置有主程序,用于根据用户指令操作加速模块;其中,加速模块包括读操作硬件加速器、写操作硬件加速器以及擦除操作硬件加速器中的至少一个,读操作硬件加速器与控制器电性连接,读操作硬件加速器包括读操作硬件逻辑电路,用于加速执行读操作过程;写操作硬件加速器与控制器电性连接,写操作硬件加速器包括写操作硬件逻辑电路,用于加速执行写操作过程;擦除操作硬件加速器与控制器电性连接,擦除操作硬件加速器包括擦除操作硬件逻辑电路,用于加速执行擦除操作过程。

3、在其中一些实施方式中,存储控制器还包括高电压发生器、行列译码器、静态存储器以及灵敏放大器,高电压发生器与读操作硬件加速器、写操作硬件加速器以及擦除操作硬件加速器电性连接,用于生成对应的操作电压;行列译码器与读操作硬件加速器、写操作硬件加速器以及擦除操作硬件加速器电性连接,用于生成对应的操作地址;静态存储器与写操作硬件加速器电性连接,用于存储待写入数据;灵敏放大器与读操作硬件加速器电性连接,用于读出至少一个存储单元中的数据。

4、在其中一些实施方式中,用户指令包括读操作指令;响应于读操作指令,控制器基于主程序启动读操作硬件加速器,读操作硬件加速器使能高电压发生器生成对应的读电压、使能行列译码器生成对应的读单元地址以及使能灵敏放大器读出读单元地址中存储的数据。

5、在其中一些实施方式中,读操作指令包括读命令代码和读地址代码;响应于读命令代码,读操作硬件加速器使能高电压发生器生成对应的读电压;响应于读地址代码,读操作硬件加速器使能行列译码器生成对应的读单元地址;在读电压的供给下,读操作硬件加速器使能灵敏放大器读出读单元地址中存储的数据。

6、在其中一些实施方式中,存储控制器还包括串行接口和数据转换模块,数据转换模块与灵敏放大器的输出端、串行接口电性连接,读操作硬件加速器使能数据转换模块转换灵敏放大器输出的并行数据为对应的串行数据,并通过串行接口输出串行数据至外部。

7、在其中一些实施方式中,用户指令包括写操作指令;响应于写操作指令,控制器基于主程序启动写操作硬件加速器,写操作硬件加速器使能静态存储器存储待写入数据、使能高电压发生器生成对应的写电压、使能行列译码器生成对应的写单元地址以及执行写操作时序,以转存静态存储器中的待写入数据至对应的存储单元。

8、在其中一些实施方式中,写操作指令包括写命令代码、写地址代码以及待写入数据;响应于写命令代码,写操作硬件加速器使能静态存储器存储待写入数据和使能高电压发生器生成对应的写电压;响应于写地址代码,写操作硬件加速器使能行列译码器生成对应的写单元地址。

9、在其中一些实施方式中,用户指令包括擦操作指令;响应于擦操作指令,擦除操作硬件加速器使能高电压发生器生成对应的擦电压、使能行列译码器生成对应的擦单元地址以及执行擦操作时序,以擦除擦单元地址对应的存储内容。

10、在其中一些实施方式中,擦操作指令包括擦命令代码和擦地址代码;响应于擦命令代码,擦除操作硬件加速器使能高电压发生器生成对应的擦电压;响应于擦地址代码,擦除操作硬件加速器使能行列译码器生成对应的擦单元地址。

11、在其中一些实施方式中,加速模块还包括过擦除校正硬件加速器,过擦除校正硬件加速器包括过擦除校正硬件逻辑电路,用于加速执行过擦除校正操作过程。

12、在其中一些实施方式中,响应于用户指令,控制器启动并监视加速模块。

13、在其中一些实施方式中,在时钟信号的控制下,控制器通过总线与加速模块进行通信;其中,控制器至加速模块的通信通过请求指令、加速指令实现,请求指令用于告知加速模块执行的操作类型,加速指令用于确定通信对象;加速模块至控制器的通信通过应答指令、加速指令实现,应答指令用于告知控制器加速模块的操作状态,加速指令用于明确与控制器通讯的通信对象。

14、第二方面,本发明提供一种闪存芯片,其包括上述至少一个实施方式中的存储控制器和至少一个存储单元,至少一个存储单元与加速模块电性连接。

15、本发明提供的存储控制器及闪存芯片,通过在控制器中植入主程序,基于硬件逻辑电路构成而成的加速模块可以加速执行控制器中的各指令,进而提高了各种操作的执行速度/效率。

16、同时,基于软件程序与硬件加速器这种架构,其能够兼具算法的灵活性和硬件的稳定性;由于控制器执行的内容减少,还可以基于此架构开发自定义指令集,该自定义指令集能够大大减小各种命令的类型和长度。

技术特征:

1.一种存储控制器,其特征在于,包括:

2.根据权利要求1所述的存储控制器,其特征在于,所述存储控制器还包括:

3.根据权利要求2所述的存储控制器,其特征在于,所述用户指令包括读操作指令;

4.根据权利要求3所述的存储控制器,其特征在于,所述读操作指令包括读命令代码和读地址代码;

5.根据权利要求3或者4所述的存储控制器,其特征在于,所述存储控制器还包括串行接口和数据转换模块,所述数据转换模块与所述灵敏放大器的输出端、所述串行接口电性连接,所述读操作硬件加速器使能所述数据转换模块转换所述灵敏放大器输出的并行数据为对应的串行数据,并通过所述串行接口输出所述串行数据至外部。

6.根据权利要求2所述的存储控制器,其特征在于,所述用户指令包括写操作指令;

7.根据权利要求6所述的存储控制器,其特征在于,所述写操作指令包括写命令代码、写地址代码以及所述待写入数据;

8.根据权利要求2所述的存储控制器,其特征在于,所述用户指令包括擦操作指令;

9.根据权利要求8所述的存储控制器,其特征在于,所述擦操作指令包括擦命令代码和擦地址代码;

10.根据权利要求1至9任一项所述的存储控制器,其特征在于,所述加速模块还包括过擦除校正硬件加速器,所述过擦除校正硬件加速器包括过擦除校正硬件逻辑电路,用于加速执行过擦除校正操作过程。

11.根据权利要求1至9任一项所述的存储控制器,其特征在于,响应于所述用户指令,所述控制器启动并监视所述加速模块。

12.根据权利要求1至9任一项所述的存储控制器,其特征在于,在时钟信号的控制下,所述控制器通过总线与所述加速模块进行通信;

13.一种闪存芯片,其特征在于,包括:

技术总结

本发明公开了一种存储控制器及闪存芯片,该存储控制器包括加速模块和控制器,控制器与加速模块电性连接;加速模块包括读操作硬件加速器、写操作硬件加速器以及擦除操作硬件加速器,读操作硬件加速器与控制器电性连接,读操作硬件加速器包括读操作硬件逻辑电路,用于加速执行读操作过程;写操作硬件加速器与控制器电性连接,写操作硬件加速器包括写操作硬件逻辑电路,用于加速执行写操作过程;擦除操作硬件加速器与控制器电性连接,擦除操作硬件加速器包括擦除操作硬件逻辑电路,用于加速执行擦除操作过程,通过控制器基于硬件逻辑电路构成而成的加速模块可以加速执行控制器中的各指令,进而提高了各种操作的执行速度/效率。

技术研发人员:胡俊刚,卢中舟,宋思宪

受保护的技术使用者:武汉新芯集成电路制造有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!