一种9T1C存算电路、乘累加运算电路、存内运算电路、芯片

本发明属于集成电路,具体涉及一种9t1c存算电路,利用9t1c存算电路设计的一种乘累加运算电路,一种基于9t1c-sram的存内运算电路以及基于9t1c-sram的cim芯片。

背景技术:

1、随着信息化技术的不断发展,大数据已经融入到人类社会生活的方方面面,这极大提高了社会的生产效率,也为人类的生活带来了便利。信息化和大规模的数据处理任务离不开各类集成电路的算力支持。近些年来,集成电路制程和工艺的快速迭代印证了摩尔定律,也使得芯片的性能不断提升,芯片的数据处理能力也一直呈指数级增长。但是随着芯片制程工艺达到10纳米以下,单一芯片的运算性能已经很难再产生太大的提升,这制约了集成电路的运算性能。另一方面,基于冯诺依曼架构的计算机系统需要分别在处理器和存储器中进行数据运算和存储,并需要在二者间进行数据传输,这种计算机架构也成为制约算力提升的另一因素。在芯片制程工艺短期难以发生革命性突破的背景下,计算机和大数据领域的科学家现在正将越来越多的精力投入突破到冯诺依曼架构的研究项目中。

2、目前,作为突破冯诺依曼架构的有效策略之一,存内计算(computing in memory,cim)引起了广泛关注。存内计算将存储器与运算模块合二为一,大幅减少了数据的搬移,进而节省了这部分的时间和能耗开销。目前世界上各大学府的科学家,各大公司的科研团队竞相发力,使得对该领域的研究呈现出百花齐放的繁荣景象。

3、其中,sram由于其高速、低功耗和逻辑电路兼容性好的优点被广泛的用于最接近计算单元的高速缓存。目前基于sram的存内计算的研究主要集中在电压域、电流域和电荷域三个部分。标准sram单元是基于电压域信号实现数据存储操作的,而电流域计算单元的主要优点是简单性和与标准sram单元的兼容性,然而由于固有的非线性问题和接入晶体管的工艺变化问题,这两类器件的计算精度都相对较低。电荷域imc(intermetalliccompound)具有更好的计算精度和更高的并行度。计算是在电容上进行的,电容的电流变化比最小尺寸的接入晶体管小得多。同时,基于电荷共享的操作不受晶体管工作区域的影响,可以同时打开更多的电容,从而获得更高的吞吐量和效率增益。但是,基于电荷域sram的存储运算电路的设计更加复杂,难度相对较大,所以这一类的电路设计较前两者方案相对较少,并且通常也无法在功耗、数据存储稳定性和精度,以及逻辑运算性能等多方面同时满足用户的需求。

技术实现思路

1、为了解决现有基于sram的存算电路无法在功耗、稳定性、精度和运算效率等方面实现全面提升的问题,本发明提供一种9t1c存算电路、乘累加运算电路、存内运算电路、芯片。

2、本发明采用以下技术方案实现:

3、一种9t1c存算电路,其具有数据读写保持功能和乘法运算功能。9t1c存算电路由6个nmos管n0~n5,3个pmos管p0~p2和1个电容c0构成,电路连接关系如下:

4、p1的栅极、n1的栅极、p0的漏极、n0的漏极、n2的漏极、n4的栅极相连,并作为存储节点q。p0的栅极、n0的栅极、n1的漏极、p1的漏极、n3的漏极、p2的栅极相连,并作为反向存储节点qb。p0和p1的源极相连并接vdd。n0和n1的源极相连并接vss。n2和n3的栅极接字线wwl;n5的栅极接字线wlr。n2的源极接在位线bl上;n3和n5的源极接在位线blb上。n4的漏极和p2的源极相连,并接在位线il上。n4的源极、p2的漏极、n5的漏极相连并连接在电容c0的右极板,电容c0的左极板连接在位线ol上。

5、在本发明提供的9t1c存算电路的电路结构中,p0和n0构成一个反相器,p1和n1构成另一个反相器;两个反相器构成交叉耦合结构,进而形成用于存储并保持数据的两个存储节点q和qb;n2和n3作为传输管,各自位于交叉耦合结构左右两侧作为两个存储节点写通路;n4和p2构成传输门;n5作为计算控制端,c0作为传输电压差的电容。

6、基于上述电路连接状态,本发明提供的9t1c存算电路在数据读取阶段支持进行单端双向访问。并且9t1c单元在执行乘法运算时既可以完成单比特数间的乘法,也可以完成单比特数与多比特数间的乘法。

7、作为本发明进一步地改进,9t1c存算电路执行数据读写保持的操作逻辑如下:

8、一、数据写操作

9、将字线wlr置为低电平,字线wwl置为高电平;然后,通过位线bl和blb在存储节点q和qb中写入待存储数据。

10、在数据写操作状态下,还可以选择将位线il和ol均置为高电平,以使得电容两端电压保持为高电平,从而使电容两端无电压差,减少电荷的转移,进而降低器件的功耗。

11、二、数据保持操作

12、将字线wlr和wll置为低电平,位线bl、blb、il和ol置为高电平;此时,n2、n3关断,且存储节点q和qb分别连接n4和p2的栅极。

13、分析电路可知:在数据保持状态下,nmos晶体管n2、n3均关断,并且存储节点q和qb分别连接nmos晶体管n4和pmos晶体管p2的栅极。因此,位线bl、blb、ol和il均不会对存储节点q或qb造成影响。pmos晶体管p0、nmos晶体管n0、pmos晶体管p1和nmos晶体管n1构成的锁存结构将可以稳定地锁存存储节点q和qb的数据。

14、三、数据读操作

15、本发明提供的9t1c存算电路是一个具有单端双向访问功能的器件,即支持采用两种不同的方式读取存储节点的数据。具体地,本发明提供的9t1c存算电路支持的数据读操作分为如下的列读模式和行读模式:

16、1、在列读模式时,将字线wwl置为低电平,字线wlr置为高电平,位线bl、blb和ol置为高电平,位线il置为低电平,qb节点的读操作结果体现在位线blb上:

17、(1)如果位线blb可以保持高电平,则表示节点qb存储的数据为1,节点q存储的数据为0。

18、(2)如果位线blb的电压下降,则代表节点qb存储的数据为0,节点q存储的数据为1。

19、2、在行读模式时,将字线wwl置为低电平,字线wlr置为高电平,位线bl、blb和ol置为高电平,位线il置为低电平,q节点的读操作结果体现在位线il上:

20、(1)如果位线il可以保持低电平,则表示节点q存储的数据为0,相应地,节点qb存储的数据为1。

21、(2)如果位线il的电压升高,则代表节点q存储的数据为1,相应地,节点qb存储的数据为0。

22、作为本发明进一步地改进,9t1c存算电路执行乘法运算包括单乘单模式和单乘多模式两种,具体的操作逻辑如下:

23、(1)在数据写入模式下,将第一操作数写入到9t1c存算电路的存储节点q。

24、此外,需要强调的是,第一操作数的写入操作并非必须。因为对于每个9t1c存算电路而言,在上电后,存储节点q或qb中必然已经存储有数据,本发明还可以直接选择相应的9t1c存算电路来执行本方案的乘法运算任务,因而无需额外进行数据写入。

25、(2)对各条信号线进行预充,分别包括:将位线ol置为高电平,il置为低电平,wlr置为高电平,wwl置为低电平,blb置为低电平。

26、(3)将第二操作数通过位线il输入到9t1c存算电路中。

27、其中,在单乘单模式下,输入的第二操作数为表征二进制数1或0的高低电平。而在单乘多模式下,第二操作数为由多位二进制数按预设规则进行数模转换后得到的对应的电压值vdac。

28、(4)将位线ol悬空,然后获取c0中电荷重新分配后位线ol的当前电压,并将其量化为乘积结果。

29、其中,在单乘单模式下,位线ol的电压为vdd时表示乘积结果为0,位线ol的电压为0时表示乘积结果为1。而在单乘多模式下,当第一操作数为0时,位线ol的电压为vdd,即乘积结果为0;当第一操作数为1时;位线ol的电压为vdd-vdac;vdd-vdac经预设规则的数转换后得到一个多位二进制数,即为乘积。

30、作为本发明进一步的改进,9t1c存算电路在非运算阶段应进行归零操作,以降低电路的功耗;归零操作的操作逻辑如下:

31、将字线wwl置为低电平,字线wlr置为高电平,位线bl、blb、ol、il置为高电平,通过n5由blb对电容c0的左极板充电,使电容c0两端电压差清零。

32、在上述9t1c存算电路,本发明进一步提供一种乘累加运算电路,其包括:运算阵列、字线组、位线组、输入信号线il,输出信号线ol、列开关s和量化电路。

33、其中,运算阵列由n个前述的9t1c存算电路按列排布而成。字线组包括n条字线wll和n条字线wlr。运算阵列中的各个9t1c存算电路均连接一组独立的字线wll和wlr;字线wll和wlr用于在乘累加运算前选中各行的9t1c存算电路以便写入乘累加运算的第一操作数。位线组包括1条位线bl和1条位线blb;同列的所有9t1c存算电路均连接在相同的位线bl、blb上,位线bl、blb用于在各个9t1c存算电路中写入乘累加运算的第一操作数。

34、输入信号线il的数量为n条;运算阵列中每个9t1c存算电路分别连接一条独立的输入信号线il,并作为各自运算过程中第二操作数的输入端。输出信号线ol的数量为1条,同列的所有9t1c存算电路均连接在该条输出信号线ol上,ol作为乘累加运算结果的输出端。列开关s连接在输出信号线ol与电源vdd之间,用于控制输出信号线ol与电源vdd的连通状态。

35、量化电路连接在输出信号线ol上,用于将输出信号线ol上的电压值转换为一个表征乘累加运算结果的数字量。

36、作为本发明进一步的改进,该型乘累加运算电路执行乘累加运算的操作逻辑如下:

37、(1)准备阶段:

38、对运算阵列中的所有9t1c存算电路进行归零操作,以保证运算阵列中所有电容c0的初始状态相同,即电容c0的右极板电压vc保持一致。

39、(2)预存阶段:

40、依次将各行的字线wlr置为低电平,字线wwl置为高电平。然后,通过位线bl和blb在各行的9t1c存算电路中的存储节点中写入各自的第一操作数。

41、(3)预充阶段:

42、将列开关s闭合,输出信号线ol连接vdd,使各个电容c0的左极板预充为vdd;wlr置于高电平,blb预充为低电平,使各个电容c0右极板预充为“0”;位线il预充为低电平。

43、(4)乘积运算阶段

44、通过输入信号线il向各个9t1c存算电路输入经数模转换后的输入电压vdac。此时wlr置为低电平,列开关s依旧闭合,各个9t1c存算电路中的电容c0两端的电压差根据存储单元q值发生如下改变:

45、a.当q=“1”时,传输门打开,输入值通过传输门输入到电容c0的右极板,电容c0的左极板电压保持为vdd,电容c0的右极板电压保持为vdac;此时,电容c0的两端电压差为vdd-vdac。

46、b.当q=“0”时,传输门关闭;电容c0的左极板电压保持为vdd,电容c0的右极板电压为0;此时,电容c0的两端电压差仍保持为vdd。

47、由此可知:各个9t1c存算电路的乘法结果均累积到了各自电容c0的右极板上。

48、(5)累加运算阶段:

49、将列开关s断开,使输出信号线ol悬空,即电容左极板悬空。然后,将wlr置为高电平,位线il置为低电平,使各行中电容c0左极板电压根据存储单元q值发生如下改变;

50、a.当q=“1”时,传输门打开,电容c0的右极板电压值被位线il拉低为0,此时由于电容c0的两端电压差不能突变,并且乘法运算阶段电容c0的电压差为vdd-vdac,所以电容c0的左极板电压值即变为vdd-vdac。

51、b.当q=“0”时,传输门关闭,电容c0的两端电压差仍保持vdd,所以电容c0的左极板电压保持vdd。

52、此时,每个9t1c存算电路的乘法结果体现为电源电压vdd减去电容c0左极板电压的值;由于一列的位线ol共享,所以各个9t1c存算电路中电容c0的左极板电荷进行共享,在位线ol上得到最后乘累加结果对应的模拟量。

53、(6)量化输出

54、按照预设的模数转换规则将ol的电压值转换为对应数字量,即为最终的乘累加运算结果。

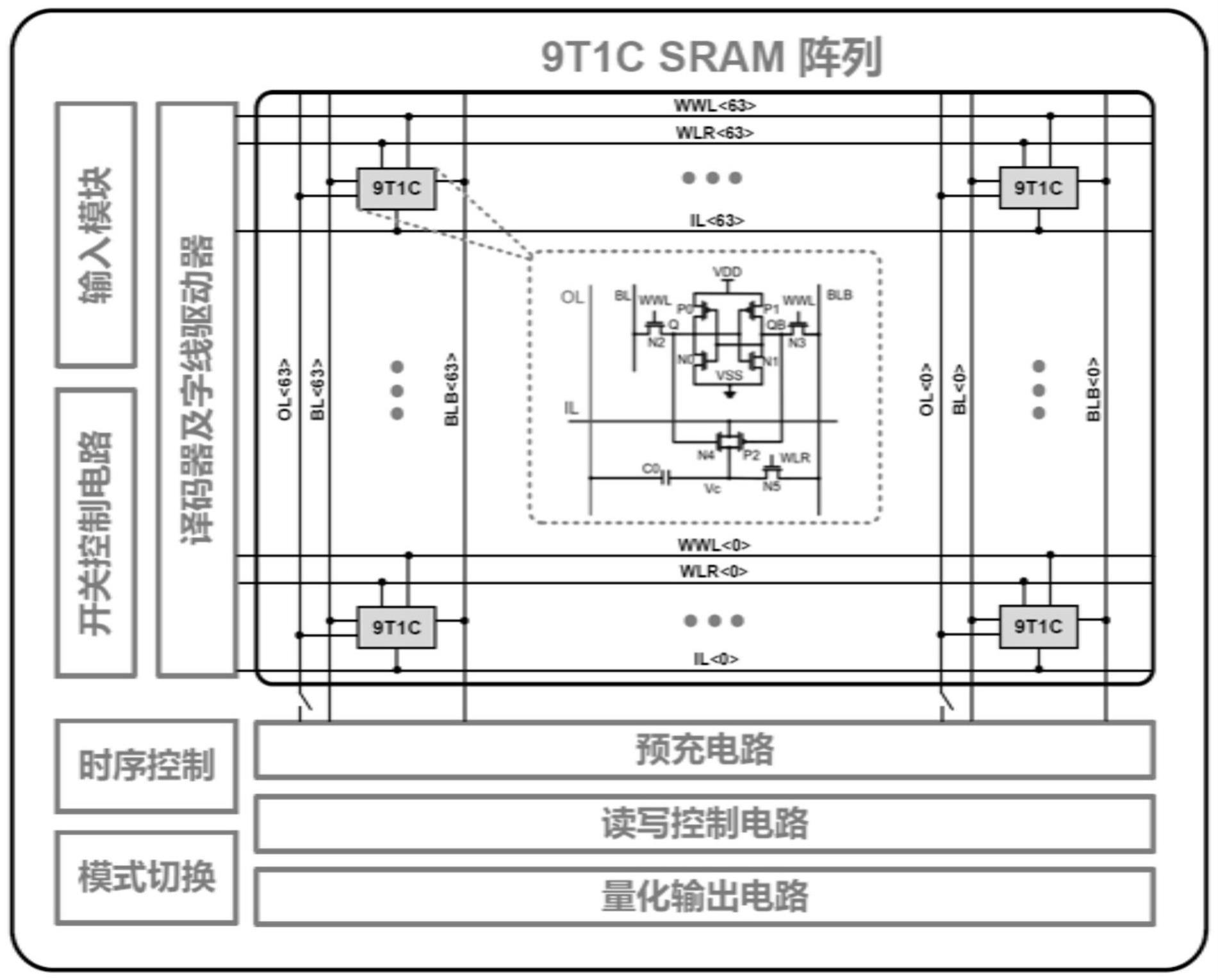

55、本发明还包括一种基于9t1c-sram的存内运算电路,其具有数据读写保持功能、乘法运算功能和乘累加运算功能。并在数据读阶段支持进行单端双向访问;而电路支持的乘法和乘累加运算功能包括单比特乘法和多比特乘法。具体地,按照功能划分,本发明提供的基于9t1c-sram的存内运算电路包括:存算阵列、字线组、位线组、输入信号线组、输出信号线组、字线驱动器、译码器、预充电路、时序控制模块、模式切换、读写控制电路、开关控制电路、输入模块,以及量化输出电路。

56、其中,存算阵列由n×m个前述的9t1c存算电路按n行m列的阵列方式排布而成。字线组包括n条字线wll和n条字线wlr。存算阵列中的同行的各个9t1c存算电路均连接在同一组字线wll和wlr上。位线组包括m条位线bl和m条位线blb。存算阵列中同列的所有9t1c存算电路均连接在相同的位线bl、blb上;输入信号线组包括n条输入信号线il;存算阵列中同行的所有9t1c存算电路均连接在一条输入信号线il。输出信号线组包括m条输出信号线ol。存算阵列中同列的所有9t1c存算电路均连接在一条输出信号线ol上。

57、字线驱动器用于控制各条字线wlr和wwl的开启。译码器与字线驱动器连接,译码器用于将地址信号译码后传入到字线驱动器。预充电路用于对位线bl、blb和输出信号线ol进行预充操作;时序控制模块用于生成执行数据存储任务或执行乘法运算和乘累加运算过程中所需的各个时钟信号。模式切换用于切换存内运算电路的工作模式,存内运算电路的工作模式包括数据存储模式和逻辑运算模式。读写控制电路用于对存内运算电路执行数据读写操作的过程进行控制。

58、开关控制电路包括m个列开关s,每个列开关s分别连接在其中一条输出信号线ol与电源vdd之间,用于控制该输出信号线ol与电源vdd的连通状态。输入模块在乘法运算或乘累加运算阶段对第二操作数进行数模转换,然后通过输入信号线il输入到对应的9t1c存算电路中。

59、量化输出电路连接在输出信号线ol、位线blb和输入信号线il上;量化输出电路包括数据读部分和运算输出部分。数据读部分用于输出各存储节点的存储数据;运算输出部分用于对ol的电压进行模数转换,输出对应的乘法运算结果或乘累加运算结果。

60、作为本发明进一步的改进,在存算阵列中,各个9t1c存算电路作为实现数据存储功能和乘法运算功能的基本单元。同一列中的所有9t1c存算电路与列开关s共同构成执行乘累加运算的基本单元。该基于9t1c-sram的存内运算电路中各列的9t1c存算电路支持并行执行乘累加运算。

61、本发明还包括一种基于9t1c-sram的cim芯片,其由如前述的基于9t1c-sram的存内运算电路封装而成。

62、本发明提供的技术方案,具有如下有益效果:

63、本发明设计的9t1c-sram器件是一种电荷域型sram器件,该器件具有常规的数据读写和保持性能,并且还可以实现单比特和多比特的乘法运算,是一种性能更优的cim电路;应用前景更加广阔。

64、本发明方案提供的电路中,计算过程是在电容上进行的,电容的电流变化比最小尺寸的接入晶体管小得多。同时,基于电荷共享的操作不受晶体管工作区域的影响,可以同时打开更多的电容,从而获得更高的吞吐量和效率增益,可大幅提高乘累加运算的效率和精度。

65、本发明提供的器件利用电容两端电压不能突变的特点,进行乘法计算和加法计算,提高了线性度和计算精度。该器件可以实现单边计算,并支持无损失等分多位输入,因而具有更高的计算精度和并行度。

66、本发明提供的9t1c-sram从数据存储功能角度看,电路结构简单,具有较低的功耗。并且因为采用读解耦的方式,可以有效解决读破坏问题;提高电路中存储的数据的安全性和稳定性。

- 还没有人留言评论。精彩留言会获得点赞!