一种用于闪存芯片的测试电路及其装置的制作方法

1.本实用新型涉及存储器测试技术领域,具体涉及一种用于闪存芯片的测试电路及其装置。

背景技术:

2.目前,flash(闪存)的应用非常广阔,可以应用在诸如移动存储、5g、车联网及人工智能等不同的技术领域。随着闪存芯片的制造工艺的不断更新,产量不断增加,其检测良率的需求也不断上升。制造厂商需要更换新的控制器进行调试,同时终端厂商也需要投入新的测试仪器进行闪存芯片的测试。

3.现有的flash(eeprom/spi nor/spi nand)存储器的封装品测试设备主要是烧录器。这些烧录器的程序基本都固化在设备内部,而且只能进行一些固定的测试项目,例如擦除、编程、读取芯片内容,而对于芯片的指令、地址、数据等不能随意更改。因此,用户无法根据特定需求,通过修改测试代码方式来更改程序,并进行相关的测试。

4.有鉴于此,需要对现有技术问题提出解决方法。

技术实现要素:

5.本实用新型的目的在于,本实用新型一实施例提供了一种用于闪存芯片的测试电路及其装置,其旨在满足用户的不同需求而允许用户修改测试程序的测试代码,以适用于闪存芯片的终端测试,也适用于验证闪存芯片的性能测试;当用于闪存芯片的终端测试时,可以极大地提高芯片的出货良率,并减少客户的投诉;当用于验证闪存芯片的性能测试时,可以根据用户的需求而相应调整测试电压、频率,从而实现各种时序。

6.根据本实用新型的一方面,本实用新型的一实施例提供了一种用于闪存芯片的测试电路,所述测试电路包括主芯片、烧录电路和芯片接口电路;所述烧录电路与所述主芯片电连接,所述烧录电路用于接收来自外部的烧录程序数据,并且将所述烧录程序数据经由所述主芯片传送至所述芯片接口电路;所述芯片接口电路与所述主芯片电连接,所述芯片接口电路用于对接不同的闪存芯片,并且根据所述烧录程序数据对所述闪存芯片进行不同的测试。

7.可选地,在一些实施例中,所述烧录电路包括第一芯片和第二芯片,所述第一芯片具有多个复用引脚,所述多个复用引脚连接用以提供烧录程序数据的外部设备,并且与所述第二芯片的相应输入引脚电连接,所述第二芯片的输出引脚与所述主芯片的相应引脚电连接。

8.可选地,在一些实施例中,所述芯片接口电路包括第三芯片,所述第三芯片具有片选引脚、输入引脚和输出引脚;所述片选引脚用于接收所述主芯片的片选信号,以使能所对接的闪存芯片,所述输入引脚和所述输出引脚用于使所述第三芯片与所述主芯片之间进行数据和地址的传输。

9.可选地,在一些实施例中,所述测试电路还包括晶振电路,所述晶振电路的第四芯

片与所述主芯片电连接,所述第四芯片用于驱动主芯片内部的逻辑电路,并且配置所述主芯片的锁相倍频,以及调整测试闪存芯片的工作电压的范围。

10.可选地,在一些实施例中,所述测试电路还包括按键电路,所述按键电路包括多个分支电路,每一所述分支电路电连接至所述主芯片的相应引脚;其中每一所述分支电路对应一按键,所述按键电路用于当检测到按键触点的电压为预设电压时,使得对应的分支电路导通。

11.可选地,在一些实施例中,所述测试电路还包括扩展接口电路,所述扩展接口电路包括第五芯片,所述第五芯片与所述主芯片电连接;所述扩展接口电路用于连接设有所述测试电路的测试板与外部设备,以使外部设备提供数据和电源给所述测试板。

12.可选地,在一些实施例中,所述测试电路还包括调试电路,所述调试电路包括第六芯片,所述第六芯片与所述主芯片电连接,所述第六芯片用于连接外部的仿真器,以接收所述仿真器的调试指令,并传送至所述主芯片。

13.可选地,在一些实施例中,所述测试电路还包括第一警示电路,所述第一警示电路与所述主芯片电连接,所述第一警示电路包括多个发光二极管,每一所述发光二极管用于根据不同的闪存芯片的测试状态而被相应点亮。

14.可选地,在一些实施例中,所述测试电路还包括第二警示电路,所述第二警示电路与所述主芯片电连接,所述第二警示电路包括蜂鸣器,所述蜂鸣器用于根据所述主芯片的控制指令发出蜂鸣。

15.可选地,在一些实施例中,所述测试电路还包括显示电路,所述显示电路具有第七芯片,所述第七芯片具有输入引脚和输出引脚,并且与所述主芯片电连接;所述显示电路用于连接外部的显示装置,以显示闪存芯片的测试结果。

16.可选地,在一些实施例中,所述闪存芯片包括eeprom、spi nor、spi nand和sd芯片中的其中一种。

17.根据本实用新型的另一方面,本实用新型的一实施例提供了一种测试装置,其包括一测试板;在所述测试板上设有本实用新型任一实施例所述的测试电路。

18.本实用新型的有益效果在于,本实用新型实施例所述用于闪存芯片的测试电路可以满足用户的不同需求而允许用户修改测试程序的测试代码,以适用于闪存芯片的终端测试,也适用于验证闪存芯片的性能测试;当用于闪存芯片的终端测试时,可以极大地提高芯片的出货良率,并减少客户的投诉;当用于验证闪存芯片的性能测试时,可以根据用户的需求而相应调整测试电压、频率,从而实现各种时序。

附图说明

19.下面结合附图,通过对本实用新型的具体实施方式详细描述,将使本实用新型的技术方案及其它有益效果显而易见。

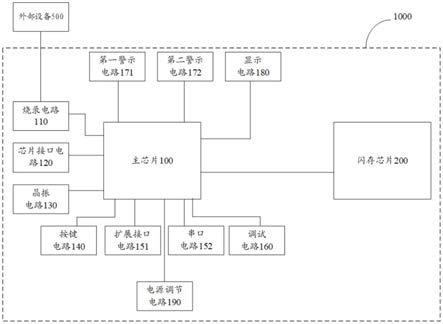

20.图1为本实用新型一实施例所提供的一种用于闪存芯片的测试电路的结构示意图。

21.图2为主芯片的电路示意图。

22.图3为烧录电路的电路示意图。

23.图4为芯片接口电路的示意图。

24.图5为晶振电路的示意图。

25.图6为按键电路的示意图。

26.图7a为扩展接口电路的示意图。

27.图7b为串口电路的示意图。

28.图8为调试电路的示意图。

29.图9为第一警示电路的示意图。

30.图10为第二警示电路的示意图。

31.图11为显示电路的示意图。

32.图12为电源调节电路的示意图。

33.图13为本实用新型一实施例所提供的测试装置的示意图。

具体实施方式

34.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

35.文中的术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个所述特征。在本实用新型的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

36.在本实用新型的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接或可以相互通讯;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本实用新型中的具体含义。

37.下文的公开提供了许多不同的实施方式或例子用来实现本实用新型的不同结构。为了简化本实用新型的公开,下文中对特定例子的部件和设置进行描述。当然,它们仅仅为示例,并且目的不在于限制本实用新型。此外,本实用新型可以在不同例子中重复参考数字和/或参考字母,这种重复是为了简化和清楚的目的,其本身不指示所讨论各种实施方式和/或设置之间的关系。

38.本实用新型的一实施例提供了一种用于闪存芯片的测试电路。所述测试电路包括主芯片、烧录电路和芯片接口电路。所述烧录电路与所述主芯片电连接,所述烧录电路用于接收来自外部的烧录程序数据,并且将所述烧录程序数据经由所述主芯片传送至所述芯片接口电路。所述芯片接口电路与所述主芯片电连接,所述芯片接口电路用于对接不同的闪存芯片,并且根据所述烧录程序数据对所述闪存芯片进行不同的测试。

39.本实用新型所述测试电路可以满足用户的不同需求而允许用户修改测试程序的测试代码,以适用于闪存芯片的终端测试,也适用于验证闪存芯片的性能测试;当用于闪存芯片的终端测试时,可以极大地提高芯片的出货良率,并减少客户的投诉;当用于验证闪存芯片的性能测试时,可以根据用户的需求而相应调整测试电压、频率,从而实现各种时序。

40.以下将结合附图进一步描述所述测试电路的各个电路及其功能。

41.如图1和图2所示,在本实施例中,所述测试电路1000包括主芯片100。该主芯片100为m48sside芯片。此芯片封装形式lqfp 64,具有52个io可供用户使用。而且主芯片100包括512kb flash、sram 160kb、32-bit timer(定时器)以及12bit adc/dca转换器。主芯片100可以与不同的闪存芯片、扩展接口、外部的显示装置和警示装置电连接。其中闪存芯片包括eeprom(带电可擦可编程只读存储器)、spi nor、spi nand(nor型和nand型的非易失性存储器)和sd芯片中的其中一种。扩展接口包括usb接口、uart接口,但不限于此。

42.如图3所示,在本实施例中,烧录电路110包括第一芯片p5和第二芯片u4。所述第一芯片p5具有多个复用引脚,所述多个复用引脚连接用以提供烧录程序数据的外部设备,并且与所述第二芯片u4的相应输入引脚电连接。所述第二芯片u4的输出引脚与所述主芯片100的相应引脚电连接。

43.具体地,所述第一芯片p5的复用引脚包括第3引脚、第5引脚、第7引脚和第9引脚,所述第一芯片p5的第3引脚、第5引脚、第7引脚和第9引脚分别与所述第二芯片u4的第14引脚(即voa引脚)、第13引脚(即vob引脚)、第11引脚(即vid引脚)和第12引脚(即voc引脚)连接。且,所述第一芯片p5的上述这些引脚分别与外部设备的引脚(或插针)电连接,用以接收外部设备所提供且与不同闪存芯片200相对应的烧录程序数据。所述第二芯片u4的第3引脚(即via引脚)、第4引脚(即vib引脚)和第5引脚(即vic引脚)和第6引脚(即vod引脚)分别通过电阻(nr3 22r)连接至所述主芯片100的第1引脚(即ate_busy引脚)、第64引脚(即ate_ok引脚)、第63引脚(即ate_ng引脚)和第62引脚(即ate_start引脚)。

44.通过上述烧录电路110的设计,可以实现外部设备(例如烧录器)与烧录电路110电连接。烧录器通过烧录电路110将烧录程序数据(即程序代码)经由主芯片100以提供至芯片接口电路120。于是,可以基于预设程序对所对接的不同闪存芯片进行测试,包括性能测试或量产测试。当闪存芯片200开始测试时,ate_start引脚为低电平。当闪存芯片200进行测试时,ate_busy引脚为低电平。当闪存芯片200测试正常结束时,ate_ok引脚为低电平。当闪存芯片200测试过程中有错误时,ate_ng引脚为低电平。换言之,在本实施例中,当上述引脚为低电平时,即表示有效。

45.如图4所示,在本实施例中,所述芯片接口电路120包括第三芯片p7,所述第三芯片p7具有片选引脚、输入引脚和输出引脚。所述片选引脚用于接收所述主芯片100的片选信号,以使能所对接的闪存芯片(例如spi nor芯片,spi nand芯片),所述输入引脚和所述输出引脚用于使所述第三芯片p7与所述主芯片100之间进行数据和地址的传输。

46.具体地,所述第三芯片p7的片选引脚(即第9引脚,此处可以定义为qspi_ss引脚)连接至所述主芯片100的第27引脚(即pa.3引脚)。所述第三芯片p7的输入引脚包括所述第三芯片p7的第11引脚(即qspi_mosi1引脚)和第13引脚(即qspi_mosi 0引脚),所述第三芯片p7的第11引脚和第13引脚分别连接至所述主芯片100的第26引脚(即pa.4引脚)和第30引脚(即pa.0引脚)。所述第三芯片p7的输出引脚包括第10引脚(即qspi_miso0引脚)和第15引脚(即qspi_miso1引脚),所述第三芯片p7的第10引脚和第15引脚分别连接至所述主芯片100的第29引脚(即pa.1引脚)和第25引脚(即pa.5引脚)。

47.需要说明的是,由于芯片接口电路120可以对接不同类型的闪存芯片,因此,芯片接口电路120中的同一个引脚可以支持不同类型闪存芯片所对应的信号。如图4所示,例如

像以“qspi”开头的信号表示与spi nor芯片或spi nand芯片相关。又例如像以“sd1”开头的信号表示与sd芯片相关。又例如像以“i2c1”开头的信号表示与eeprom芯片相关。换言之,设有所述测试电路1000的测试板2000(如图13所示)预留了与spi nor芯片、spi nand芯片、sd芯片及eeprom芯片相关的接口。用户可以根据需求加载一不限容量的spi nor芯片、spi nand芯片、sd芯片及eeprom芯片。于是,可以进行spi nor芯片、spi nand芯片、sd芯片及eeprom芯片的量产测试、性能测试和验证测试。若是量产测试,即批量出货给客户的测试方式,需要对测试板和芯片的参数进行预先配置,在测试过程中不再发生改变。若是性能测试,即验证闪存芯片的测试,在测试过程中需要不断调整芯片的各项参数,并观察测试结果是否与预期值一致,以达到验证芯片的各项功能是否满足需求。其中各项功能包括测试电压、测试频率、测试参数,均可以灵活调整。此外,由于芯片接口电路120可以支持spi型的闪存芯片的访问,而该类型的闪存芯片具有非易失特性,因此,qspi型闪存芯片也可以作为系统的启动数据。

48.如图5所示,在本实施例中,所述测试电路1000还包括晶振电路130,所述晶振电路130的第四芯片y1与所述主芯片100电连接,所述第四芯片y1用于驱动主芯片100内部的逻辑电路,并且配置所述主芯片100的锁相倍频,以及调整测试闪存芯片的工作电压的范围。

49.具体地,所述晶振电路130具有输入端(hxt_i)和输出端(hxt_o),该输入端与主芯片100的第16引脚(即pf.3引脚)电连接,该输出端与主芯片100的第17引脚(即pf.2引脚)电连接。用户可以通过晶振电路130来配置主芯片100内部的锁相环倍频,以实现更高的时钟频率。进一步地,可以通过主芯片100内部的倍频和分频电路以产生不同的频率(几百khz到100mhz)。而且,所述晶振电路130为12m无源晶振电路,可用于实现在测试闪存芯片过程中对闪存芯片的工作电压的调节,工作电压范围为1.8v至5v,从而支持不同闪存芯片的不同电压测试。

50.如图6所示,在本实施例中,所述测试电路1000还包括按键电路140。所述按键电路140包括多个分支电路,每一所述分支电路电连接至所述主芯片100的相应引脚。其中每一所述分支电路对应一按键(s1、s2、s3),所述按键电路140用于当检测到按键触点的电压为预设电压时,使得对应的分支电路导通。

51.具体地,所述按键电路140包括三个分支电路,分支电路的数量不限于此。每一分支电路(key1,key2,key3)对应一按键(如图6所示的s1,s2,s3),每一所述分支电路(key1,key2,key3)的一端接地,另一端连接至主芯片100的相应引脚。这些引脚分别为主芯片100的第15引脚(即pf.4引脚)、第18引脚(即pc.7引脚)和第19引脚(即pc.6引脚)。需说明的是,按键电路140检测到按键触点为预设电平(例如低电平)时,即确定相应的分支电路为导通,于是用户可以根据测试需求对按键的功能进行开发,以实现通过按键的选择来确定相应的闪存芯片类型(eeprom/spi nor/spi nand)、测试电压、测试频率、测试项目、测试模式,如此设计,使得测试电路具有灵活选择的特点。

52.如图7a所示,在本实施例中,所述测试电路1000还包括扩展接口电路151。所述扩展接口电路151包括第五芯片type-c1,所述第五芯片type-c1与所述主芯片100电连接。所述扩展接口电路151用于连接设有所述测试电路1000的测试板2000(如图13所示)与外部设备(图中未示),以使外部设备提供数据和电源给所述测试板。

53.具体地,如图7a所示,所述扩展接口电路151包括第五芯片type-c1,第五芯片的

dn2引脚电连接至主芯片100的第44引脚(即usb_hs_d-引脚),第五芯片的dp2引脚电连接至主芯片100的第46引脚(即usb_hs_d+引脚)。通过上述设计,可以实现通过所述扩展接口电路151将设有所述测试电路1000的测试板2000与外部设备(例如个人电脑,不限于此)进行连接,以使外部设备可以提供数据和电源给测试板。需说明的是,在本实施例中,扩展接口电路151为usb接口电路,使得设有测试电路1000的测试板与外部设备连接。进一步地,两者之间可以进行usb2.0的高速通信。而且,通过上述usb接口电路,不仅可以使得外部设备给测试板供电,而且也可以将测试数据输出至外部设备,以供后继操作。若是在调试过程中的变量值、测试电压、测试频率、循环次数等,均可以输出,从而给开发人员提供了便利。

54.如图7b所示,可选地,所述测试电路1000还包括串口电路152。在本实施例中,所述串口电路152为usb接口转串口电路,其用于相连设有测试电路1000的测试板2000与外部设备。换言之,测试板2000可以通过usb接口转串口与外部设备进行通信。

55.如图8所示,在本实施例中,所述测试电路1000还包括调试电路160,所述调试电路160包括第六芯片p1,所述第六芯片p1与所述主芯片100电连接,所述第六芯片p1用于连接外部的仿真器(图中未示),以接收所述仿真器的调试指令,并传送至所述主芯片100。

56.如图8所示,所述调试电路160的第六芯片p1的第1引脚连接3.3v电源,第2引脚连接主芯片100的第33引脚(即pf.0引脚,此处可定义为ice_dat引脚),第3引脚连接主芯片100的第34引脚(即pf.1引脚,此处可定义为ice_clk引脚),第4引脚连接主芯片100的第32引脚(即nreset引脚,此处可定义为ice_rst引脚)。通过上述的电路设计,用户可以通过仿真器进入调试模式,在程序的调试过程中实时观察变量的值,并且能够灵活地实现单步运行,从而及时发现程序中的错误。

57.如图9所示,所述测试电路1000还包括第一警示电路171,所述第一警示电路171与所述主芯片100电连接,所述第一警示电路171包括多个发光二极管,每一所述发光二极管用于根据不同的闪存芯片的测试状态而被相应点亮。

58.具体地,所述第一警示电路171包括四个发光二极管,分别为黄光、绿光、蓝光和红光,每一个发光二极管分别连接至主芯片100的第1引脚(即ate_busy引脚)、第64引脚(即ate_ok引脚)、第63引脚(即ate_ng引脚)和第62引脚(即ate_start引脚)。于是,用户可以通过量产测试过程中实时观察内存芯片的测试情况。当闪存芯片200开始测试时,与ate_start引脚相连的发光二极管点亮。当闪存芯片200测试过程中时,与ate_busy引脚相连的发光二极管点亮。当闪存芯片200测试正常结束时,与ate_ok引脚相连的发光二极管点亮。当闪存芯片200测试过程中有错误时,与ate_ng引脚相连的发光二极管点亮。

59.如图10所示,在一些实施例中,所述测试电路1000还包括第二警示电路172。所述第二警示电路172与所述主芯片100电连接,所述第二警示电路172包括蜂鸣器。所述蜂鸣器用于根据所述主芯片100的控制指令发出蜂鸣。

60.具体地,所述第二警示电路172包括蜂鸣器、开关管和若干电阻。所述蜂鸣器通过两个分支电路各自连接至所述主芯片100的第43引脚(即hsusb_vbus引脚)和第14引脚(即pf.5引脚,此处可定义为swdh_srt引脚)。这样,在测试过程中,若测试有失效,可以通过预配置的第二警示电路172来产生警示声音,以提示用户在测试过程中产生了异常数据。

61.如图11所示,所述测试电路1000还包括显示电路180,所述显示电路180具有第七芯片u7,所述第七芯片u7具有输入引脚和输出引脚,并且与所述主芯片100电连接;所述显

示电路180用于连接外部的显示装置,以显示闪存芯片的测试结果。

62.具体地,第七芯片u7的第3引脚(即sda引脚)连接至主芯片100的第3引脚(即pb.4引脚,此处可定义为spi1_mosi引脚)。第七芯片u7的第4引脚(即scl引脚)连接至主芯片100的第4引脚(即pb.3引脚,此处可定义为spi1_clk引脚)。第七芯片的第5引脚(即rs引脚)连接至主芯片100的第2引脚(即pb.5引脚,此处可定义为spi1_miso引脚)。第七芯片u7的第6引脚(即reset引脚)连接至主芯片100的第11引脚(即pa.8引脚,此处可定义为lcd_rst引脚)。第七芯片u7的第7引脚(即cs引脚)连接至主芯片100的第5引脚(即pb.2引脚,此处可定义为spi1_ss引脚)。第七芯片的第11引脚(即ledk引脚)电连接至主芯片100的第8引脚(即pa.11引脚,此处可定义为lcd_blk引脚)。通过上述配置,可以使测试板2000与外部的显示装置相连。显示装置可以实时显示所测试的内容,包括闪存芯片的类型、测试电压、测试频率、测试项目、测试模式等。另外,用户也可以自定义所需显示的内容,例如测试程序的更新日期,以防止误下载其他日期的测试程序。

63.如图12所示,所述测试电路1000还包括电源调节电路190,所述电源调节电路190包括第八芯片u5和第九芯片u6。第八芯片u5和第九芯片u6共同连接至主芯片100的第43引脚(即hsusb_vbus引脚)。其中的第九芯片u6还连接至主芯片100的第56引脚(即pb.12引脚,此处可定义为dac0_out引脚)以及主芯片100的第55引脚(即pb.13引脚,此处可定义为adc_ch13引脚)。需说明的是,第八芯片u5和第九芯片u6为电源调节芯片。第八芯片u5固定输出3.3v电压,第九芯片u6通过adc(数模转换器)输出不同的电压至主芯片100,然后主芯片100再相应地输出至部分从芯片,例如上文的第二芯片u4、第六芯片p1和第七芯片u7,但不限于此。

64.因此,本实用新型所述测试电路1000可以满足用户的不同需求而允许用户修改测试程序的测试代码,以适用于闪存芯片的终端测试,也适用于验证flash芯片的性能测试。当用于闪存芯片的终端测试时,可以极大地提高芯片的出货良率,并减少客户的投诉。当用于验证flash芯片性能时,可以根据用户的需求而相应调整测试电压、频率,从而实现各种时序,相当于一小型测试机。

65.如图13所示,基于同一个实用新型构思,本实用新型的一实施例提供了一种测试装置3000,其包括一测试板2000。在所述测试板2000上设有上述实施例所述的测试电路1000。该测试电路1000的具体结构在此不再赘述。

66.本实用新型所述测试装置3000可以实现对闪存芯片的各种操控功能。这样,可适用于量产测试、性能测试和新研发产品的验证等。当进行闪存芯片的量产测试时,可以根据测试程序,配置闪存芯片的各项参数,增加测试项目,从而提高出货芯片的良率、可靠性等各项参数,并且极大地减少客户的投诉,为产品的质量进一步做保障。当进行闪存芯片的性能测试时,可以实现验证芯片的各项参数,例如擦除时间、写入时间、读出时间、动态电流等。当进行新研发产品的验证时,可以验证新品的各项功能是否如预期的一样,例如擦除是否正常、擦除的时间是否能控制在预期之内、写入数据是否正常、读出数据是否正常等等。

67.在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述的部分,可以参见其他实施例的相关描述。

68.以上对本实用新型实施例所提供的一种用于闪存芯片的测试电路及其装置进行了详细介绍,本文中应用了具体个例对本实用新型的原理及实施方式进行了阐述,以上实

施例的说明只是用于帮助理解本实用新型的技术方案及其核心思想;本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本实用新型各实施例的技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1