一种信号采样电路以及半导体存储器的制作方法

本公开涉及集成电路,尤其涉及一种信号采样电路以及半导体存储器。

背景技术:

1、随着半导体技术的不断发展,人们在制造和使用计算机等设备时,对数据的传输速度提出了越来越高的要求。为了获得更快的数据传输速度,应运而生了一系列数据可以双倍速率(double data rate,ddr)传输的存储器等器件。

2、在动态随机存取存储器(dynamic random access memory,dram)中,输入的命令地址信号既可以作为地址进行采样又可以作为指令进行采样译码。在输入的命令地址信号作为指令时,需要采样译码得到译码信号。然而,译码信号的脉冲宽度存在不确定性,可能会导致数据失效,影响了半导体的性能。

技术实现思路

1、本公开提供了一种信号采样电路以及半导体存储器,能够改善信号脉冲宽度存在不确定性的问题,提高目标指令信号的质量。

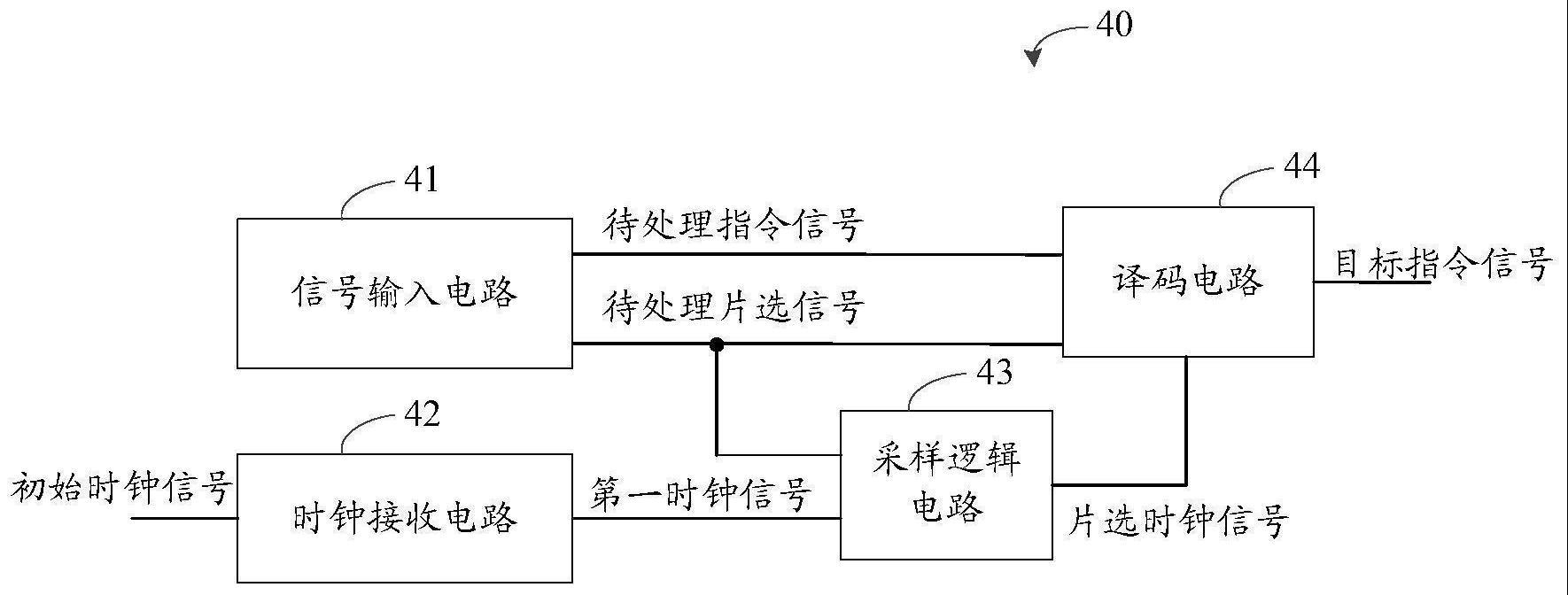

2、第一方面,本公开实施例提供了一种信号采样电路,所述信号采样电路包括信号输入电路、时钟接收电路、采样逻辑电路和译码电路;其中,

3、所述信号输入电路,用于确定待处理指令信号和待处理片选信号;

4、所述时钟接收电路,用于接收初始时钟信号,并对所述初始时钟信号进行分频处理,得到第一时钟信号;其中,所述初始时钟信号的时钟周期为预设时钟周期,所述第一时钟信号的时钟周期为所述预设时钟周期的2倍;

5、所述采样逻辑电路,用于根据所述第一时钟信号对所述待处理片选信号进行两级采样处理和逻辑运算处理,得到片选时钟信号;其中,所述片选时钟信号包括两个脉冲,且每个脉冲的宽度为预设时钟周期;

6、所述译码电路,用于根据所述待处理片选信号和所述片选时钟信号对所述待处理指令信号进行译码处理和采样处理,得到目标指令信号。

7、在一些实施例中,所述目标指令信号包括一个脉冲,且所述脉冲的宽度为所述预设时钟周期的2倍;其中,所述片选时钟信号中第一个脉冲的上升沿用于产生所述目标指令信号的上升沿,所述片选时钟信号中第二个脉冲的上升沿用于产生所述目标指令信号的下降沿。

8、在一些实施例中,所述第一时钟信号包括时钟奇信号和时钟偶信号;其中,

9、所述时钟奇信号和所述时钟偶信号的时钟周期均是所述预设时钟周期的2倍,且所述时钟奇信号和所述时钟偶信号之间的相位差为180度。

10、在一些实施例中,所述第一时钟信号包括时钟奇信号和时钟偶信号;其中,

11、所述时钟奇信号和所述时钟偶信号的时钟周期均是所述预设时钟周期的2倍,且所述时钟奇信号和所述时钟偶信号之间的相位差为180度。

12、在一些实施例中,所述信号输入电路包括第一输入电路和第二输入电路;其中,

13、所述第一输入电路,用于接收初始指令信号,输出中间指令信号;以及

14、利用所述时钟奇信号对所述中间指令信号进行采样处理,得到待处理指令奇信号,利用所述时钟偶信号对所述中间指令信号进行采样处理,得到待处理指令偶信号;

15、所述第二输入电路,用于接收初始片选信号,输出中间片选信号;以及

16、利用所述时钟奇信号对所述中间片选信号进行采样处理和反相处理,得到待处理片选奇信号,并利用所述时钟偶信号对所述中间片选信号进行采样处理和反相处理,得到待处理片选偶信号;

17、其中,所述待处理指令奇信号和所述待处理指令偶信号组成所述待处理指令信号,所述待处理片选奇信号和所述待处理片选偶信号组成所述待处理片选信号。

18、在一些实施例中,所述采样逻辑电路包括第一采样电路、第二采样电路、第一逻辑电路和第二逻辑电路;其中,

19、所述第一采样电路,用于利用所述时钟奇信号对所述待处理片选偶信号进行第一级采样处理,得到第一片选采样奇信号;并利用所述时钟奇信号对所述第一片选采样奇信号进行第二级采样处理,得到第二片选采样奇信号;

20、所述第二采样电路,用于利用所述时钟偶信号对所述待处理片选奇信号进行第一级采样处理,得到第一片选采样偶信号;并利用所述时钟偶信号对所述第一片选采样偶信号进行第二级采样处理,得到第二片选采样偶信号;

21、所述第一逻辑电路,用于对所述时钟奇信号、所述第一片选采样奇信号和所述第二片选采样奇信号进行逻辑运算,得到片选时钟奇信号;

22、所述第二逻辑电路,用于对所述时钟偶信号、所述第一片选采样偶信号和所述第二片选采样偶信号进行逻辑运算,得到片选时钟偶信号;

23、其中,所述片选时钟偶信号和所述片选时钟奇信号组成所述片选时钟信号。

24、在一些实施例中,所述第一级采样处理是指上升沿采样处理,所述第二级采样处理是指下降沿采样处理。

25、在一些实施例中,所述第一采样电路包括第一触发器、第一非门和第二触发器;其中,

26、所述第一触发器的输入端与所述待处理片选偶信号连接,所述第一触发器的时钟端与所述时钟奇信号连接,所述第二触发器的输入端与所述第一触发器的输出端连接,所述第一非门的输入端与所述时钟奇信号连接,所述第一非门的输出端与所述第二触发器的时钟端连接,所述第二触发器的输出端用于输出所述第二片选采样奇信号。

27、在一些实施例中,所述第二采样电路包括第三触发器、第二非门和第四触发器;其中,

28、所述第三触发器的输入端与所述待处理片选奇信号连接,所述第三触发器的时钟端与所述时钟偶信号连接,所述第四触发器的输入端与所述第三触发器的输出端连接,所述第二非门的输入端与所述时钟偶信号连接,所述第二非门的输出端与所述第四触发器的时钟端连接,所述第四触发器的输出端用于输出所述第二片选采样偶信号。

29、在一些实施例中,所述第一逻辑电路包括第一或门和第一与门;其中,

30、所述第一或门,用于对所述第一片选采样奇信号和所述第二片选采样奇信号进行或运算,得到中间奇信号;

31、所述第一与门,用于对所述中间奇信号和所述时钟奇信号进行与运算,得到所述片选时钟奇信号。

32、在一些实施例中,所述第二逻辑电路包括第二或门和第二与门;其中,

33、所述第二或门,用于对所述第一片选采样偶信号和所述第二片选采样偶信号进行或运算,得到中间偶信号;

34、所述第二与门,用于对所述中间偶信号和所述时钟偶信号进行与运算,得到所述片选时钟偶信号。

35、在一些实施例中,所述译码电路包括第一指令译码电路、第二指令译码电路以及第三或门;其中,

36、所述第一指令译码电路,用于根据所述待处理片选偶信号和所述片选时钟奇信号对所述待处理指令偶信号进行译码和采样处理,得到指令偶信号;

37、所述第二指令译码电路,用于根据所述待处理片选奇信号和所述片选时钟偶信号对所述待处理指令奇信号进行译码和采样处理,得到指令奇信号;

38、所述第三或门,用于对所述指令偶信号和所述指令奇信号进行或运算,得到所述目标指令信号。

39、在一些实施例中,所述第一指令译码电路包括第一译码电路和第三采样电路;其中,

40、所述第一译码电路,用于对所述待处理指令偶信号和所述待处理片选偶信号进行译码处理,得到指令译码偶信号;

41、所述第三采样电路,用于根据所述片选时钟奇信号对所述指令译码偶信号进行采样处理,得到所述指令偶信号。

42、在一些实施例中,所述第二指令译码电路包括第二译码电路和第四采样电路;其中,

43、所述第二译码电路,用于对所述待处理指令奇信号和所述待处理片选奇信号进行译码处理,得到指令译码奇信号;

44、所述第四采样电路,用于根据所述片选时钟偶信号对所述指令译码奇信号进行采样处理,得到所述指令奇信号。

45、在一些实施例中,所述初始片选信号是表征目标芯片被选中的信号,且所述初始片选信号为低电平有效的脉冲信号;其中,

46、若所述初始片选信号在偶数时钟周期的上升沿采样为低电平,则所述待处理片选偶信号为高电平有效的脉冲信号;以及

47、所述片选时钟奇信号中第一个脉冲的上升沿用于产生所述目标指令信号的上升沿,所述片选时钟奇信号中第二个脉冲的上升沿用于产生所述目标指令信号的下降沿。

48、在一些实施例中,若所述初始片选信号在奇数时钟周期的上升沿采样为低电平,则所述待处理片选奇信号为高电平有效的脉冲信号;以及

49、所述片选时钟偶信号中第一个脉冲的上升沿用于产生所述目标指令信号的上升沿,所述片选时钟偶信号中第二个脉冲的上升沿用于产生所述目标指令信号的下降沿。

50、第二方面,本公开实施例提供了一种半导体存储器,包括如第一方面中任一项所述的信号采样电路。

51、在一些实施例中,该半导体存储器为动态随机存取存储器dram芯片。

52、本公开实施例提供了一种信号采样电路以及半导体存储器,该信号采样电路包括信号输入电路、时钟接收电路、采样逻辑电路和译码电路;其中,信号输入电路,用于确定待处理指令信号和待处理片选信号;时钟接收电路,用于接收初始时钟信号,并对初始时钟信号进行分频处理,得到第一时钟信号;其中,初始时钟信号的时钟周期为预设时钟周期,第一时钟信号的时钟周期为预设时钟周期的2倍;采样逻辑电路,用于根据第一时钟信号对待处理片选信号进行两级采样处理和逻辑运算处理,得到片选时钟信号;其中,片选时钟信号包括两个脉冲,且每个脉冲的宽度为一个预设时钟周期;译码电路,用于根据待处理片选信号和片选时钟信号对待处理指令信号进行译码处理和采样处理,得到目标指令信号。这样,经过该信号采样电路的处理,片选时钟信号包括两个脉冲,且每个脉冲的宽度为一个预设时钟周期,从而译码及采样之后的目标指令信号的脉冲宽度不会跟随工艺、电压、温度等变化产生偏差,改善目标指令信号的脉冲宽度不确定的问题,防止数据失效。

- 还没有人留言评论。精彩留言会获得点赞!