半导体装置及其控制方法与流程

1.本发明涉及一种半导体装置及其控制方法。例如,本发明涉及包括存储器并且具有活动操作模式和功耗低于活动操作模式的待机操作模式的半导体装置及其控制方法。

背景技术:

2.下面列出了公开的技术。

3.[专利文献1]日本专利申请号5,580,751

[0004]

专利文献1公开了包括sram(静态随机存取存储器)作为存储器并且具有低功耗的操作模式的半导体装置。

[0005]

低功耗的操作模式例如是待机操作模式。当具有sram的半导体装置被设置为待机操作模式时,sram也被设置为低功耗的操作模式。在这种情况下,低功耗模式包括例如恢复待机模式(以下也称为rs模式)和待机模式(以下称为sd模式),在恢复待机模式中存储内容被保留,在待机模式中存储内容不被保留以便进一步减少泄漏电流并且它是低功耗的。

技术实现要素:

[0006]

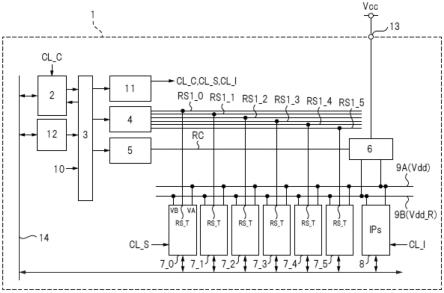

本发明人已经研究了提供有这种sram的半导体装置。首先,将参照附图描述本发明人的研究。图7是示出本发明人在本发明之前讨论的比较半导体装置的配置的框图。另外,图8是示出图7中所示的比较示例的半导体装置的操作的定时图。

[0007]

半导体装置1包括:处理器核心2;低功耗模式控制电路3p;sram控制电路4p;调节器控制电路5p;调节器6;sram 7_0至7_5;以及多个ip核心(知识产权核心)8。虽然没有特别限制,但是sram7_0至7_5的每个存储电容都相对小,例如32k字节。

[0008]

调节器6由调节器控制电路5p控制,从外部电源电压vcc生成内部电源电压vdd并供应给电源线9。sram 7_0至7_5和ip核心8连接到电源线9。sram 7_0至7_5和ip核心8使用电源线9中的内部电源电压vdd作为操作电压来操作。在图7中,作为低功耗模式,sram 7_0至7_5提供有rs模式。即,sram 7_0至7_5分别包括模式端子rs_t。例如通过模式端子rs_t被供应有低电平模式指令信号p_0至p_5,sram 7_0至7_5被设置为rs模式并且被设置为低功耗。通过将模式指令信号p_0至p_5从低电平改变为高电平,sram 7_0至7_5从rs模式转变为正常模式(以下也称为正常模式)。

[0009]

当半导体装置1被设置为待机操作模式时,sram控制电路4p输出低电平模式指令信号p_0至p_5。当半导体装置1从待机操作模式到活动操作模式进行转变时,sram控制电路4p将低电平模式指令信号p_0至p_5变为高电平。因此,sram 7_0至7_5从rs模式转变为正常模式。

[0010]

半导体装置1例如通过生成唤醒事件10而从待机操作模式转变为活动操作模式。

[0011]

响应于唤醒事件10的发生,当sram控制电路4p同时将所有模式指令信号p_0至p_5从低电平改变为高电平时,例如sram 7_0至7_5同时开始操作。因此,电源线9上将流过较大的冲击电流,电源线9中的电位大大降低。这种电位下降会阻止sram 7_0至7_5或ip核心8中

的至少一个正常工作。

[0012]

为了防止sram或ip核心中的至少一个发生故障,本发明人考虑了比较示例的sram控制电路4p将模式指令信号p_0至p_5从低电平依次改变为高电平,如图8中所示。即,当唤醒事件10在时间t0处发生时,在时间t0和时间t1之间的唤醒时间内,sram控制电路4p按照模式指令信号的顺序将模式指令信号从低电平改变为高电平p_0至p_5。因此,抑制了大冲击电流流过电源线9,可以抑制故障。然而,存在着从待机操作模式(sstby)到活动操作模式(actv)的唤醒时间(从sstby的唤醒时间)变长的问题。

[0013]

在图8中,3p_st指示低功耗模式控制电路3p的状态,并且4p_st指示sram控制电路4p的状态。此外,在图8中,sram控制电路4p的状态rs指示sram处于rs模式状态,状态rs释放序列指示sram的rs模式被释放,并且正常(normal)指示srma处于正常模式状态。当然,该模式可以是sd模式而不是rs模式。

[0014]

根据本文描述的一个实施例的半导体装置如下。

[0015]

一种半导体装置,包括:处理器;和连接到处理器的存储器。该半导体装置包括;第一操作模式;功耗低于第一操作模式的第二操作模式。存储器包括第一存储器模式和功耗低于第一存储器模式的第二存储器模式,并且包括多个存储器电路,该多个存储器电路包括第一存储器电路和第二存储器电路。该多个存储器电路分别包括被供应有指定第一存储器模式或第二存储器模式的模式指令信号的模式端子和电源端子。该半导体装置包括;电源线,该电源线连接到多个存储器电路中的每一个的电源端子,并且控制电路在半导体装置从第二操作模式到第一操作模式进行转变的转变时段中将指定第一存储器模式的模式指令信号供应给第一存储器电路的模式端子,并且响应于从第二操作模式到第一操作模式的转变在半导体装置进行到第一操作模式的转变之后,将指定第一存储模式的模式指令信号供应给第二存储器电路的模式端子。

[0016]

根据本说明书和附图的描述,其他目的和新颖特征将变得清楚。

附图说明

[0017]

图1是示出了根据第一实施例的半导体装置的配置的框图。

[0018]

图2是示出了根据第一实施例的lpm控制电路的操作的流程图。

[0019]

图3是示出了根据第一实施例的示例性sram的示意配置的图。

[0020]

图4是示出了在转变时的根据第一实施例的半导体装置的操作的定时图。

[0021]

图5是示出了根据第二实施例的半导体装置的配置的框图。

[0022]

图6是示出了根据第二实施例的半导体装置的操作的定时图。

[0023]

图7是示出了比较半导体装置的配置的图。

[0024]

图8是示出了比较示例的半导体装置的操作的定时图。

具体实施方式

[0025]

下面将参照附图描述本发明的实施例。需要注意的是,本公开仅是示例,并且本领域技术人员可以在保持本发明要点的同时容易地想到适当的变更,这些变更自然也被包括在本发明的范围内。

[0026]

在本说明书和各个附图中,相同的附图标号被指派给与以上参照前面的附图描述

的那些相同的元件,并且可以适当地省略其详细描述。

[0027]

(第一实施例)

[0028]

《半导体装置的结构》

[0029]

图1是示出了根据第一实施例的半导体装置的配置的框图。在图中中,1标示半导体装置。在第一实施例中,包括处理器核心(以下也简称为处理器)和sram的微控制器被例示为半导体装置1,但微控制器不限于此。

[0030]

尽管半导体装置1包括多个电路块,但是为了避免复杂的附图,仅在图中描绘了解释所需的电路块。在图1中,2标示处理器,3标示低功耗模式控制电路(以下也称为lpm控制电路),4标示sram控制电路,5标示调节器控制电路,6标示调节器,7_0至7_5标示sram,并且8标示多个ip核心。11标示时钟控制电路,12标示rs模式跳跃寄存器(以下也称为rs寄存器),13标示外部电源端子,并且14标示内部总线。通过外部电源端子13向半导体装置1提供外部电源电压vcc。半导体装置1内部的电路块将基于外部电源电压vcc形成的内部电源电压vdd或外部电源电压vcc中的至少一者作为电源电压来操作。

[0031]

处理器2、sram 7_0至7_5、ip核心8和rs寄存器12连接到共享内部总线14。处理器2例如在执行程序时经由内部总线14访问sram 7_0至7_5,并向sram 7_0至7_5写入数据或从sram 7_0至7_5读取数据。处理器2还经由内部总线14访问rs寄存器12以向rs寄存器12写入数据或从rs寄存器12读取数据。

[0032]

图1示出了提供六个sram的示例,但是示例不限于该数目。可以在半导体装置1中提供具有大存储电容的单个sram来代替六个sram,但是从可访问性或灵活性的角度来看,提供多个具有小存储电容的sram(例如,32k字节)是优选的。在以下讨论中,存储电容的小sram 7_0至7_5中的每一个被称为存储器电路。而由这些sram 7_0至7_5所配置的存储电容的大sram有时被称为存储器。

[0033]

lpm控制电路3连接到处理器2、rs寄存器12、sram控制电路4、调节器控制电路5和时钟控制电路11。根据来自处理器2的数据和来自rs寄存器12的数据以及唤醒事件10,lpm控制电路3控制sram控制电路4、调节器控制电路5和时钟控制电路11。处理器2由lpm控制电路3控制。

[0034]

sram控制电路4根据来自lpm控制电路3的指令来生成模式指令信号rs1_0到rs1_5,并将它们输出到sram 7_0至7_5的模式端子rs_t,这将在后面描述。调节器控制电路5还根据来自lpm控制电路3的指令来生成调节器控制信号rc并将其供应给调节器6。

[0035]

时钟控制电路11根据来自lpm控制电路3的指令来生成并输出时钟信号cl_c、cl_s、cl_i等。时钟信号cl_c被供应给处理器2,并且处理器2与时钟信号cl_c同步地操作。时钟信号cl_s被供应给sram 7_0至7_5,并且sram 7_0至7_5与时钟信号cl_s同步地操作。时钟信号cl_i被供应给ip核心8,并且ip核心8与时钟信号cl_i同步地操作。

[0036]

调节器6连接到外部电源端子13和电源线9a和9b。调节器6根据调节器控制信号rc通过诸如降压之类的电压变换,而根据外部电源端子13供应的外部电源电压vcc来生成内部电源电压vdd和比内部电源电压vdd更低的内部电源电压vdd_r。并且调节器6将内部电源电压vdd和内部电源电压vdd_r提供给电源线9a和9b。没有特别限制,内部电源电压vdd大约为1.18v,内部电源电压vdd_r大约为1.0v。

[0037]

sram 7_0至7_5具有相同的配置。sram 7_0至7_5分别包括连接到电源线9a的电源

端子va、连接到电源线9b的电源端子vb、提供有模式指令信号的模式端子rs_t、以及提供有时钟信号cl_s的时钟端。顺便提及,在图1中,仅针对sram 7_0,示出了电源端子va、vb和时钟端子,其他sram也以相同的方式包括这些端子。

[0038]

根据第一实施例的半导体装置1包括多个操作模式。接下来,将描述这些操作模式的活动操作模式(actv)和待机操作模式(sstby)。在本说明书中,活动操作模式也被称为第一操作模式,待机操作模式也被称为第二操作模式。

[0039]

《《半导体装置的操作模式1》》

[0040]

活动操作模式是正常操作模式。例如,处理器2执行程序以在活动操作模式中执行预定过程。在此时,处理器2在活动操作模式中访问sram 7_0至7_5。ip核心8还在活动操作模式中操作以执行预定过程。在另一方面,待机操作模式是功耗低于活动操作模式的操作模式。

[0041]

当处理器2指示lpm控制电路3从活动操作模式转变为待机操作模式时,半导体装置1将从活动操作模式转变为待机操作模式。另一方面,当唤醒事件10的生成发生时,lpm控制电路3使半导体装置1从待机操作模式转变为活动操作模式。

[0042]

图2是示出了根据第一实施例的lpm控制电路的操作的流程图。

[0043]

在步骤s0中,假设半导体装置1操作在活动操作模式(actv)中。在步骤s1中,处理器2向lpm控制电路3输出转变到待机操作模式的指令。在步骤s2中,lpm控制电路3控制时钟控制电路11停止时钟信号cl_c、cl_s和cl_i。接下来,在步骤s3中,lpm控制电路3指示sram控制电路4输出模式指令信号rs1_0~rs1_5,以使得sram成为rs模式。此外,在步骤s4中,lpm控制电路3控制调节器控制电路5。调节器控制电路5在lpm控制电路3的控制下,输出调节器控制信号rc,该调节器控制信号rc使调节器6输出较低的内部电源电压vdd_r。

[0044]

结果,在步骤s5中,时钟信号cl_c、cl_s和cl_i停止,并且调节器6输出低的内部电源电压vdd_r。sram 7_0至7_5被转变为rs模式。由于没有时钟信号被供应,处理器2、ip核心8和sram7_0至7_5被停用,并且半导体装置1被设置为低功耗的待机操作模式(sstby)。在此时,sram 7_0至7_5被供应有较低电平的内部电源电压vdd_r,以使得sram保持数据。

[0045]

在待机操作模式中,当唤醒事件10发生时,lpm控制电路3使半导体装置1从待机操作模式转变为活动操作模式。即,在步骤s6中,lpm控制电路3针对调节器控制电路5,并且输出调节器控制信号rc,从而将内部电源电压vdd输出到调节器6。

[0046]

接下来,在步骤s7中,lpm控制电路3指示sram控制电路4输出模式指令信号,以基于来自该rs寄存器12的数据(指定信息)而将该指定信息中未指定的sram从rs模式转变为正常模式。在步骤s8中,lpm控制电路3指示时钟控制电路11输出时钟信号cl_c、cl_s和cl_i。此后,在步骤s9中,lpm控制电路3开始处理器2的操作。

[0047]

因此,在步骤s10中,处理器2与时钟信号cl_c、cl_s和cl_i同步地操作(活动操作模式)。并且sram和ip核心8转变为正常模式,也与时钟信号cl_c、cl_s和cl_i同步地操作(活动操作模式)。

[0048]

注意,在待机操作模式中,当sram转变为上述sd模式而不是rs模式时,在步骤s3中可以将sram 7_0至7_5转变为sd模式,并在步骤s7中将指定信息中未指定的sram从sd模式转变为正常模式。以这种方式,sram的存储数据丢失,但是可以进一步降低数据的功耗。

[0049]

《《sram的配置和模式》》

[0050]

接下来,将描述sram 7_0至7_5的配置和模式(操作模式)。在本说明书中,为了将sram的模式与半导体装置1的操作模式的各个模式区分开来,sram的模式也被称为存储器模式。

[0051]

sram具有正常模式(第一存储器模式)和rs模式(第二存储器模式)作为操作模式(存储器模式)。根据供应给模式端子rs_t的模式指令信号,sram被设置为正常模式或是rs模式。在rs模式中,如上所述,sram在保持数据的同时功耗低于正常模式。当然,本发明不仅限于rs模式。例如,sram还可以包括上述的sd模式(第二存储器模式)。

[0052]

由于sram 7_0至7_5具有彼此相同的配置,所以在这里将sram 7_0作为代表进行描述。图3是示出了根据第一实施例的示例性sram的示意配置的图。sram 7_0包括布置有多个存储器单元的存储器阵列7mc、外围块7ph、缓冲电路7bf和开关7sw1至7sw3。

[0053]

外围块7ph经由开关7sw1连接到电源线7a。存储器阵列7mc还经由开关7sw2连接到电源线7a和7b。外围块7ph和存储器阵列7mc使用从电源线经由开关7sw1和开关7sw2而供应的内部电源电压作为操作电压来操作。在这里,电源线7a经由电源端子va连接到电源线9a(如图1中所示)。并且电源线7b经由电源端子vb连接到电源线9b(如图1中所示)。

[0054]

尽管未示出,外围块7ph包括解码器电路、感测放大器、写入电路等。当经由开关7sw1供应内部电源电压vdd时,解码器电路、感测放大器和写入电路如下操作。即,解码器电路对来自内部总线14的地址信号进行解码。解码器电路根据地址信号选择存储器阵列7mc的存储器单元。感测放大器放大所选择的存储器单元的数据,并经由开关7sw3将放大的数据输出到内部总线14。写入电路将经由开关7sw3从内部总线14提供的数据写入到所选择的存储器单元。

[0055]

缓冲电路7bf连接到模式端子rs_t。并且缓冲电路7bf根据供应给模式端子rs_t的模式指令信号rs1_0来提供选择信号rs_c(如图1中所示)。开关7sw1至7sw3由选择信号rs_c控制。

[0056]

当模式指令信号rs1_0处于高电平以便指定正常模式(第一存储器模式)时,开关7sw1至7sw3的每个公共节点cm连接到节点n0。因此,存储器阵列7mc和外围块7ph以来自电源线9a的内部电源电压vdd作为操作电压来操作。此外,外围块7ph经由开关7sw3电连接到内部总线14。因此,sram 7_0根据例如来自处理器2(如图1中所示)的访问来操作。

[0057]

另一方面,当模式指令信号rs1_0处于低电平以便指定rs模式(第二存储器模式)时,开关7sw1至7sw3的每个公共节点cm连接到节点n1。因此,存储器阵列7mc以来自电源线9b的内部电源电压vdd_r作为操作电压来操作。

[0058]

外围块7ph也经由开关7sw1来与电源线7a电隔离并且连接到高阻抗节点(hi-z)。在此时,开关7sw3将内部总线14连接到预定的内部电压vit而不是外围块7ph。因此,外围块7ph被停用,并且内部总线14被供应有预定的内部电压vit而不是存储器单元的数据。

[0059]

当外围块7ph变为非活动时,不执行对存储器阵列7mc的访问。因此,可以降低sram 7_0中的功耗。由于低的内部电源电压vdd_r被供应给存储器阵列7mc,所以可以在保持数据的同时降低存储器阵列7mc的功耗。

[0060]

例如,当将sd模式设置为sram 7_0时,sram 7_0提供有用于sd模式的模式端子(为方便起见,模式端子sd_t)。开关7sw1至7sw3由供应给模式端子sd_t的模式指令信号控制。在sd模式中,开关7sw1和7sw3将公共节点cm连接到节点n1,并且开关7sw2将公共节点cm连

接到节点n2。因此,存储器阵列7mc和外围块7ph中的每一个变为非活动的,因为它们连接到高阻抗节点(hi-z)。因此,存储器阵列7mc中存储的数据不被保留,但是能够进一步降低功耗。

[0061]

《《rs寄存器》》

[0062]

当半导体装置1从待机操作模式到活动操作模式进行转变时,sram从rs模式转变为正常模式。但是在第一实施例的半导体装置1中,一些sram从rs模式转变为正常模式,而其余sram在从待机操作模式到活动操作模式的转变时段中不从rs模式转变为正常模式。对于未转变为正常模式的sram,在半导体装置1转变为活动操作模式之后,必要的sram从rs模式转变为正常模式。例如,在参考图7和图8描述的比较示例中,在半导体装置1的操作模式的转变时段中,对所有sram执行存储器模式的转变。另一方面,根据第一实施例,在转变时段中,对于半导体装置1的一部分sram,存储器模式的转变被取消。因此,在抑制故障的同时,可以缩短半导体装置1的操作模式的转变时段。

[0063]

根据第一实施例,半导体装置1的rs寄存器12存储指定用于取消从图1中所示的rs模式到正常模式的转变的sram的指定信息。取消转变的sram例如由用户标识,并由处理器2作为指定信息存储在rs寄存器12中。在半导体装置1变为活动操作模式之后sram需要被访问时,取消转变的sram通过使用处理器2来更新存储在rs寄存器12中的指定信息。即,rs寄存器12被更新以从存储在rs寄存器12中的指定信息中排除标识需要被访问的sram的指定信息。

[0064]

当唤醒事件10发生时,lpm控制电路3控制sram控制电路4,以通过模式指令信号将除了由存储在rs寄存器12中的指定信息所指定的sram之外的sram从rs模式转变为正常模式。在半导体装置1转变为活动操作模式之后,lpm控制电路3控制sram控制电路4,以在存储在rs寄存器12中的指定信息被更新时将由通过更新所移除的指定信息所指定的sram从rs模式转变为正常模式。

[0065]

《《转变》》

[0066]

接下来,将描述当转变操作模式时根据第一实施例的半导体装置1的操作。图4是示出了在转变时的根据第一实施例的半导体装置的操作的定时图。在该示例中,在操作模式的转变时段期间,sram 7_0至7_2(第一存储器电路)从rs模式转变为正常模式。此外,sram7_3至7_5(第二存储器电路)不从rs模式转变为正常模式。本节解释了如何取消sram 7_3到7_5中的转变。在半导体装置1转变为活动操作模式之后,本节解释了如何将sram 7_3至7_5从rs模式转变为正常模式。

[0067]

在时间t0处,唤醒事件10发生。因此,lpm控制电路3开始唤醒序列。rs寄存器12包含标识sram 7_3至7_5的指定信息。由于该指定信息被供应给lpm控制电路3,lpm控制电路3指示sram控制电路4将除了sram 7_3至7_5之外的sram 7_0至7_2从rs模式转变为正常模式。响应于该指令,sram控制电路4执行释放sram 7_0至7_2的rs模式的序列(rs模式释放序列)。具体而言,sram控制电路4按照模式指令信号rs1_0、rs1_1、rs1_2的顺序从低电平改变为高电平。

[0068]

在时间t1处,lpm控制电路3结束唤醒序列并开始处理器2的操作。从待机操作模式到活动操作模式的转变时段是从发生唤醒事件10的时间t0到处理器2的操作开始的时间t1。该持续时间也可以被认为是从待机操作模式开始的唤醒时间。

[0069]

图4示出了在转变为活动操作模式的时间t1之后处理器2正在更新存储在rs寄存器12中的指定信息。即,处理器2更新标识sram7_4的指定信息、标识sram 7_3的指定信息、以及标识sram 7_5的指定信息,以从存储在rs寄存器12中的指定信息中排除。响应于该更新,lpm控制电路3指示sram控制电路4在时间t2处将对应于sram 7_4的模式指令信号rs1_4设置为高电平。类似地,lpm控制电路3指示sram控制电路4在时间t3处将sram 7_3的模式指令信号rs1_3设置为高电平。并且lpm控制电路3在时间t4处将sram 7_5的模式指令信号rs1_5指示为高电平。因此,在半导体装置1在时间t1处已经转变为活动操作模式之后,sram 7_3至7_5将从rs模式转变为正常模式。

[0070]

在第一实施例中,六个小存储电容的sram 7_0至7_5被用来存储程序或数据中的至少一个。因此,例如,期望将半导体装置1在活动操作模式中要使用的预定程序或预定数据,存储在在转变时段中从rs模式转变为正常模式的sram(图4中的7_0至7_2)中。结果,当半导体装置1进行到活动操作模式的转变时,可以执行预定程序或者可以执行使用预定数据的过程。

[0071]

另一方面,在从rs模式的转变在转变时段中被取消的sram(图4中的srma7_3至7_5)中,例如期望存储当半导体装置1被设置为活动操作模式时以及时的方式需要的程序或数据中的至少一个。所需的程序或数据由在被需要之前在活动操作模式期间将sram(7_3到7_5)从rs模式转变为正常模式的转变使用。在这种情形中,存储活动操作模式所不需要的程序或数据的sram可以停留在rs模式中。

[0072]

在第一实施例中,如果半导体装置1在时间t4之后要从活动操作模式转变为待机操作模式,则在转变为待机操作模式之前,处理器2将指定取消从rs模式到正常模式的转变的sram的指定信息存储在rs寄存器12中。结果,即使在转变从待机操作模式返回到活动操作模式时,也可以缩短转变时段。存储在rs寄存器12中的指定信息可以始终相同或不同。

[0073]

作为存储在rs寄存器12中的指定信息,作为示例描述取消从rs模式到正常操作模式的转变的sram的指定信息。然而,信息不限于此。例如,在转变时段中,指定要从rs模式转变到正常模式的sram的指定信息可以被存储在rs寄存器12中。

[0074]

尽管已经例示了从rs模式到正常模式的转变,但是它可以是从sd模式到正常模式的转变。在这种情况下,在与rs寄存器12相同的sd寄存器中存储指定用于在转变时段中取消从sd模式转变到正常模式的sram的指定信息。由存储在sd寄存器中的指定信息所指定的sram不在转变时段中从sd模式转变到正常模式,因此它在活动操作模式中进行转变。

[0075]

(第二实施例)

[0076]

图5是示出了根据第二实施例的半导体装置的配置的框图。图6是示出了根据第二实施例的半导体装置的操作的定时图。

[0077]

由于图5类似于图1,所以将解释主要区别。主要区别在于图5的半导体装置1没有rs寄存器12,所以sram控制电路从图1中改变,并且附图标记为15。sram控制电路15输出rs2_0至rs2_5而不是rs1_0至rs1_5作为模式指令信号。

[0078]

与第一实施例类似,lpm控制电路3在唤醒事件10发生时在时间t0处开始唤醒序列。在该序列中,lpm控制电路3使sram控制电路15启动rs模式释放序列。

[0079]

在rs模式释放序列中,sram控制电路15在时刻t0到t1的转变时段将sram 7_0至7_5中的每一个从rs模式转变为正常模式。在转变时段中,sram控制电路15将各模式指令信号

rs2_0至rs2_5从低电平改变为高电平。在此时,sram控制电路15基本上同时改变模式指令信号,以便使来自sram 7_0至7_5的多个sram从rs模式转变为正常模式。

[0080]

具体地,在时间t0_1处,sram控制电路15改变模式指令信号rs2_0以便将一个sram 7_0(第一存储器电路)转变为正常模式。然后在时间t0_2处,sram控制电路15改变模式指令信号rs2_1和rs2_2以使正常模式转变至少两个sram(sram 7_1和sram 7_2:图6中的第二存储器电路)。接下来,在时间t0_3处,sram控制电路15改变模式指令信号rs2_3至rs2_5,以使得至少两个sram(在图6中,三个sram 7_3至7_5:第三存储器电路)转变为正常模式。即,sram控制电路15改变模式指令信号,以使得从rs模式转变为正常模式的sram的数目随时间增加。

[0081]

在第二实施例中,控制多个sram基本上同时从rs模式转变为正常模式。这可以抑制转变时段变长。

[0082]

从电源线9b的电位变化的观点来看,从sram来看,从rs模式转变为正常模式的sram可以被看作是连接到电源线9的寄生电容。当许多sram基本上同时从rs模式转变为正常模式时,连接到电源线9的寄生电容大大增加,从而大的寄生电容连接到电源线。由于这个大的寄生电容的充电与放电,电源线9上的电位将发生很大的变化。在第二实施例中,如图6中所示,从rs模式转变为正常模式的sram的数目首先是一个sram 7_0。在那之后,转变模式的sram数目逐渐增加。因此,连接到电源线9b的寄生电容将随时间依次增加。可以抑制电源线9中的电位变化。结果,可以抑制故障的发生。

[0083]

基本上同时从rs模式转变为正常模式的sram的数目不限于图6中所示的数目。此外,即使多个sram连接到电源线,只要电源线的电位变化是可接受的,首先从rs模式转变为正常模式的sram的数目不限于一。

[0084]

在图5和图6中,对从rs模式向正常模式的转变的情况进行了描述,但是同样也适用于对于从正常模式向rs模式的转变的情况。例如,在正常模式到rs模式的转变中,转变时段可以首先基本上同时转变若干sram,然后转变一个sram。

[0085]

虽然从rs模式转变为正常模式的sram的数目与从正常模式转变为rs模式的sram的数目相同,但是本发明不限于此。此外,作为要经受转变的模式,它可以是上述的sd模式。即,在上述解释中,rs模式可以被替换为sd模式。

[0086]

在第一实施例和第二实施例中,从控制sram 7_0至7_5的观点来看,可以认为lpm控制电路3、sram控制电路4(或15)和调节器控制电路5构成控制电路。

[0087]

此外,在第一实施例中,使sram 7_0至7_2从rs模式转变为正常模式的步骤可以被视为第一转变步骤,并且使sram 7_3至7_5从rs模式转变为正常模式的步骤可以被视为第二转变步骤。

[0088]

此外,在第二实施例中,将sram 7_0至7_5之中的一个sram7_0的模式(从rs模式到正常模式)转变的步骤可以被视为第一步骤。在这种情形中,sram 7_1和7_2可以被视为几乎同时的模式(从rs模式到正常模式)转变的步骤被视为第二步骤,而sram 7_3到7_5几乎同时的模式(从rs模式到正常模式)转变的步骤可以被视为第三步骤。

[0089]

在本说明书中,描述了权利要求中描述的发明以外的多个发明。以下列出了权利要求中未描述的发明的代表性示例。

[0090]

(a)一种半导体装置的控制方法,该半导体装置包括处理器和耦合到该处理器的

多个存储器电路,

[0091]

其中多个存储器电路包括第一存储器模式和功耗低于第一存储器模式的第二存储器模式,以及

[0092]

其中半导体装置包括第一操作模式和功耗低于第一操作模式的第二操作模式,

[0093]

其中控制方法包括以下步骤:

[0094]

(a)在将操作模式在第二存储器模式和第一存储器模式之间转变的转变时段中,将多个存储器电路中的预定存储器电路的操作模式在第一存储器模式和第二存储器模式之间转变,

[0095]

(b)在步骤(a)之后,在转变时段期间,将多个存储器电路中的至少两个存储器电路的操作模式基本上同时在第一操作模式和第二操作模式之间转变。

[0096]

其中步骤(a)是第一转变步骤,并且

[0097]

其中步骤(b)是第二转变步骤。

[0098]

(a-1)根据条款(a)所述的控制方法,还包括:

[0099]

(c)在步骤(b)之后,在转变时段期间,将多个存储器电路中的至少两个存储器电路的操作模式基本上同时在第一操作模式和第二操作模式之间转变,

[0100]

其中步骤(c)是第三转变步骤。

[0101]

(a-2)根据条款(a-1)所述的控制方法,

[0102]

其中在第三步骤中进行模式转变的存储器电路的数目大于在第二步骤中进行模式转变的存储器电路的数目。

[0103]

(b)一种半导体装置,包括:

[0104]

处理器;和

[0105]

连接到处理器的存储器,

[0106]

第一操作模式;和

[0107]

功耗低于第一操作模式的第二操作模式,

[0108]

其中存储器包括第一存储器模式和功耗低于第一存储器模式的第二存储器模式,并且包括多个存储器电路,该多个存储器电路分别包括模式端子和电源端子,模式端子被供应有指定第一存储器模式或第二存储器模式的模式指令信号,

[0109]

其中半导体装置包括;

[0110]

电源线,其连接到多个存储器电路中的每一个的电源端子,以及

[0111]

寄存器,其存储指定取消从第二存储模式到第一存储模式的转变的存储器电路的指定信息、或指定在转变时段期间从第二存储模式转变为第一存储模式的存储器电路的指定信息,以在从第二操作模式转变为第一操作模式之后将半导体装置从第二操作模式转变为第一操作模式。

[0112]

尽管已经基于实施例具体描述了本发明人做出的发明,但是本发明不限于上述实施例,并且更不用说可以进行各种修改而不脱离其主旨。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1