位线读出放大器和存储器设备的制作方法

1.本发明构思涉及一种存储器设备的位线读出放大器。

背景技术:

2.半导体存储器设备被用来存储数据。随机存取存储器(ram)是在没有电的情况下会丢失数据的易失性存储器设备。ram主要用作计算机的主存储器设备。动态随机存取存储器(dram)是易失性的且由存储器单元构成的一种ram。例如,dram对于每个单元使用晶体管和电容器。为了检测存储在dram的存储器单元中的数据,位线和互补位线用预充电电压进行预充电,执行电荷共享操作,并产生位线的电压电平和互补位线的电压电平之间的差。然后,读出放大器接收并放大位线和互补位线之间的电压差,以检测存储在存储器单元中的数据。

3.由于电子工业的最新发展,对更高级的功能、更高的速度和更小尺寸的电子组件的需求越来越大。因此,为了提高半导体存储器设备的集成度,存储器单元区域和外围电路区域的面积已经减少。此外,还已经作出努力来增加处理的数据量,以加快数据处理时间。

技术实现要素:

4.本发明构思的实施例提供了一种减少读出放大器的上层导体的数量以提高由外围电路占据的面积的效率的半导体存储器设备。

5.根据本发明构思的实施例,提供了一种位线读出放大器,包括:放大器,连接在第一读出位线和第二读出位线之间,并响应于第一控制信号和第二控制信号来检测并放大第一位线和第二位线之间的电压差;和均衡器,连接在通过其提供第一控制信号的第一电源线和通过其提供第二控制信号的第二电源线之间,并响应于均衡控制信号来用预充电电压对第一位线和第二位线进行预充电,其中,均衡器包括源端连接到第一电源线的均衡使能晶体管,并响应于均衡控制信号来执行均衡。

6.根据本发明构思的实施例,提供了一种位线读出放大器,包括:均衡使能晶体管,其第一端连接到第一电源线,以响应于均衡控制信号来用预充电电压对第一位线和第二位线进行预充电;第一电源晶体管,响应于第一控制信号来将第一电源电压提供给第一电源线;和放大器,连接在第一读出位线和第二读出位线之间,并响应于第一控制信号和第二控制信号来检测并放大第一位线和第二位线之间的电压差,其中,均衡使能晶体管和第一电源晶体管共享单个有源区域。

7.根据本发明构思的实施例,提供了一种位线读出放大器,包括:均衡器,连接在第一控制信号的第一电源线和第二控制信号的第二电源线之间,响应于第一均衡控制信号来均衡第一控制信号和第二控制信号,并响应于第二均衡控制信号来用预充电电压对第一位线和第二位线进行预充电;放大器,连接在第一读出位线和第二读出位线之间,并响应于第一控制信号和第二控制信号来检测并放大第一位线和第二位线之间的电压差;第一偏移晶体管,响应于偏移控制信号来操作,并连接在第一位线和第二读出位线之间;和第二偏移晶

体管,连接在第二位线和第一读出位线之间,并响应于偏移控制信号来操作,其中,均衡器包括具有一端连接到第一电源线或第二电源线的均衡使能晶体管,并响应于第二均衡控制信号来对第一位线和第二位线执行预充电,并且第二均衡控制信号基于偏移控制信号而在预充电之前使能。

8.根据本发明构思的实施例,提供了一种位线读出放大器,包括:均衡器,连接在第一控制信号的第一电源线和第二控制信号的第二电源线之间,并根据均衡控制信号来用预充电电压对第一位线和第二位线进行预充电;和放大器,连接在第一读出位线和第二读出位线之间,并根据第一控制信号和第二控制信号来检测并放大第一位线和第二位线之间的电压差,其中,均衡器包括具有一端连接到第一电源线或第二电源线的均衡使能晶体管,以执行预充电,并且均衡使能晶体管包括:第一有源区域,包括成对放置以在第一方向上平行延伸的第一区域,以及连接到该对的一端中的每一个并具有矩形形状的第二区域;第一栅极图案,在第一区域上沿第二方向延伸,并被施加均衡控制信号;和第一栅极图案对,在第二区域上沿第一方向平行延伸,并被施加第一控制信号或第二控制信号。

9.根据本发明构思的实施例,提供了一种位线读出放大器,包括:均衡使能晶体管;和放大器,根据第一控制信号和第二控制信号来检测并放大第一位线和第二位线之间的电压差,其中,均衡使能晶体管包括:p型共享有源区域,在基底上包括第一矩形区域、第二矩形区域、以及连接第一矩形区域和第二矩形区域的桥区域;第一控制信号触点,被放置在第一矩形区域上,并被施加第一控制信号;第二控制信号触点,被放置在第二矩形区域上,并被施加第二控制信号;和第一栅极图案,被放置在桥区域上,并被施加均衡控制信号。

附图说明

10.本发明构思的上述和其他特征将通过参考附图详细描述其实施例而变得更加明显,在附图中:

11.图1是示出根据本发明构思的一些实施例的存储器设备的图;

12.图2是示出图1的存储器单元的图;

13.图3是示出应用了根据本发明构思的一些实施例的读出放大器的存储器单元阵列的图;

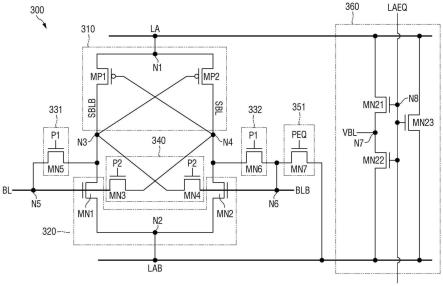

14.图4是示出根据本发明构思的一些实施例的位线读出放大器的电路图;

15.图5是示出根据本发明构思的一些实施例的位线读出放大器的电路图;

16.图6示出图4或图5所示的位线读出放大器的操作时序图;

17.图7是示出根据本发明构思的一些实施例的位线读出放大器的布局的图;

18.图8示出连接到图7所示的位线读出放大器的位线布局;

19.图9是示出根据本发明构思的一些实施例的位线读出放大器的布局的图;

20.图10示出连接到图9所示的位线读出放大器的位线布局;

21.图11是示出根据本发明构思的一些实施例的位线读出放大器的布局的图;

22.图12是示出根据本发明构思的一些实施例的位线读出放大器的布局的图;

23.图13是示出根据本发明构思的一些实施例的位线读出放大器的布局的图;

24.图14示出连接到图12或图13所示的位线读出放大器的位线布局;

25.图15是示出应用了根据本发明构思的一些实施例的读出放大器的存储器单元阵

列的图;

26.图16是示出应用了根据本发明构思的一些实施例的读出放大器的存储器单元阵列的图;以及

27.图17是示出包括根据本发明构思的一些实施例的存储器设备的电子设备的图。

具体实施方式

28.在下文中,本发明构思的实施例将参考附图进行描述。

29.图1是示出根据本发明构思的一些实施例的存储器设备的图。

30.参考图1,存储器设备100可以是基于半导体器件的存储设备。例如,存储器设备100可以是动态随机存取存储器(dram),诸如双倍数据速率静态dram(ddr sdram)、单倍数据速率sdram(sdr sdram)、低功耗ddr sdram(lpddr sdram)、低功耗sdr sdram(lpsdr sdram)和rambus dram(direct rdram(直接rdram))或任何易失性存储器设备。具体地,存储器设备100可以是应用了标准协议(诸如ddr4或ddr5)的设备。

31.作为示例,应用了ddr4或ddr5标准协议的数据引脚的数量可以是四个、八个和十六个,并且根据本发明构思的半导体存储器设备100的数据引脚的数量可以是十六个。在下文中,虽然对本文描述的存储器系统的数据引脚的数量的描述可以根据用于dram的标准协议来应用,但是发明构思不一定局限于此。

32.存储器设备100可以响应于从外部设备(例如,存储器控制器)接收的命令cmd、地址addr和控制信号,通过数据线dq输出数据。存储器设备100包括存储器单元阵列110、命令译码器112、控制逻辑114、地址缓冲器120、行译码器130、列译码器140、读出放大器阵列150和数据输入/输出电路160。

33.存储器单元阵列110包括以布置成行和列的矩阵的形式提供的多个存储器单元。存储器单元阵列110包括连接到存储器单元的多条字线和多条位线bl。多条字线可以连接到存储器单元的行,并且多条位线bl可以连接到存储器单元的列。

34.命令译码器112对从存储器控制器接收的命令(例如,写入使能信号/we、行地址选通信号/ras、列地址选通信号/cas、芯片选择信号/cs等)进行译码。命令cmd可以包括活动(active)命令、读取命令、写入命令、预充电命令等。

35.控制逻辑114可以响应于译码的命令,生成各种控制信号,以对存储器单元阵列110执行访问操作,例如,写入操作、读取操作、预充电操作等。

36.地址缓冲器120从作为外部设备的存储器控制器接收地址addr。地址addr包括寻址存储器单元阵列110的行的行地址ra,以及寻址存储器单元阵列110的列的列地址ca。地址缓冲器120可以将行地址ra发送到行译码器130,并可以将列地址ca发送到列译码器140。

37.行译码器130可以选择连接到存储器单元阵列110的多条字线之一。行译码器130可以对从地址缓冲器120接收的行地址ra进行译码,选择与行地址ra对应的任何一条字线,并激活所选择的字线。在激活字线时,高于电源电压(例如,vdd)的高电源电压(例如,vpp)可以被施加于存储器单元的存取(access)晶体管的栅极上,换句话说,这是字线使能操作。

38.列译码器140可以在存储器单元阵列110的多条位线bl当中选择预定位线。列译码器140可以对从地址缓冲器120接收的列地址ca进行译码,并选择与列地址ca对应的预定位线bl。

39.读出放大器阵列(s/a)150连接到存储器单元阵列110的位线bl。读出放大器阵列150检测多条位线bl当中的所选择的位线的电压改变,并且放大并输出电压改变。数据输入/输出电路160可以通过数据线dq将数据输出到外部,其中,该数据是基于从读出放大器阵列150检测并放大的电压来输出的。任何位线读出放大器blsa可以连接到包括第一位线bl和第二位线blb的位线对,以读出并放大位线上生成的电位。位线读出放大器和位线对之间的具体连接将在下面的图3和图4中描述。

40.读出放大器阵列150可以从控制逻辑114接收隔离信号iso和偏移消除信号oc。读出放大器阵列150可以根据隔离信号iso和偏移消除信号oc来执行偏移消除操作。作为示例,偏移是指构成读出放大器阵列150的半导体元件之间的特性,例如,阈值电压的差。

41.图2是示出图1的存储器单元的图。

42.参考图1和图2,包括在存储器单元阵列中的存储器单元mc连接到字线wl和位线bl中的每一个。

43.存储器单元mc由单元晶体管mtr和单元电容器c构成。存储器设备100可以基于存储在单元电容器c中的电荷量执行读取操作或刷新操作。在这种情况下,连接到存储器单元mc的第一位线bl用预充电电压vpre进行预充电。之后,当连接到存储器单元mc的字线wl激活时,用预充电电压vpre充电的第一位线bl的电荷与存储器单元mc的单元电容器c的电荷共享。由于电荷共享操作,第一位线bl的电压可以从预充电电压vpre减少或增加电压改变量v。读出放大器阵列150中的每个读出放大器可以检测并放大电压改变量v。

44.图3是示出应用了根据本发明构思的一些实施例的读出放大器的存储器单元阵列的图。

45.参考图3,存储器设备200包括多个存储器单元阵列110_1至110_n,以及多个读出放大器150_1至150_n。

46.多个读出放大器150_1至150_n中的每个读出放大器可以包括多个位线读出放大器blsa。位线读出放大器blsa可以被实现为图1至图2所述的读出放大器阵列150。

47.连接到多个存储器单元阵列110_1至110_n的多个位线对bl和blb可以各自连接到多个位线读出放大器blsa。每个位线读出放大器blsa可以是由p型读出放大器和n型读出放大器实现的交叉耦合差分读出放大器。

48.每个位线放大器blsa是在存储器设备200操作时操作的电路元件,并区别于在除了在其中实现位线读出放大器blsa的区域之外的区域中实现的虚设(dummy)读出放大器。

49.根据本发明构思的一些实施例,存储器单元阵列110_1的奇数位线可以连接到第一位线bl,并且偶数位线可以连接到第二位线blb。位线读出放大器150-2可以在两个方向上连接到位线对bl和blb中的每一个。换句话说,位线读出放大器150-2的左端连接到存储器单元阵列110_1的奇数位线,也就是第一位线bl,并且位线读出放大器150-2的右端连接到存储器单元阵列110_2的偶数位线,也就是第二位线blb。

50.当第一位线bl的电位在位线读出放大器blsa的读出操作中为高电位时,第二位线blb的电位变为低电位。另一方面,当第一位线bl的电位在位线读出放大器blsa的读出操作中为低电位时,第二位线blb的电位变为高电位。

51.图4是示出根据本发明构思的一些实施例的位线读出放大器的电路图。

52.参考图4,位线读出放大器300包括放大器310和放大器320以及均衡器360。

53.根据本发明构思的一些实施例,放大器310和放大器320连接在提供第一控制信号la的第一电源线(la线,n1)和提供第二控制信号lab的第二电源线(lab线,n2)之间,并且在第一位线bl和第二位线blb之间。位线读出放大器300包括具有一端连接到第一节点n1的p型放大器310和具有一端连接到第二节点n2的n型放大器320。p型放大器310和n型放大器320中的每一个的另一端可以通过第三节点n3和第四节点n4电连接。第三节点n3和第四节点n4也可以分别称为第一交叉耦合节点和第二交叉耦合节点。p型放大器310包括晶体管mp1和晶体管mp2,并且n型放大器320包括晶体管mn1和晶体管mn2。晶体管mp1和晶体管mp2彼此连接,并且晶体管mn1和晶体管mn2通过交叉耦合结构来彼此连接。n型放大器320还连接到第一位线bl和第二位线blb。

54.例如,晶体管mp1连接在第一节点n1和第三节点n3之间,并且晶体管mp1的栅极连接到第四节点n4。晶体管mp2连接在第一节点n1和第四节点n4之间,并且晶体管mp2的栅极连接到第三节点n3。晶体管mn1连接在第二节点n2和第三节点n3之间,并且晶体管mn1的栅极连接到第五节点n5,其中第一位线bl连接到第五节点n5。晶体管mn2连接在第二节点n2和第四节点n4之间,并且晶体管mn2的栅极连接到第六节点n6,其中第二位线blb连接到第六节点n6。

55.根据本发明构思的一些实施例,位线读出放大器300还包括偏移消除电路331和偏移消除电路332。

56.偏移消除电路331和偏移消除电路332执行偏移消除操作,其中,偏移消除操作出现在第一位线bl和第二读出位线sblb之间,或在第二位线blb和第一读出位线sbl之间。偏移消除电路331和偏移消除电路332可以包括第一偏移晶体管mn5和第二偏移晶体管mn6。第一偏移晶体管mn5连接在第五节点n5和第三节点n3之间,以根据偏移控制信号p1来连接或断开第一位线bl和第二读出位线sblb。第二偏移晶体管mn6连接在第六节点n6和第四节点n4之间,以根据偏移控制信号p1来连接或断开第二位线blb和第一读出位线sbl。

57.根据本发明构思的一些实施例,位线读出放大器300还包括隔离电路340。隔离电路340根据隔离控制信号p2,连接或断开第一位线bl和第一读出位线sbl,或者连接或断开第二位线blb和第二读出位线sblb。隔离电路340包括隔离晶体管mn3和隔离晶体管mn4。隔离晶体管mn3连接在第五节点n5和第四节点n4之间,以根据隔离控制信号p2来连接或断开第一位线bl和第一读出位线sbl。隔离晶体管mn4连接在第六节点n6和第三节点n3之间,以根据隔离控制信号p2来连接或断开第二位线blb和第二读出位线sblb。

58.均衡器360连接在第一电源线(la线)和第二电源线(lab线)之间,也就是在第一节点n1和第二节点n2之间,并根据第二均衡控制信号peq来用预充电电压vbl对第一位线bl和第二位线blb进行预充电。均衡器360包括连接在第一节点n1和第七节点n7之间的晶体管mn21、连接在第二节点n2和第七节点n7之间的晶体管mn22、以及连接在第一节点n1和第二节点n2之间的晶体管mn23。晶体管mn21、晶体管mn22和晶体管mn23的每个栅极连接到第八节点n8,第一均衡控制信号laeq被施加于每个栅极,并且预充电电压vbl被提供给第七节点n7。

59.根据本发明构思的一些实施例,均衡器360还包括均衡使能晶体管351。例如,当均衡使能晶体管351是n型晶体管时,均衡使能晶体管351根据第二均衡控制信号peq来连接或断开第二位线blb和第二电源线(lab线),以执行均衡操作。虽然图4示出均衡使能晶体管

351连接在第二位线blb和第二电源线(lab线)之间以对第二位线进行预充电,但是根据另一示例,均衡使能晶体管351还可以连接到第一位线bl,以对第一位线进行预充电。

60.图5是示出根据本发明构思的一些实施例的位线读出放大器的电路图。将省略与图4重复的解释,并且将主要解释不同之处。

61.参考图5,位线读出放大器400还包括放大器410和放大器420以及均衡器460。然而,与图4不同,包括在均衡器460中的均衡使能晶体管435可以被实现为p型晶体管。

62.均衡使能晶体管435连接在第四节点n4和第一节点n1之间,并根据第二均衡控制信号peq来连接或断开第一电源线(la线)和第一读出位线sbl,以执行均衡操作。

63.图6示出图4所示的位线读出放大器400的操作时序图。图6的x轴表示时间,并且y轴表示每个信号的电压电平。

64.位线读出放大器400依次执行预充电操作、偏移消除操作、电荷共享操作、预读出操作和重新存储操作。在下面的描述中,将主要描述预充电操作。

65.参考图4和图6,在执行重新存储操作直到时间t0之后,存储器单元被去激活(例如,wl开始从逻辑高转变到逻辑低),并且当第一均衡控制信号laeq从逻辑低在时间t1改变为逻辑高时,均衡器360和均衡器460的晶体管mn21、晶体管mn22和晶体管mn23导通,并且开始均衡第一控制信号la和第二控制信号lab。此时,第一控制信号la和第二控制信号lab的均衡电压可以在时间t2汇聚(converge)为通过第七节点n7提供的预充电电压vbl。

66.在时间t3和时间t4之间的部分,隔离控制信号p2持续处于维持逻辑高的状态,并且偏移控制信号p1从逻辑低转变到逻辑高。隔离控制信号p2导通晶体管mn3和晶体管mn4,并且偏移控制信号p1导通偏移晶体管mn5和偏移晶体管mn6。第一位线bl的第五节点n5的信号通过第三节点n3输入到晶体管mp2的栅极,并且第二位线blb的第六节点n6的信号通过第四节点n4输入到晶体管mp1的栅极。此外,通过晶体管mn3和晶体管mn4,第三节点n3与第六节点n6相连,并且第四节点n4与第五节点n5相连。因此,通过连接到第一节点n1和第二节点n2中的每个节点的第一控制信号la和第二控制信号lab,第一位线bl和第二位线blb的电压电平逐渐开始转变。

67.当第二均衡信号peq在时间t5变为逻辑高时,晶体管mn7导通,并且第二位线blb用第二电源线(例如,lab线)的均衡电压进行预充电。尽管图6示出第一位线bl和第二位线blb在相同时间点汇聚为预充电电压,但是驱动第一位线bl和第二位线blb的晶体管mp1和晶体管mp2可以在相同时间点汇聚或在不同时间点汇聚,这取决于它们各自的电流驱动能力。

68.在时间t5之后的时间t6,当第一均衡信号laeq首先变为逻辑低并且晶体管mn21、晶体管mn22和晶体管mn23截止,然后隔离控制信号p2变为逻辑低时,晶体管mn3和晶体管mn4截止,以及当第二均衡信号peq也变为逻辑低时,晶体管mn7也截止。因此,第一位线bl和第二位线blb在预充电状态下各自分开,并且在只有偏移控制信号p1处于逻辑高状态的状态下,晶体管mn5和晶体管mn6导通,并执行偏移取消操作oc。

69.当在时间t7偏移控制信号p1变为逻辑低并且字线的电压电平变为逻辑高时,在第二均衡信号peq在时间t7和时间t8之间的部分期间变为逻辑高时,属于该字线的存储器单元经受电荷共享操作。之后,存储器单元mc可以根据存储在电容器c中的电荷量来改变。

70.尽管上面的描述主要是基于图4来提供的,但是假设的是图5也类似地操作。然而,由于均衡使能晶体管mp3是p型的,因此第二均衡控制信号peq可以以与图6所示的相位相反

的相位来操作均衡使能晶体管mp3。图7至图9是示出根据本发明构思的实施例的位线读出放大器的后道工艺(back end of line,beol)布局。将主要描述均衡使能晶体管。作为示例,均衡使能晶体管的源极连接到第一电源线(la线),并且均衡使能晶体管可以包括与提供第一控制信号la的晶体管的有源区域(例如,p型有源图案)共用的有源区域。作为另一示例,均衡使能晶体管的源极可以连接到第二电源线(lab线),并且均衡使能晶体管可以包括与提供第二控制信号lab的晶体管的有源区域(例如,n型有源图案)共用的有源区域。在所示的位线读出放大器150和位线读出放大器150’中,形成均衡使能晶体管的peq区域和用提供第二控制信号的晶体管形成的lab区域共享n型有源区域。然而,由于施加于栅极图案33、栅极图案51和栅极图案52中的每个栅极图案的信号只是不同,因此用于均衡使能晶体管的源极或漏极的独立有源区域的面积可以减少,并且线型图案的数量可以相应减少。换句话说,存储器单元阵列和位线读出放大器阵列可以用整个有效面积进行设计。

71.在下文中,将在图7至图14中描述根据本发明构思的一些实施例的位线读出放大器的布局的实施例。

72.图7是示出根据本发明构思的一些实施例的位线读出放大器的布局的图,并且图8示出连接到图7所示的位线读出放大器的位线布局。

73.参考图7,根据本发明构思的一些实施例,位线读出放大器150包括第一p型有源区域10和第二n型有源区域s。

74.p型有源区域10可以以沿x方向的矩形有源图案被放置在基底上。n型有源区域s可以在基底上沿x方向与p型有源区域10隔开,并且可以以叉(fork)的形式的有源图案被放置。例如,n型有源区域s可以具有音叉形状。

75.用于连接到包括位线bl或互补位线blb的位线金属图案的触点bl_c11和触点bl_c12以及用于连接到第一控制信号la金属图案的触点c_la可以形成在p型有源区域10上。

76.根据本发明构思的一些实施例,n型有源区域s包括:第一区域30,在基底上具有间隔部分并在x方向上平行延伸;第二区域40,具有连接到第一区域30的间隔部分的间隔部分,并且是平行的,并具有比第一区域的宽度更窄的宽度;和第三区域50,连接第二区域的间隔部分。作为示例,第一区域30可以是在y方向上被放置在第二区域40的间隔部分的两端处的有源图案对。第二区域40是在y方向上被放置在第一区域30的间隔部分的两端处的有源图案对,但是可以具有比第一区域30的有源图案的宽度更窄的宽度。第一区域30、第二区域40和第三区域50在z方向上具有不同的横截面,但可以是彼此连接作为共同区域的图案。

77.用于连接到包括位线bl或互补位线blb的位线金属图案的触点g12_1、触点g12_2、触点g21_1、触点g21_2、触点bl_c21和触点bl_c22可以形成在第一区域30上。用于连接到包括位线bl或互补位线blb的位线金属图案的触点bl_c31和触点bl_c32可以形成在第三区域50上。在第三区域50上,用于连接到第二控制信号lab金属图案的触点c_lab可以在y方向上形成在中央区域中(例如,在与触点c_la相同的线上)。

78.根据本发明构思的一些实施例,位线读出放大器可以包括多个栅极图案。例如,位线读出放大器包括第一栅极图案对12、第二栅极图案对51和52、第一栅极图案31,第二栅极图案32、以及第三栅极图案33。

79.第一栅极图案对12在y方向上彼此隔开,同时被放置为在x方向上延伸。在y方向上,第一栅极图案对12之间的间隔距离比第一区域30和第二区域40(其为有源图案)的间隔

部分更宽,并且比第一区域10(其为p型有源区域)的长度更窄。第一控制信号la被提供给第一栅极图案对12。

80.栅极触点g11_1和栅极触点g11_2可以分别形成在第一栅极图案对12上。

81.因此,p型第一区域10、第一栅极图案对12、以及触点bl_c11和触点bl_c12可以分别形成图4的mp1晶体管和mp2晶体管。栅极触点g11_1和栅极触点g11_2可以分别连接到第三节点n3和第四节点n4。

82.第二栅极图案对51和52在y方向上彼此隔开,同时被放置为在x方向上延伸。在y方向上,第二栅极图案对51和52之间的间隔距离与第一栅极图案对12之间的间隔距离相同,并且比第一区域30和第二区域40的间隔部分更宽,但是比p型第一区域10的长度更窄。

83.第一栅极图案31、第二栅极图案32和第三栅极图案33被放置为在n型有源区域s的第一区域30上沿y方向延伸,并被放置为在x方向上以预定距离隔开。第一栅极图案对12以及第二栅极图案对51和52可以被切割成预定长度,以便不与其他栅极图案(例如,第一栅极图案31、第二栅极图案32和第三栅极图案33)连接。

84.例如,隔离控制信号p2可以施加于第一栅极图案31,偏移控制信号p1可以施加于第二栅极图案32,并且第二均衡控制信号peq可以施加于第三栅极图案33。然而,根据其他示例,施加于第一栅极图案31、第二栅极图案32和第三栅极图案33中的每个栅极图案的信号的顺序可以改变。

85.第二栅极图案对51和52可以是相邻位线读出放大器的栅极图案。栅极触点g22_1和栅极触点g22_2可以形成在第二栅极对51和52上,并且栅极触点g22_1和栅极触点g22_2可以分别连接到第三节点n3和第四节点n4。换句话说,第三区域50、第二栅极图案对51和52、以及栅极触点g22_1和栅极触点g22_2可以形成图4的mn1晶体管和mn2晶体管。

86.参考图8,图7所示的触点bl_c11、触点bl_c12、触点g11_1、触点g11_2、触点g12_1、触点g12_2、触点g21_1、触点g21_2、触点bl_c21、触点bl_c22、触点g22_1、触点g22_2、触点bl_c31和触点bl_c32以及控制信号触点c_la和控制信号触点c_lab可以被放置在图8所示的位线金属图案下方的相同位置。

87.因此,由于第一区域30的有源区域施加第二控制信号lab,并且不与用于均衡使能晶体管(peq、150、图4的mn7)的另一有源区域共享,因此peq区域上的位线金属图案的数量可以减少。

88.图9是示出根据本发明构思的一些实施例的位线读出放大器的布局的图,并且图10示出连接到图9所示的位线读出放大器的位线布局。

89.参考图9,在位线读出放大器中,与图7不同,隔离晶体管mn3和隔离晶体管mn4以及均衡使能晶体管可以具有彼此独立的有源区域。图9所示的均衡使能晶体管是n型晶体管,并且可以是图4所示的均衡使能晶体管mn7。

90.例如,位线读出放大器150’可以在基底上包括第一n型有源区域s、p型有源区域60、第二n型有源区域30和第三n型有源区域35。

91.根据本发明构思的一些实施例,有源区域之间在x方向上的间隔距离可以相同或者不同,这取决于栅极图案的形状。根据本发明构思的一些实施例,不同类型(p型、n型)之间的有源区域的x方向上的间隔距离可以大于相同类型之间的有源区域的x方向上的间隔距离。

92.第一n型有源区域s可以划分为第一区域50、第二区域80和第三区域70。第一区域50在x方向上被放置为矩形,并且第二区域80可以是在y方向上具有比第一区域50更窄的长度(也就是宽度)的矩形图案。第三区域70可以在y方向上被放置在有源图案结构对中,其中该有源图案结构对在其间隔部分的两端处沿x方向平行延伸。第一区域50、第二区域80和第三区域70在z方向上具有不同横截面,但可以是彼此连接作为共同区域的图案。

93.触点bl_c11和触点bl_c12可以形成在第一n型有源区域s的第一区域50上。此外,控制信号触点c_la1形成在第一区域50上,并且控制信号la1(例如,lab信号)可以施加在控制信号触点c_la1上。触点blb_c21和触点blb_c22可以形成在第三区域70上。

94.p型有源区域60的一侧(p型有源区域的左边界)在x方向上与第一n型有源区域s的一侧(例如,右边界)隔开,并且p型有源区域60可以在x方向上被放置为矩形结构。可以在p型有源区域60上形成触点blb_c31和触点blb_c32,并且可以形成施加控制信号la2(例如,la信号)的控制信号触点c_la2。

95.第二n型有源区域30在x方向上与p型有源区域60隔开,以面对p型有源区域60的x方向上的一侧(例如,p型有源区域60的左边界),并且可以被放置作为在x方向上平行延伸并在y方向上包括两个间隔部分的有源图案对30。触点c31、触点c32、触点c21和触点bl_co2可以形成在第二n型有源区域30上。换句话说,第二n型有源区域30的触点c21和触点bl_co2连接到位线bl,并可以与栅极图案31一起成为图4的mn3晶体管。

96.第三n型有源区域35的一侧被放置为与第一n型有源区域s的x方向上的一侧(例如,右边界)隔开,并且第三n型有源区域35可以被放置作为在x方向上平行延伸并在y方向上包括间隔部分的有源图案对35。在这种情况下,第二n型有源区域30的间隔部分和第三n型有源区域35的间隔部分在y方向上可以具有相同间隔距离。触点c61、触点c62、触点blb_c41和触点blb_c42可以形成在第三n型有源区域35上。换句话说,第三n型有源区域35的触点blb_c41和触点blb_c42连接到互补位线blb,并可以与栅极图案37一起成为图4的mn4晶体管。

97.位线读出放大器150’可以包括多个有源区域上的多个栅极图案。例如,位线读出放大器150’可以包括第一栅极图案71、第一栅极图案对51和52、第二栅极图案对61和62、第二栅极图案31、以及第三栅极图案37。

98.第一栅极图案71、第二栅极图案31和第三栅极图案37是在y方向上延伸的单个图案,并且第一栅极图案对51和52以及第二栅极图案对61和62可以是在x方向上延伸的栅极图案对。第一栅极图案对51和52以及第二栅极图案对61和62可以被切割成预定长度,以便不与其他栅极图案(例如,第二栅极图案31、第一栅极图案71和第三栅极图案37)连接。

99.第一栅极图案对51和52在y方向上彼此隔开,同时被放置为在x方向上延伸。在y方向上,第一栅极图案对51和52之间的间隔距离比有源图案70的间隔部分更宽,但是比第一n型有源区域s的长度更窄。在第一栅极图案对51和52中的每个栅极图案上可以形成栅极触点c11、栅极触点c12、栅极触点blb_c11和栅极触点blb_c12。

100.第二栅极图案对61和62在y方向上彼此隔开,同时被放置为在x方向上延伸。在y方向上,第二栅极图案对61和62之间的间隔距离与第一栅极图案对51和52之间的间隔距离相同,并且比第二n型有源区域30和第三n型有源区域35的间隔部分更宽,但是比第二n型有源区域30和第三n型有源区域35的长度更窄。在第二栅极图案对61和62中的每个栅极图案上

可以形成栅极触点bl_c21、栅极触点bl_c22、栅极触点c41和栅极触点c42。

101.第一栅极图案71被放置在第三区域70上,以沿y轴延伸,并且第二均衡控制信号peq被施加于第一栅极图案71。第二栅极图案31被放置在第二n型有源区域30上,以沿y轴延伸,并且隔离控制信号p2被施加于第二栅极图案31。第三栅极图案37被放置在第三n型有源区域35上,以沿y轴延伸,并且隔离控制信号p2被施加于第三栅极图案37。

102.参考图10,图9所示的触点c31、触点c32、触点c21、触点bl_co2、触点bl_c21、触点bl_c22、触点bl_c11、触点bl_c12、触点blb_c21、触点blb_c22、触点blb_c31、触点blb_c32、触点blb_c41、触点blb_c42、触点c61和触点c62以及控制信号触点c_la1和控制信号触点c_la2可以被放置在图10所示的位线金属图案下方的相同位置。

103.因此,由于第一n型有源区域s施加第二控制信号lab,并且不与用于均衡使能晶体管(peq、150、图4的mn7)的另外的有源区域共享,因此peq区域上的位线金属图案的数量可以减少。

104.图11是示出根据本发明构思的一些实施例的位线读出放大器的布局的图。

105.参考图11,在位线读出放大器150’中,与图7不同,隔离晶体管mn3和隔离晶体管mn4以及均衡使能晶体管可以具有彼此独立的有源区域。此外,与图9不同,图11所示的均衡使能晶体管是p型晶体管,并且可以是图5所示的均衡使能晶体管mp3。

106.例如,位线读出放大器150'可以在基底上包括p型有源区域s、第一n型有源区域60、第二n型有源区域30和第三n型有源区域35。

107.根据本发明构思的一些实施例,有源区域之间在x方向上的间隔距离可以相同或者不同,这取决于栅极图案的形状。根据本发明构思的一些实施例,不同类型(例如,p型和n型)之间的有源区域的x方向上的间隔距离可以大于相同类型之间的有源区域的x方向上的间隔距离。

108.p型有源区域s可以划分为第一区域50、第二区域80和第三区域70。第一区域50在x方向上被放置为矩形形状,第二区域80可以是在y方向上具有比第一区域50更窄的长度(也就是宽度)的矩形图案。第三区域70可以被放置在有源图案结构对中,其中该有源图案结构对沿x方向平行延伸并且在y方向上具有间隔部分。第一区域50、第二区域80和第三区域70在z方向上具有不同横截面,并且可以是彼此连接作为共同区域的图案。然而,与图9的有源区域s的x方向上的布置顺序(其中,第一区域50、第二区域80和第三区域70从左到右放置)不同,在图11中,第一区域50、第二区域80和第三区域70从右到左布置。

109.第一n型有源区域60的一侧(第一n型有源区域60的右边界)在x方向上与p型有源区域s的一侧(例如,左边界)隔开,并且第一n型有源区域60可以在x方向上被放置为矩形结构。

110.第二n型有源区域30在x方向上与p型有源区域s隔开,以面对p型有源区域s的x方向上的一侧(例如,p型有源区域s的左边界),并且可被放置作为在x方向上平行延伸并且在y方向上具有间隔部分的有源图案对30。

111.第三n型有源区域35的一侧被放置为与p型有源区域s的x方向上的另一侧(例如,右边界)隔开,并且第三n型有源区域35可以被放置为在x方向上平行延伸并且在y方向上具有间隔部分的有源图案对35。在这种情况下,第二n型有源区域30的间隔部分和第三n型有源区域35的间隔部分在y方向上可以具有相同间隔距离。

112.位线读出放大器150’可以包括多个有源区域上的多个栅极图案。例如,位线读出放大器150’可以包括第一栅极图案71、第一栅极图案对51和52、第二栅极图案对61和62、第二栅极图案31和第三栅极图案37。

113.第一栅极图案71、第二栅极图案31和第三栅极图案37是在y方向上延伸的单个图案,并且第一栅极图案对51和52以及第二栅极图案对61和62可以是在x方向上延伸的栅极图案对。第一栅极图案对51和52以及第二栅极图案对61和62可以被切割成预定长度,以便不与其他栅极图案(例如,第二栅极图案31、第一栅极图案71和第三栅极图案37)连接。

114.第一栅极图案对51和52在y方向上彼此隔开,同时被放置为在第一区域50上沿x方向延伸。在y方向上,第一栅极图案对51和52之间的间隔距离比有源图案70的间隔部分更宽,但是比有源图案50的长度更窄。第一控制信号la和第一控制信号la1被提供给第一栅极图案对51和52。

115.第二栅极图案对61和62在y方向上彼此隔开,同时被放置在第一n型有源区域60上,以在x方向上延伸。在y方向上,第二栅极图案对61和62之间的间隔距离与第一栅极图案对51和52之间的间隔距离相同,并且比第二有源图案30和第三有源图案35的间隔部分更宽,但是比有源区域50和有源区域60的长度更窄。第二控制信号lab和第二控制信号la2被提供给第二栅极图案对61和62。

116.第一栅极图案71被放置在第三区域70上,以沿y轴延伸,并且第二均衡控制信号peq被施加于第一栅极图案71。第二栅极图案31被放置在第二n型有源区域30上,以沿y轴延伸,并且隔离控制信号p2被施加于第二栅极图案31。第三栅极图案37被放置在第三n型有源区域35上,以沿y轴延伸,并且隔离控制信号p2被施加于第三栅极图案37。

117.另一方面,虽然图11中没有示出触点,但是图11的实施例可以以与图9的实施例相同的方式实现,并且触点和位线金属线可以相连。

118.图12是示出根据本发明构思的一些实施例的位线读出放大器的布局的图。图13是示出根据本发明构思的一些实施例的位线读出放大器的布局的图。图14示出连接到图12或图13所示的位线读出放大器的位线布局。为了方便解释,由于第二n型有源区域30和第三n型有源区域35对应于图7、图9和图11的有源区域,因此将不提供其描述。

119.参考图12,在位线读出放大器150’中,与图9或图11不同,图4的mp1晶体管和mp2晶体管以及mn4和均衡使能晶体管mp3可以共享单个有源区域。

120.p型共享有源区域su1在从z方向观看时可以划分为la1区域、peq区域和la2区域,但是在z方向上有不同横截面,并且可以是彼此连接作为共同区域的图案。

121.根据本发明构思的一些实施例,la1区域和la2区域可以是在基底上形成为矩形形状的p型有源区域。peq区域可以被实现为在中心处连接矩形la1区域和矩形la2区域的桥形状。例如,peq区域可以被实现为在桥形状的中间具有预定间隔区域的桥对的形式。在这种情况下,桥形状可以被实现为在la1区域和la2区域之间以对角线方式倾斜(tilt),如图12所示。根据本发明构思的另一实施例,桥形状可以被实现为基于栅极图案71的仅在la1区域和la2区域之间沿x-y方向弯曲(或偏斜(slant))的形状,如图13所示。

122.可以在p型共享有源区域su1上形成连接到位线或互补位线的触点blb_c11、触点blb_c12、触点bl_c21和触点bl_c22,并且可以形成施加第一控制信号la1或第二控制信号la2的控制信号触点c_la1和控制信号触点c_la2。

123.位线读出放大器150’可以包括多个有源区域上的多个栅极图案。例如,位线读出放大器150’可以包括第一栅极图案71、第一栅极图案对51和52、以及第二栅极图案对61和62。

124.第一栅极图案71是在y方向上延伸的单个图案,并且第一栅极图案对51和52以及第二栅极图案对61和62可以是在x方向上延伸的栅极图案对。第一栅极图案对51和52以及第二栅极图案对61和62可以被切割成预定长度,以便不与另一栅极图案(例如,第一栅极图案71)连接。

125.第一栅极图案对51和52在y方向上彼此隔开,同时被放置为在x方向上延伸。可以在第一栅极图案对51和52上形成栅极触点c21、栅极触点c23、栅极触点bl_c11和栅极触点bl_c12。

126.第二栅极图案对61和62在y方向上彼此隔开,同时被放置为在x方向上延伸。可以在第二栅极图案对61和62上形成栅极触点blb_c21、栅极触点blb_c22、栅极触点c31和栅极触点c32。

127.第一栅极图案71被放置在p型共享有源区域su1的peq区域上,以沿y轴延伸,并且第二均衡控制信号peq被施加于第一栅极图案71。

128.参考图14,图12或图13所示的触点c11、触点c12、触点c21、触点c23、触点blb_c11、触点blb_c12、触点bl_c11、触点bl_c12、触点blb_c21、触点blb_c22、触点bl_c21、触点bl_c22、触点c31、触点c32、触点c41和触点c42以及控制信号触点c_la1和控制信号触点c_la2可以被放置在图14所示的位线金属图案下方的相同位置。

129.因此,由于p型共享有源区域su1施加第一控制信号la1或第二控制信号la2,并且不与用于均衡使能晶体管(peq、150、图5的mp3)的另外的有源区域共享,因此peq区域上的位线金属图案的数量可以减少。

130.此外,与图9或图11相比,由于la1区域、peq区域和la2区域被实现为单个p型共享有源区域su,因此不需要图9的peq区域和la2区域之间的间隙或者图11的peq区域和la1区域之间的间隙。此外,不需要单独的触点和单独的上层布线来连接不同于mp3晶体管(例如,均衡控制晶体管)的形成在la1区域中的晶体管或形成在la2区域中的晶体管。换句话说,这在存储器单元的布局上具有减少面积的作用,并且可以减少布线量。

131.图15和图16是示意性示出应用了根据本发明构思的一些实施例的位线读出放大器的存储器设备的图。

132.图15和图16是与作为上面图3所述的多个存储器单元阵列110_1至110_n以及多个读出放大器150_1至150_n中的一些的第一存储器单元阵列110_1和第二存储器单元阵列110_2以及位线读出放大器150_2对应的图。每个位线读出放大器150_2可以包括多个位线读出放大器blsa。位线读出放大器blsa可以被实现为图4至图14所述的位线读出放大器。

133.与图3的存储器设备200不同,在图15的存储器设备600中,第二读出放大器150_2a中的两个位线读出放大器blsa被放置为彼此相邻。两个位线读出放大器blsa可以连接到第一位线bl1和第二位线bl2以及第一互补位线blb1和第二互补位线blb2。两个位线读出放大器blsa之一可以检测第一位线对bl1和blb1的电压改变,并且另一个可以检测第二位线对bl2和blb2的电压改变。

134.与图3的存储器设备200不同,在图16的存储器设备700中,第二读出放大器150_2b

中的三个位线读出放大器blsa被放置为彼此相邻。三个位线读出放大器blsa可以连接到第一位线bl1、第二位线bl2和第三位线bl3以及第一互补位线blb1、第二互补位线blb2和第三互补位线blb3。三个位线读出放大器blsa中的每个位线读出放大器可以检测第一位线对(bl1,blb1)、第二位线对(bl2,blb2)和第三位线对(bl3,blb3)中的每一个的电压改变。

135.图15和图16的存储器设备600和存储器设备700可以根据以下趋势被选择地应用:由于根据存储器单元元件的高集成度的设计规则的小型化,单位单元的大小减少。根据本发明构思的实施例,n个位线读出放大器blsa被放置为彼此相邻,并且n个位线读出放大器blsa连接到第一位线bl1至第n位线bln以及第一互补位线blb1至第n互补位线blbn,并且n个位线读出放大器中的每个位线读出放大器可以检测第一位线对(bl1,blb1)至第n位线对(bln,blbn)中的每一个的电压改变。

136.图17是示出包括根据本发明构思的实施例的读出放大器的存储器设备被应用于移动设备的示例的框图。移动设备可以是移动电话或智能电话。

137.参考图17,移动设备1000包括全球移动通信系统(gsm)块1010、近场通信(nfc)收发器1020、输入/输出块1030、应用块1040、存储器1050和显示器1060。在图17中,移动设备1000的组件/块被示为示例。移动设备1000可以包括更多或更少的组件/块。此外,尽管实施例被示为使用gsm技术,但是移动设备1000可以通过使用其他技术(诸如码分多址(cdma))来实现。图17的块将以集成电路的形式实现。可替换地,一些块将以集成电路的形式实现,而其他块将以单独形式实现。

138.gsm块1010连接到天线1011,并可以操作以提供无线电话的操作。gsm块1010内部可以包括接收器和发射器,以执行对应的接收和发送操作。

139.nfc收发器1020可以被配置为通过利用电感耦合进行无线通信来发送和接收nfc信号。nfc收发器1020将nfc信号提供给nfc天线匹配网络系统1021,并且nfc天线匹配网络系统1021可以通过电感耦合发送nfc信号。nfc天线匹配网络系统1021可以接收从其他nfc设备提供的nfc信号,并将所接收的nfc信号提供给nfc收发器1020。

140.应用块1040包括硬件电路(例如,一个或多个处理器),并且可以操作以提供由移动设备1000提供的各种用户应用。用户应用可以包括语音呼叫操作、数据传递、数据交换等。应用块1040可与gsm块1010和/或nfc收发器1020一起操作,以提供gsm块1010和/或nfc收发器1020的操作特性。可替换地,应用块1040可以包括用于移动销售点(point of sales,pos)的程序。这种程序可以提供使用移动电话(也就是智能电话)的信用卡的购买和支付功能。

141.显示器1060可以响应于从应用块1040接收的显示信号来显示图像。图像可以在应用块1040中提供,或者由内置在移动设备1000中的相机生成。显示器1060的内部可以包括用于临时存储像素值的帧缓冲器,并可以由液晶显示器屏幕与相关联的控制电路一起配置。

142.输入/输出块1030向用户提供输入功能,并提供通过应用块1040接收的输出。

143.存储器1050存储将由应用块1040使用的程序(命令)和/或数据,并可以被实现为随机存取存储器(ram)、只读存储器(rom)、快闪存储器等。因此,存储器1050可以包括易失性和非易失性存储元件。例如,存储器1050对应于图1至图16所述的存储器设备100、存储器设备600和存储器设备700。

144.存储器1050可以包括图1至图9所述的位线读出放大器。位线读出放大器包括放大器和均衡器,并且均衡器可以包括具有一端连接到施加第一控制信号la的第一电源线和施加第二控制信号lab的第二电源线之一的均衡使能晶体管,并根据均衡控制信号peq来执行均衡操作。

145.在结束详细描述时,本领域技术人员将理解,在不实质脱离本发明构思的范围的情况下,可以对本文所公开的实施例进行许多变化和修改。因此,所公开的实施例不是为了限制的目的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1