利用具有最小可寻址单元的寻址方式来进行寻址的存储器的制作方法

本发明涉及集成电路存储器,涉及具有存储器与接口之间的数据路径设置的快取的存储器装置,更具体地涉及一种利用具有一最小可寻址单元(minimumaddressable unit)的一寻址方式来进行寻址的存储器。

背景技术:

1、一些类型的高密度存储器(例如包括nand快闪存储器)配置于页面模式操作,这涉及将相对大数据页面从存储器阵列并行移动至页面缓冲器(page buffer),而输入/输出接口可包括更少数量的接脚(pin)。对于上下文,在一些情况下,一个页面可包括16千位元组(kb,kilobyte)序列或更多,而输入/输出接口可包括数据传输的8个接脚。为了促进更高流通量(throughput)和其他操作,快取存储器(cache memory)可设置在页面缓冲器与输入/输出接口之间。使用快取存储器,数据页面可从页面缓冲器快速传输至快取。在页面缓冲器和存储器阵列之间传输下一页面的时间间隔内,输入/输出接口可利用快取的存取来进行操作。

2、在具有页面操作的页面缓冲器和快取的装置实施中,集成电路上的布局(layout)可以是因素。页面缓冲器和快取期望符合多条数据线的间距(pitch),这些数据线提供存储器阵列的数据页面连接。页面缓冲单元和快取单元可包括利用多个晶体管形成的闩锁(latch)或正反器(flip-flop)之类的时钟脉冲存储元件(clocked storage element),因此可能需要比数据线的间距更大的布局间距。在解决此布局问题的一种方法中,页面缓冲器和快取设置于多个列和行,其中各行符合相同于列数的多条数据线的正交间距(orthogonal pitch)。例如,在具有16列的布局中,行连接至16条数据线,存储16位元,并符合16条数据线的正交间距。

3、快取中的列数和每行单元数通常为2的幂次方(power)(例如,8或16),以促进最小可寻址存储单元大小的整数倍数据传输。作为地址的基数2将标识最小可寻址单元的边界,该最小可寻址单元具有最小可寻址单元大小的整数倍数量。最小可寻址存储单元具有对应至存储器支持的最小可寻址大小的尺寸。最小可寻址单元的大小通常为1位元组或8位元。在一些装置中,最小可寻址单元的大小可以是1字元(word)或16位元。如果最小可寻址大小为8位元,它将以二进制表示为1000。因此,基数2地址中的字位组(8位元)边界将始终具有等于0的三个最低有效位元(least significant bit)(即xxxxxx000)。如果最小可寻址大小为16位元,它将以二进制表示为10000。因此,基数2地址中的字元(16位元)边界将始终具有四个等于0的最低有效位元(即xxxxx0000)。其他大小的最小可寻址单元也有可能。快取中的列数可以是最小可寻址单元大小的整数倍,这会导致对页面缓冲器和快取布局的设计限制。

4、然而,页面缓冲器和快取的垂直间距可能很重要。因此,希望提供一种配置,其可减少在具有存储器的集成电路装置中实施页面缓冲器和快取的所需面积。

技术实现思路

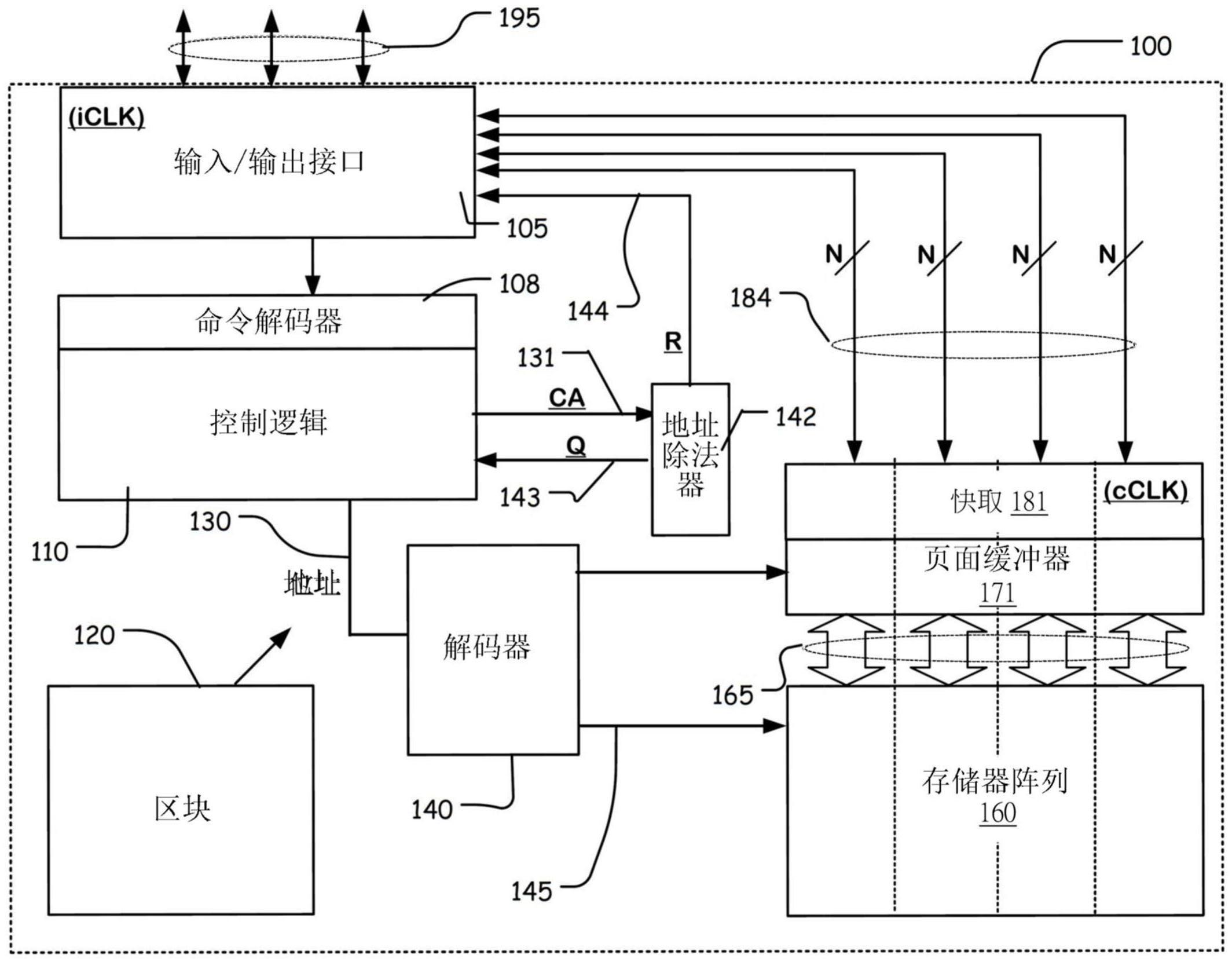

1、本公开描述了一种技术,该技术利用基于最小可寻址单元(minimum addressableunit)(例如,位元组(byte))的寻址方式来提供存储器寻址的数据路径,最小可寻址单元具有2的幂次方(power)大小(例如,8)。数据路径用以利用具有n位元(例如12)的多个传输存储单元(transfer storage unit)在存储器阵列和数据接口之间传输数据,其中n为最小可寻址单元的大小的非整数倍(例如,1.5乘以8,或0.75乘以16)。在本发明所述的实施例中,n非为2的幂次方。通过有效实施页面缓冲器和快取,可支持这种方式配置的数据路径。

2、例如,数据路径可包括用以连接至存储器阵列的页面缓冲器,以及用以连接至页面缓冲器与数据接口的快取。存储器阵列可包括多条数据线,这些数据线用以连接至页面缓冲器,该页面缓冲器设置于x组数据线。快取可包括多组快取单元阵列(cache unitarray),各该多组快取单元阵列用于各该x组数据线。各个快取单元阵列可用以存取页面缓冲器的整数个p位元,并且可包括p个快取单元,该p个快取单元排列成n个快取列(cacherow)和p/n个快取行(cache column)。

3、数据路径可包括耦接至快取的多个电路,用以将各x组快取单元阵列的选定快取单元阵列的选定p/n快取行的n个快取单元连接至一组m条接口线,其中m为n乘以x。数据接口依序(in turn)耦接至m条接口线,并包括在各个接口时钟脉冲周期中以d位元单位(bitunit)进行数据传输的多个电路,其中d为利用二进制寻址方式的最小可寻址单元(例如,8或16)的大小的整数倍。

4、在此数据路径的配置中,m为d和n的公倍数。例如,对于1个位元组(八位元)的最小可寻址单元,d可以是8个接脚且单一数据率端口(single data rate port)状态下、8个接脚、且双倍数据率端口(double data rate port)状态下的16、以及16个接脚且单一数据率端口(single data rate port)状态下的16等,其中单一数据率端口是指每一个时钟脉冲只有传一笔数据。

5、存储器可包括多个地址转换电路,这些地址转换电路回应于输入地址而产生多个选择信号,以控制n个位元传输存储单元所传输的多个数据路径电路。

6、使用如本发明所述的数据路径,基于寻址方式的数据页面可包括具有序列地址(sequential address)的多个最小可寻址单元(例如,位元组(byte))。存储于存储器阵列的数据页面散布于多个存储单元之间的n位元的多个存储单元,这些存储单元对应至快取和页面缓冲器的n位元行(bit column)的大小,这些存储单元耦接至跨x组进行非依序设置的数据线。序列传输存储单元(sequential transfer storage unit)在x组的不同快取单元阵列之间交错(interleave)。

7、本公开描述了一种存储器,该存储器包括存储器阵列,该存储器阵列具有多条数据线,用以存取存储器阵列的多个存储单元。多条数据线包括x组数据线,其中x为大于1的整数。存储器包括数据路径,该数据路径包括页面缓冲器和快取。页面缓冲器用以存取多条数据线。页面缓冲器包括多个页面缓冲单元,各该页面缓冲单元用于每条数据线,并且页面缓冲器可配置于多组页面缓冲单元阵列(page buffer unit array)。快取耦接至页面缓冲器。快取包括一组快取单元阵列,该组快取单元阵列用于各该x组数据线。各个快取单元阵列用以存取页面缓冲器的整数p个缓冲单元,并包括p个快取单元,该p个快取单元排列成整数n个快取列和p/n个快取行。n并非为2的幂次方,且为最小可寻址单元的大小的非整数倍。多个数据路径电路耦接至快取,用以将各x组快取单元阵列的选定快取单元阵列的一选定p/n快取行的n个快取单元连接至m条接口线,其中m为n乘以x。接口耦接至m条接口线,并包括以d位元单位进行数据传输的电路,其中d为最小可寻址单元的大小的整数倍,并且m为d和n的公倍数。提供多个地址转换电路,回应于标识最小可寻址单元的输入地址,而为这些数据路径电路产生多个选择信号。

8、多个地址转换电路可包括地址除法器(address divider),用以将输入地址除以相同于数量m的因子(factor)f除以最小可寻址单元的大小。地址除法器输出商数(quotient),该商数用于选择快取行以及各该x组快取单元阵列的快取单元阵列。地址除法器输出接口所使用的余数(remainder),用以选择来自m条接口线的d位元单元(bit unit),以在接口上传输。

9、多个地址转换电路可用以产生一系列选择信号,用以通过数据路径电路和接口移动传输存储单元,以支持数据的多个d位元单元的数据页面传输,该数据页面具有接口上的序列地址。

10、本公开描述了数据路径的页面缓冲器和快取配置,其中页面缓冲器和快取由多个单元阵列所组成,这些单元阵列对齐于存储器阵列的相应数据线集合(set ofdata line)。各个单元阵列可包括n个列和y个列。耦接至页面缓冲单元阵列的数据线集合包括n条数据线,这些数据线连接至各y行页面缓冲单元阵列的n个单元。将页面缓冲器连接至存储器阵列的数据线集合具有正交间距(orthogonal pitch)(相邻平行位元线的中心到中心的间距),该正交间距为存储器技术和制造节点的函数,并且对于高密度存储器(high densitymemory),正交间距可以非常小。为了符合可用空间,页面缓冲器和快取中的n个单元必须符合n条位元线的正交间距。这是通过将页面缓冲器和快取中的单元堆叠成行来完成。因此,一行单元阵列的页面缓冲器和快取中的存储元件的正交间距必须等于或小于单元阵列行(column in the unit array)所连接的n个数据线集合的间距。

11、使用小于d的数量n能够实施具有较小区域的快取和页面缓冲器,该区域将用于具有d列的快取和页面缓冲器。

12、本公开所述的技术利用“非二进制”快取配置来支持高效布局和操作高密度存储器。如本发明所述实施的数据路径配置可克服两个不同快取行存储的一个数据字元(wordof data)的存取模式问题。此外,如本发明所述实施的数据路径配置可克服快取支持以及位于不同列的快取和页面缓冲器的不同字元中的相同位元选择的互连设置的问题。此外,如本发明所述实施的数据路径配置提供了如何设置支持存储器阵列的单元阵列布局的问题解决方式,特别是对于非常大的页面大小。

13、通过审阅附图、详细说明和权利要求书,可看出本发明的其他方面和优点。

14、为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合所附图式详细说明如下。

- 还没有人留言评论。精彩留言会获得点赞!