用于放大器输入对保护的方法和系统与流程

1.本公开的实施例大体上涉及半导体装置的领域。更具体地说,本公开的实施例涉及存储器放大器保护电路系统。

背景技术:

2.通常,例如半导体装置、存储器芯片、微处理器芯片、图像芯片等的电子装置可包含一或多个放大器电路,所述放大器电路可为可用作电压产生器(例如产生用于电子装置中的参考电压的产生器)的电路。然而,在实施电压产生器时,电压产生器的准确性(例如,其一致地产生预定或所请求电压电平的能力)与电压产生器的电路系统的保护之间可能存在竞争性目标以确保电压产生器的可靠性。此外,用于电子装置中的电压产生器的传统保护方案通常依赖于外部(全局)路线,此举可增大实施这些电压产生器的大小和复杂性,这可在电子装置的大小持续减小时引起问题。

3.本公开的实施例可针对于上文所阐述的问题中的一或多者。

技术实现要素:

4.根据本技术案的一方面,提供一种存储器装置。所述存储器装置包括:电压产生器,其经配置以产生用于传输到所述存储器装置的至少一个组件的参考电压,其中所述电压产生器包括:第一输入,其接收具有第一电压值的第一信号;第二输入,其接收具有第二电压值的第二信号;第一电路,其经配置以产生第三电压值;以及第二电路,其耦合到所述第一电路以接收所述第三电压值,其中所述第二电路接收所述第一信号和所述第二信号,且经配置以利用所述第三电压值来促进所述第一电压值与所述第二电压值的比较,以产生输出电压。

5.根据本技术案的另一方面,提供一种差分放大器。所述差分放大器包括:第一电路,其经配置以产生具有预定电压电平的输出电压;以及耦合到所述第一电路的第二电路,其中所述第二电路包括:晶体管;第一路径,其耦合到所述晶体管以将所述输出电压传输到所述晶体管的源极;选择器,其经配置以选择性地传输多个所接收信号中的所选信号;第二路径,其耦合到所述第一路径和所述选择器以将所述输出电压作为所述多个所接收信号中的一个所接收信号传输到所述选择器;以及第三路径,其耦合到所述选择器和所述晶体管以在所述多个所接收信号中的所述一个所接收信号由所述选择器选择时将所述一个所接收信号传输到所述晶体管的栅极,其中所述晶体管基于所述晶体管由所述多个所接收信号中的所述一个所接收信号激活而产生具有第二预定电平的第二输出电压。

6.根据本技术案的又一方面,提供一种方法。所述方法包括:在电压产生器处接收具有第一电压电平的第一信号;经由所述电压产生器的第一电路在内部产生具有第二电压电平的第二信号;从包括所述第一信号和所述第二信号的多个信号选择所述第二信号;将所述第二信号传输到所述电压产生器的晶体管的栅极以激活所述晶体管;以及产生具有基于所述第二信号的所述第二电压电平的第三电压电平的输出电压信号。

附图说明

7.图1是说明根据本公开的实施例的存储器装置的某些特征的简化框图;

8.图2是根据本公开的实施例的图1的存储器装置的参考电压产生器的框图。

9.图3是根据本公开的实施例的图2的参考电压产生器的第一实施例的电路图。

10.图4是根据本公开的实施例的图2的参考电压产生器的第二实施例的电路图。

具体实施方式

11.下文将描述一个或多个具体实施例。为了提供这些实施例的简要描述,不会在本说明书中描述实际实施方案的所有特征。应了解,在任何这样的实际实施方案的发展中,如同在任何工程或设计项目中,必须制定许多实施方案特定决策以实现研发者的特定目标,例如与系统相关和企业相关约束条件的一致性,这可从一个实施方案到另一实施方案有所变化。此外,应了解,这种发展努力可能是复杂且耗时的,然而将是从本公开获益的所属领域的技术人员从事的设计、构造和制造的例程。

12.电压产生器(例如,参考电压产生器)用于例如存储器装置的电子装置中以产生具有所选或预定电平的可用电压。然而,暴露于超出特定阈值电平的供电电压或其它输入电压可能造成电压产生器中的劣化和/或故障,这致使所产生的实际电压量不同于其期望值或可能致使电压产生器停止操作。因此,本发明的实施例提供保护和电路系统以在电压产生器操作时保护电压产生器。

13.现转向诸图,图1是说明存储器装置10的某些特征的简化框图。具体地说,图1的框图是说明存储器装置10的某些功能性的功能框图。根据一个实施例,存储器装置10可为随机存取存储器(ram)装置、动态ram(dram)装置、静态ram(sram)装置(包含双数据速率sram装置)、快闪存储器或双数据速率类型四同步动态随机存取存储器(ddr4 sdram)装置或双数据速率类型五同步动态随机存取存储器(ddr5 sdram)装置。

14.存储器装置10可包含数个存储器存储体12。举例来说,存储器存储体12可为ddr4sdram存储器存储体。存储器存储体12可设置在布置于双列直插式存储器模块(dimms)上的一或多个芯片(例如,sdram芯片)上。如将了解,每一dimm可包含数个sdram存储器芯片(例如,x4、x8或x16存储器芯片)。每一sdram存储器芯片可包含一或多个存储器存储体12。存储器装置10表示具有数个存储器存储体12的单个存储器芯片(例如,sdram芯片)的一部分。存储器装置10表示具有数个存储器存储体12的单个存储器芯片(例如,sdram芯片)的一部分。应了解,取决于所使用的总体系统的应用和设计以及存储器的类型,可利用存储器装置10上的存储器存储体12的各种其它配置、组织和大小。

15.存储器装置10可包含命令接口14和输入/输出(i/o)接口16。命令接口14经配置以从例如处理器或控制器的外部装置(未示出)提供多个信号(例如,信号15)。处理器或控制器可将各种信号15提供到存储器装置10以促进待写入到存储器装置10或从存储器装置10读取的数据的传输和接收。

16.如将了解,命令接口14可包含数个电路,例如时钟输入电路18和命令地址输入电路20,以保障信号15的恰当处置。命令接口14可从外部装置接收一或多个时钟信号。通常,双数据速率(ddr)存储器利用系统时钟信号的差分对,在本文中被称为真时钟信号(clk_t)及互补时钟信号(clk_c)。ddr的正时钟边缘指代上升真时钟信号clk_t与下降互补时钟信

号clk_c交叉的点,而负时钟边缘指示下降真时钟信号clk_t的转变及互补时钟信号clk_c的上升。命令(例如读取命令、写入命令等)通常在时钟信号的正边缘上输入,且数据是在正和负时钟边缘两者上传输或接收。

17.时钟输入电路18接收真时钟信号(clk_t)和互补时钟信号(clk_c)且产生内部时钟信号clk。内部时钟信号clk供应到内部时钟产生器30,例如延迟锁定环路(dll)电路。内部时钟产生器30基于所接收的内部时钟信号clk产生相控内部时钟信号lclk。相位控制内部时钟信号lclk供应到例如i/o接口16,并用作用于确定读取数据的输出定时的定时信号。

18.内部时钟信号clk也可提供到存储器装置10内的各种其它组件,且可用于产生各种额外内部时钟信号。举例来说,内部时钟信号clk可提供到命令解码器32。命令解码器32可从命令总线34接收命令信号且可解码命令信号以提供各种内部命令。举例来说,命令解码器32可经由总线36将命令信号提供到内部时钟产生器30以协调相位控制内部时钟信号lclk的产生。相位受控内部时钟信号lclk可用于例如通过io接口16钟控数据。

19.此外,命令解码器32可对例如读取命令、写入命令、模式寄存器设定命令、激活命令等命令进行解码,且提供经由总线路径40对对应于命令的特定存储器存储体12的存取。如将了解,存储器装置10可包含各种其它解码器,例如行解码器和列解码器,以促进对存储器存储体12的存取。在一个实施例中,每一存储器存储体12包含存储体控制块22,其提供必要的解码(例如,行解码器和列解码器),以及例如时序控制和数据控制等其它特征,以促进去往和来自存储器存储体12的命令的执行。存储器存储体12和存储体控制块22可被统称为存储器阵列23。

20.存储器装置10基于从例如处理器的外部装置接收的命令/地址信号而执行例如读取命令和写入命令的操作。在一个实施例中,命令/地址总线可为用于适应命令/地址信号(ca)的14位总线。使用时钟信号(clk_t和clk_c)将命令/地址信号时控到命令接口14。所述命令接口可包含命令地址输入电路20,其经配置以通过例如命令解码器32接收和传输命令以提供对存储器存储体12的存取。另外,命令接口14可接收芯片选择信号(cs_n)。cs_n信号使得存储器装置10能够处理传入ca总线上的命令。对存储器装置10内的特定存储体12的存取通过命令编码于ca总线上。另外,命令接口14可经配置以接收多个其它命令信号,且其它存储器类型可使用由命令接口14接收的不同信号。

21.利用上文所论述的命令和计时信号,数据可以发送到存储器装置10并且从存储器装置10发送数据,方法是通过io接口16传输和接收数据信号44。更具体地说,数据可通过包含多个双向数据总线的数据路径46发送到存储器存储体12或从其检索数据。通常被称作dq信号的数据io信号通常在一或多个双向数据总线中传输和接收。对于某些存储器装置,可将io信号划分为高字节和低字节。举例来说,对于x16存储器装置,io信号可划分成对应于例如数据信号的高字节和低字节的高io信号和低io信号。

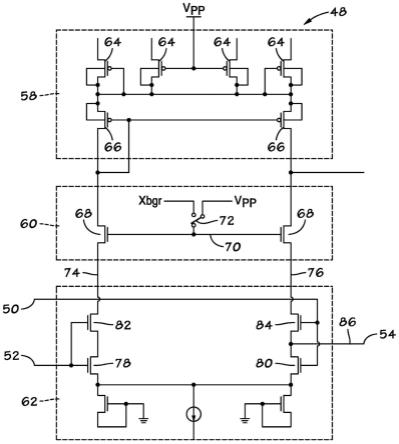

22.另外,为了允许存储器装置10内的较高数据速率,例如ddr存储器装置的某些存储器装置可利用数据选通信号,通常称为dqs信号。dqs信号是由发送数据的外部处理器或控制器(例如,用于写入命令)或由存储器装置10(例如,用于读取命令)驱动。对于读取命令,dqs信号实际上是具有预定模式的额外数据输出(dq)信号。对于写入命令,dqs信号被用作时钟信号以捕获对应的输入数据。如同时钟信号(clk_t和clk_c),可提供数据选通(dqs)信号作为数据选通信号的差分对(dqs_t和dqs_c),以在读取和写入期间提供差分对信令。对

于某些存储器装置,dqs信号的差分对可划分成对应于发送到和来自存储器装置10的数据的高字节和低字节的高数据选通信号和低数据选通信号。

23.也可通过i/o接口16将阻抗(zq)校准信号提供到存储器装置10。可将zq校准信号提供到参考引脚,且用于通过跨越过程、电压和温度(pvt)值的变化调整存储器装置10的上拉和下拉电阻器来调谐输出驱动器和odt值。因为pvt特性可能影响zq电阻器值,所以zq校准信号可提供到zq参考引脚以用于调整电阻而将输入阻抗校准到已知值。如将了解,精密电阻器通常耦合在存储器装置10上的zq引脚与存储器装置10外部的gnd/vss之间。此电阻器充当用于调整内部odt和io引脚的驱动强度的参考。

24.如将了解,例如电力供应电路(用于接收外部vdd和vss信号)、模式寄存器(用以限定可编程操作和配置的各种模式)、读取/写入放大器(用以在读取/写入操作期间放大信号)、温度传感器(用于感测存储器装置10的温度)等各种其它组件也可并入到存储器装置10中。因此,应理解,仅提供图1的框图以突出存储器装置10的某些功能特征以有助于后续详细描述。

25.在一些实施例中,存储器装置10可安置在主机装置中(物理上集成到主机装置中或以其它方式连接到主机装置)或以其它方式耦合到主机装置。主机装置可包含台式计算机、膝上计算机、寻呼机、蜂窝电话、个人管理器、便携式音频播放器、控制电路、相机等中的任一者。主机装置还可是网络节点,例如路由器、服务器或客户端(例如,先前所描述类型的计算机中的一者)。所述主机装置可是某一其它种类的电子装置,例如复印机、扫描仪、打印机、游戏控制台、电视机、机顶盒视频分布或记录系统、电缆盒、个人数字媒体播放器、工厂自动化系统、汽车计算机系统或医疗装置。(用于描述系统的这些各种实例的术语,比如本文中所使用的许多其它术语,可共享一些指代物,并且因此不应当仅仅借助于列出的其它项目来解释。)

26.主机装置因此可是基于处理器的装置,其可包含控制主机中的系统功能和请求的处理的处理器,例如微处理器。此外,任何主机处理器可包括共享系统控制的多个处理器。主机处理器可直接地或间接地耦合到主机的额外系统元件,使得主机处理器通过执行可存储在主机内或在主机外部的指令而控制主机的操作。

27.可结合图1的存储器装置10利用的一个电路为参考电压产生器,其可例如用于从存储器存储体12读出数据。图2说明参考电压产生器48的示意图,所述参考电压产生器可为例如放大器。如所说明,参考电压产生器48可包含输入50(例如,引脚、连接或线)和输入52,借此输入50表示放大器的正端子,且输入52表示放大器的负端子。参考电压产生器48另外包含输出54(例如,引脚、连接等),所述输出操作以输出经放大信号,即在特定电压下的参考电压。另外,说明接收供电电压的供电输入56。

28.在一些实施例中,参考电压产生器48另外包含加载装置58(即,加载电路系统)、保护电路60和差分晶体管对62。加载装置58可操作以接收和调节从供电输入56接收的供电电压。保护电路60可操作以确保提供到差分晶体管对62的电压处于或低于阈值。差分晶体管对62包含将增益施加到在输入50与输入52处接收到的输入信号之间的差的电路系统,所述输入信号可作为来自参考电压产生器48的输出54的所得信号而传输。图3说明用于参考电压产生器48的保护电路60中的电路系统的第一实例。

29.如图3中所说明,加载装置58包含一或多个晶体管64(例如,p沟道金属氧化物半导

体场效应晶体管(mosfet)),其操作以调节所接收电压,例如vpp(例如,可操作为供应用于更改某些非易失性存储器阵列的状态和/或充当程序启用信号(p)的电位和能量的电压供应器的编程功率电压)。另外,两个额外晶体管66(例如,p沟道mosfets)说明为加载装置58的部分。如下文将论述,晶体管66可为具有保护电路60的电路系统的电流镜的部分。

30.如所说明,保护电路60包含一对晶体管68(例如,n沟道mosfets),其各自耦合到晶体管66中的一者。晶体管68中的每一者的栅极耦合到(共同)路径70。此路径70经由开关72耦合到至少两个电压源中的一者。如所说明,开关72操作以选择至少两个电压源中的一者以将所述对应电压提供到晶体管68的栅极。在一个实施例中,第一电压源为带隙参考电压(vbgr),其可表示独立于过程变化、温度变化和电压变化的电压源。如另外说明,图3中所说明的第二电压源为vpp。此外,晶体管68各自耦合到晶体管66中的一者以实现电流镜,使得在路径74和76中的每一者上供应到差分晶体管对的电流具有共同值。

31.如另外在图3中所说明,差分晶体管对62包含晶体管78和晶体管80(例如,n沟道mosfets)作为晶体管的差分对以及晶体管82和晶体管84(例如,n沟道mosfets)作为晶体管的输入对。如所说明,晶体管78和82中的每一者的栅极耦合到输入50(例如,参考电压产生器48的正端子)。同样,晶体管80和84中的每一者的栅极耦合到输入52(例如,参考电压产生器48的负端子)。此配置允许放大输入50与输入52处的电压差,所述电压可沿着路径86输出到输出54。

32.在一些实施例中,沿着路径74和76中的每一者供应的电压应处于或低于预设值,以便保护晶体管78、80、82和84且延长差分晶体管对62的寿命。沿着路径74和76中的每一者供应的电压可作为由晶体管78、80、82和84在操作中利用的源电压而操作,例如作为提供到晶体管78、80、82和84的源极的电压(例如,源电压或操作电压),以用于由差分晶体管对62执行的差分放大中。此外,沿着路径74和76中的每一者供应的电压由沿着路径70传输的栅极电压控制。然而,不同存储器装置10对于vbgr和vpp中的每一者具有不同值。

33.举例来说,当存储器装置10为ddr4装置时,vpp为2.5v。当此电压施加到晶体管68的栅极时,在路径74和76处的电压电平为过高电平而无法保护晶体管82和84。同样,当存储器装置10为ddr4装置时,vbgr为1.24v。此电压电平在路径74和76上产生对于恰当操作过低的所得电压(例如,传输到晶体管82和晶体管84的电压致使晶体管82和晶体管84在线性区中操作,从而引起参考电压产生器48的dc增益的损失和放大功能的故障)。

34.缓解上述问题的一种技术将为从参考电压产生器48外部的源供应额外电压到开关72和/或用从参考电压产生器48外部的源接收的源电压替换源电压中的一者(vbgr或vpp)。然而,此技术可具有一或多个问题。举例来说,此技术可引起布线中增大的复杂性(归因于供应到参考电压产生器48的额外电压路径)。另外,外部电压源可安置在距参考电压产生器48一定距离处,这可引起与信号路径长度有关的问题(即,在参考电压产生器48处接收的电压可能归因于信号路径传输长度而减小或因其它原因而受影响)。

35.因此,在图4中说明用于在用于由开关72选择的预定电平下在内部产生源电压的第二技术和电路。图4说明参考电压产生器48,其包含加载装置58、保护电路60和差分晶体管对62。如所说明,保护电路60包含开关72,所述开关在操作中时选择至少两个电压源中的一者以将所述对应电压提供到晶体管68的栅极。虽然第一电压源对应于vbgr(在一些实施例中,第一电压源可替代地为vpp),但第二电压源在参考电压产生器48内部产生。更明确地

说,沿着路径88离开加载装置58的电压(例如,vth)传输到晶体管68作为到晶体管66的栅极电压信号,且沿着路径90作为用于由开关72选择的第二电压源。

36.在一些实施例中,可选择加载装置58的电路系统(例如,可经由选择加载装置58的电路系统来调谐电压),使得输出电压(vth)为例如大致1.5v、1.6v、1.7v、大致在1.5v与1.7v之间或另一值。以此方式,举例来说,结合为ddr4装置的存储器装置10,vth经产生(例如,选择,接着经由选择加载装置58的电路系统而以预定电平产生),且经由开关72供应到晶体管68的栅极,且具有小于vpp且大于存储器装置10的vbgr的预定电压电平。可选择用于vth的此预定电平以保护差分晶体管对62免受施加到其上的过高电压的影响,同时防止输入晶体管对82和84在其线性区中操作。以此方式,沿着路径74的电压被箝位(即,经由在保护电路60的晶体管68的栅极上选择性地施加预定电压,沿着路径74的电压将不超出或降到低于某值或值范围)。在一些实施例中,使用保护电路60(包含厚氧化物晶体管作为晶体管68)可允许使用薄n沟道晶体管作为差分晶体管对62中的晶体管78、80、82和84,而不将晶体管78、80、82和84暴露于将伤害或因其它原因损害其操作和/或使用寿命的电压。

37.另外,可利用上文结合差分晶体管对62所描述的保护电路60来实现改进的dc增益,因为可选择沿着路径74(和路径76)传输的电压以致使晶体管78、80、82和84在其饱和区中操作。这可通过确保传输到差分晶体管对62的电压在预定值之间来实现。产生电压以在第一高电压值(高于所述第一高电压值,差分晶体管对62的可靠性将受影响)与第二低电压值(低于所述第二低电压值,晶体管78、80、82和84将在其线性区中操作)之间。每一参考电压产生器48可将这两个限值建立为设定点,且可产生施加到晶体管68的栅极的电压以得到沿着路径74的在预定限值之间的电压。

38.虽然本公开可出现各种修改和替代形式,但具体实施例已在附图中通过举例方式展示且在本文中详细描述。然而,应理解,本公开并不希望限于所公开的特定形式。实际上,本公开意图涵盖属于如由所附权利要求书限定的本公开的精神和范围内的所有修改、等效物和替代方案。

39.本文中呈现且要求的技术经参考且应用于具有实践性质的实质对象和具体实例,所述实质对象和具体实例以可论证方式改进本技术领域且因此不是抽象的、无形的或纯理论的。另外,如果随附于本说明书的末尾的任何权利要求项含有表示为“用于执行功能的构件

……”

或“用于执行功能的步骤

……”

的一或多个要素,则预期将依照35 u.s.c.112(f)解释此类要素。然而,对于含有以任何其它方式指定的元素的任何权利要求项,希望不会将依照35 u.s.c.112(f)解释此类元素。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1