一种相位调整电路、延时锁定电路和存储器的制作方法

本公开涉及半导体存储器,尤其涉及一种相位调整电路、延时锁定电路和存储器。

背景技术:

1、在动态随机存取存储器(dynamic random access memory,dram)中的延迟锁定回路(delay loop lock,dll)中,存在四个相位依次相差90度的时钟路径。然而,这四个时钟路径可能由于相位偏移导致错配问题和噪声问题,从而影响存储器的性能。

技术实现思路

1、本公开提供了一种相位调整电路、延时锁定电路和存储器,通过检测不同时钟信号之间的相位差并对时钟信号进行校正,能够改善时钟信号的相位偏移。

2、本公开的技术方案是这样实现的:

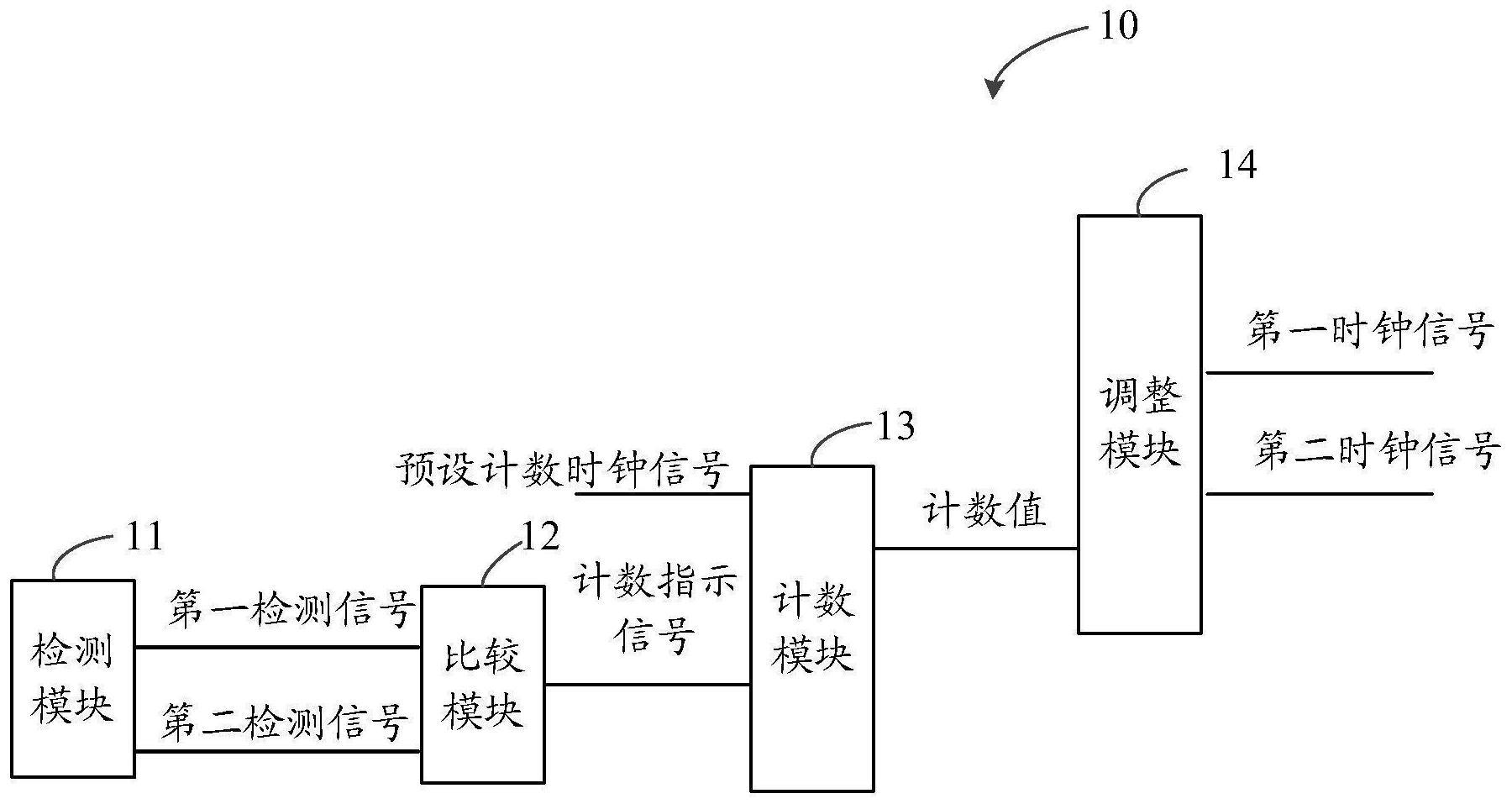

3、第一方面,本公开实施例提供了一种相位调整电路,所述相位调整电路包括依次连接的检测模块、比较模块、计数模块和调整模块;其中,

4、所述检测模块,配置为对第一时钟信号与第二时钟信号之间的相位差进行检测,得到第一检测信号和第二检测信号;

5、所述比较模块,配置为对所述第一检测信号和所述第二检测信号进行占空比比较处理,得到计数指示信号;

6、所述计数模块,配置为基于所述计数指示信号对预设计数时钟信号的脉冲数量进行计数,得到计数值;

7、所述调整模块,配置为根据所述计数值对所述第二时钟信号进行相位调整,以使所述第一时钟信号和所述第二时钟信号之间的相位差为预设值。

8、在一些实施例中,所述检测模块,具体配置为接收所述第一时钟信号、所述第二时钟信号、第三时钟信号和第四时钟信号之中的任意三个信号,根据所接收的信号,输出所述第一检测信号和所述第二检测信号;其中,所述第三时钟信号与所述第一时钟信号的相位差为180度,所述第四时钟信号与所述第二时钟信号的相位差为180度,所述第一检测信号指示所述第一时钟信号的上升沿与所述第二时钟信号的上升沿之间的相位差,所述第二检测信号指示所述第二时钟信号的上升沿与所述第一时钟信号的下降沿之间的相位差。

9、在一些实施例中,所述调整模块,还配置为根据所述计数值对所述第四时钟信号进行相位调整,以使所述第三时钟信号和所述第四时钟信号之间的相位差为预设值。

10、在一些实施例中,所述检测模块包括第一检测单元和第二检测单元;其中,所述第一检测单元,配置为接收所述第一时钟信号和所述第二时钟信号,对所述第一时钟信号和所述第二时钟信号进行逻辑运算,得到所述第一检测信号;所述第二检测单元,配置为接收所述第三时钟信号和所述第二时钟信号,对所述第三时钟信号和所述第二时钟信号进行逻辑运算,得到所述第二检测信号。

11、在一些实施例中,所述第一检测单元包括第一反相器、第一传输门和第一与非门,所述第二检测单元包括第二反相器、第二传输门和第二与非门;所述第一反相器的输入端接收所述第二时钟信号,所述第一传输门的输入端接收所述第一时钟信号,所述第一与非门的两输入端分别与所述第一反相器的输出端和所述第一传输门的输出端连接,所述第一与非门的输出端输出所述第一检测信号;所述第二反相器的输入端接收所述第三时钟信号,所述第二传输门的输入端接收所述第二时钟信号,所述第二与非门的两输入端分别与所述第二反相器的输出端和所述第二传输门的输出端连接,所述第二与非门的输出端输出所述第二检测信号。

12、在一些实施例中,所述相位调整电路应用于存储器,所述比较模块包括占空比单元、预处理单元和采样单元;其中,所述占空比单元,配置为接收所述第一检测信号和所述第二检测信号,对所述第一检测信号和所述第二检测信号进行占空比比较处理,得到比较结果信号;其中,在所述第一检测信号的占空比高于所述第二检测信号时,所述比较结果信号处于第一电平状态;在所述第一检测信号的占空比低于所述第二检测信号时,所述比较结果信号处于第二电平状态;所述预处理单元,配置为接收所述存储器的主时钟信号,对所述主时钟信号进行分频处理,得到采样时钟信号;所述采样单元,配置为接收所述采样时钟信号和所述比较结果信号,基于所述采样时钟信号对所述比较结果信号进行采样,得到所述计数指示信号。

13、在一些实施例中,所述占空比单元包括第一开关管、第二开关管、第三开关管、第四开关管、第一电流源、第二电流源、第三电流源、第四电流源、第一电容、第二电容和运算放大器;其中,所述第一开关管的控制端与所述第二开关管的控制端形成连接点,用于接收所述第一检测信号;所述第一开关管的第一端与所述第一电流源的输出端连接,所述第一电流源的输入端与电源信号连接,所述第二开关管的第二端与所述第二电流源的输入端连接,所述第二电流源的输出端与地信号连接;所述第一开关管的第二端、所述第二开关管的第一端均与所述第一电容的第一端连接,所述第一电容的第二端与地信号连接;所述第三开关管的控制端与所述第四开关管的控制端形成连接点,用于接收所述第二检测信号;所述第三开关管的第一端与所述第三电流源的输出端连接,所述第三电流源的输入端与电源信号连接,所述第四开关管的第二端与所述第四电流源的输入端连接,所述第四电流源的输出端与地信号连接;所述第三开关管的第二端、所述第四开关管的第一端均与所述第二电容的第一端连接,所述第二电容的第二端与地信号连接;所述第一电容的第一端还与所述运算放大器的反相输入端连接,所述第二电容的第一端还与所述运算放大器的正相输入端连接,所述运算放大器的输出端用于输出所述比较结果信号。

14、在一些实施例中,所述预处理单元,还配置为对所述采样时钟信号进行延迟处理,得到所述预设计数时钟信号;所述计数模块,具体配置为在所述计数指示信号处于第一电平状态的情况下,每检测到所述预设计数时钟信号的一个脉冲,对所述计数值进行加一处理;或者,在所述计数指示信号处于第二电平状态的情况下,每检测到所述预设计数时钟信号的一个脉冲,对所述计数值进行减一处理。

15、在一些实施例中,所述调整模块包括第一调整模块和第二调整模块;其中,所述第一调整模块,配置为接收预设固定值和第一原始时钟信号,基于所述预设固定值对所述第一原始时钟信号进行传输处理,得到所述第一时钟信号;所述第二调整模块,配置为接收所述计数值和第二原始时钟信号,基于所述计数值对所述第二原始时钟信号进行传输处理,得到所述第二时钟信号;其中,在所述计数值大于所述预设固定值的情况下,所述第二时钟信号的上升沿相对于所述第一时钟信号的上升沿朝第一方向移动;在所述计数值小于所述预设固定值的情况下,所述第二时钟信号的上升沿相对于所述一时钟信号的上升沿朝第二方向移动。

16、在一些实施例中,所述调整模块还包括第三调整模块、第四调整模块;其中,所述第三调整模块,配置为接收所述预设固定值和第三原始时钟信号,基于所述预设固定值对所述第三原始时钟信号进行传输处理,得到第三时钟信号;所述第三原始时钟信号与所述第一原始时钟信号的相位差为180度;所述第四调整模块,配置为接收所述计数值和第四原始时钟信号,基于所述计数值对所述第四原始时钟信号进行传输处理,得到第四时钟信号;所述第四原始时钟信号与所述第二原始时钟信号的相位差为180度;其中,在所述计数值大于所述预设固定值的情况下,所述第四时钟信号的上升沿相对于所述第三时钟信号的上升沿朝第一方向移动;在所述计数值小于所述预设固定值的情况下,所述第四时钟信号的上升沿相对于所述第三时钟信号的上升沿朝第二方向移动。

17、在一些实施例中,所述第一调整模块、所述第二调整模块、所述第三调整模块和所述第四调整模块中的任意一个均包括预设数量的调整单元,所述预设数量为偶数;所述调整单元,包括多个反相单元,配置为根据所述预设固定值或者所述计数值中相应的一者,确定每一所述反相单元是否接通;以及,利用接通的所述反相单元,对所述第一时钟信号、所述第二时钟信号、所述第三时钟信号和所述第四时钟信号中相应的一者进行反相传输处理;其中,每一所述调整单元中至少存在一个反相单元是接通的;多个所述反相单元的控制端共同形成所述调整单元的控制端,且一个所述反相单元的控制端用于接收所述计数值的其中一位或者所述固定值的其中一位;多个所述反相单元的输入端共同形成所述调整单元的输入端,多个所述反相单元的输出端共同形成所述调整单元的输出端。

18、在一些实施例中,所述预设固定值的位数与所述计数值的位数相同,均为n;所述调整单元包括(n+1)个反相单元,且第1个反相单元固定处于接通状态;若所述调整单元属于所述第一调整模块或者所述第三调整模块,则第(i+1)个反相单元是否接通取决于所述预设固定值的第i位;若所述调整单元属于所述第二调整模块或者所述第四调整模块,则第(i+1)个反相单元是否接通取决于所述计数值的第i位;其中,n为正整数,i是正整数,且i小于或等于n。

19、在一些实施例中,每一所述反相单元均包括第五开关管、第六开关管、第七开关管和第八开关管;所述第五开关管的第一端与电源信号连接,所述第五开关管的第二端与所述第六开关管的第一端连接,所述第七开关管的第二端和所述第八开关管的第一端连接,所述第八开关管的第二端与地信号连接;在第1个所述反相单元中,所述第六开关管的控制端与地信号连接,所述第七开关管的控制端与电源信号连接,以使得第1个反相单元固定处于接通状态;在第(i+1)个所述反相单元中,所述第六开关管的控制端与第i控制信号连接,所述第七开关管的控制端与第i控制信号的反相信号连接,且第i控制信号的电平状态取决于所述计数值或者所述预设固定值中相应一者的第i位,以使得第(i+1)个反相单元是否接通取决于所述计数值或者所述预设固定值中相应一者的第i位;所述第五开关管的控制端与所述第八开关的控制端共同形成所述反相单元的输入端,所述第六开关管的第二端与所述第七开关管的第一端共同形成所述反相单元的输出端。

20、在一些实施例中,所述预设值为90度,第一电平状态为高电平状态,第二电平状态为低电平状态;第一开关管、第三开关管、第五开关管和第六开关管均为p型沟道场效应管,第二开关管、第四开关管、第七开关管和第八开关管均为n型沟道场效应管;所述p型沟道场效应管的控制端为栅极,所述p型沟道场效应管的第一端为源极,所述p型沟道场效应管的第二端为漏极,所述n型沟道场效应管的控制端为栅极,所述n型沟道场效应管的第一端为漏极,所述n型沟道场效应管的第二端为源极。

21、第二方面,本公开实施例提供了一种延时锁定电路,该延时锁定电路用于输出第一时钟信号、第二时钟信号、第三时钟信号和第四时钟信号;所述延时锁定电路至少包括如第一方面所述的相位调整电路;其中,所述延时锁定电路,配置为通过所述相位调整电路对所述第一时钟信号、所述第二时钟信号、所述第三时钟信号和所述第四时钟信号之间的相位差进行校正,以使得所述第一时钟信号、所述第二时钟信号、所述第三时钟信号和所述第四时钟信号之间的相位依次相差90度。

22、第三方面,本公开实施例提供了一种存储器,所述存储器至少包括如第二方面所述的延时锁定电路。

23、本公开实施例提供了一种相位调整电路、延时锁定电路和存储器,相位调整电路包括依次连接的检测模块、比较模块、计数模块和调整模块;其中,检测模块,配置为对第一时钟信号与第二时钟信号之间的相位差进行检测,得到第一检测信号和第二检测信号;比较模块,配置为对第一检测信号和第二检测信号进行占空比比较处理,得到计数指示信号;计数模块,配置为基于计数指示信号对预设计数时钟信号的脉冲数量进行计数,得到计数值;调整模块,配置为根据计数值对第二时钟信号进行相位调整,以使第一时钟信号和第二时钟信号之间的相位差为预设值。这样,通过检测不同时钟信号之间的相位差并对时钟信号进行校正,能够改善时钟信号的相位偏移。

- 还没有人留言评论。精彩留言会获得点赞!